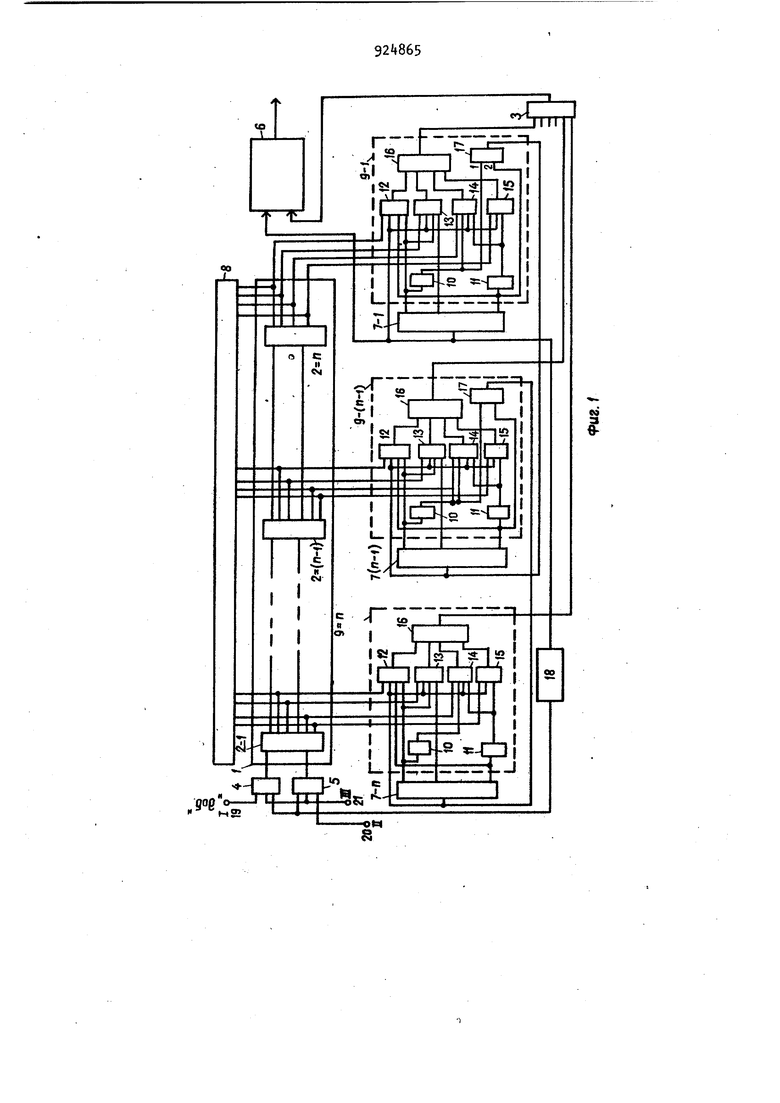

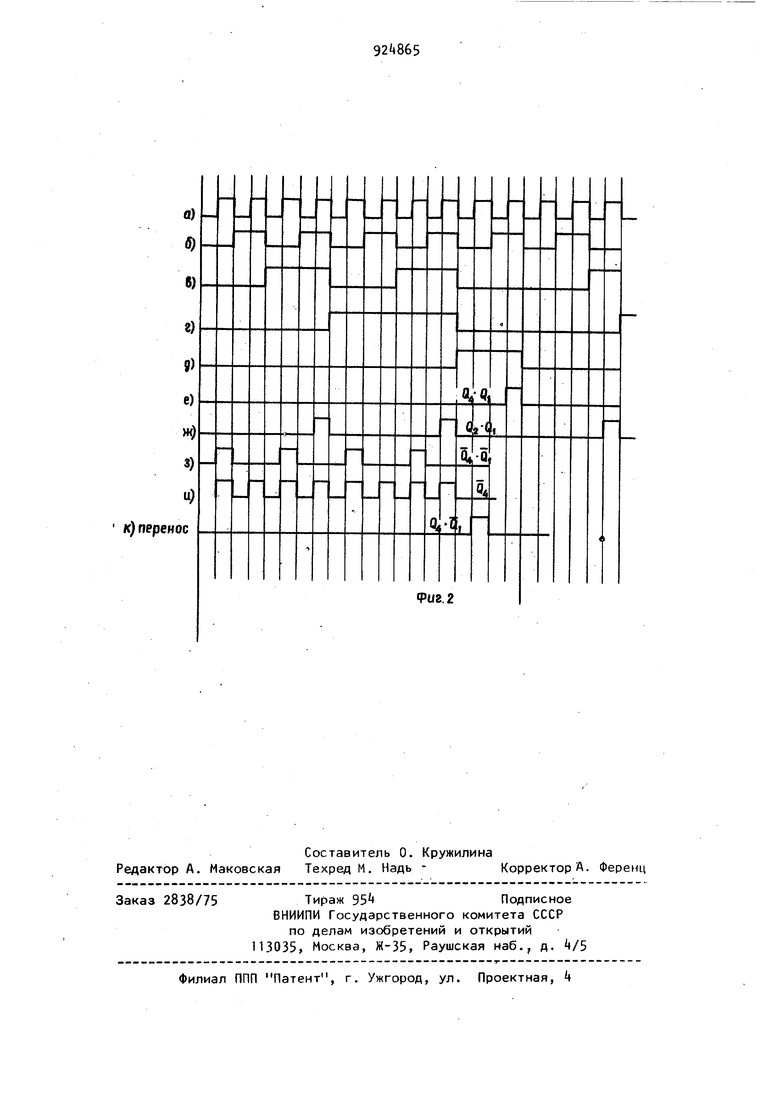

Изобретение относится к автоматике и передаче данных и может быть ис пользовано, например, в различных ра диотехнических устройствах для изменения частоты импульсов. Известен делитель частоты следова ния импульсов, содержащий формирователь импульсов, выход которого соединен через элементы И со входом сче чика и со входом узла установки целы чисел, детектор заполнения, узел задания, а также элементы И Гт, Недостатком устройства является его сложность, которая резко.возрастает, если необходимо обеспечить подстройку частоты в пределах единиц процентов и менее Наиболее близким к предлагаемому является делитель частоты следования импульсов, содержащий блок памяти, каждая группа входов которого соединена с соответствующей группой входов блока индикации информационными входами соответствующих п формирователей группы импульсов, первые входы которых подключены к счетным входам соответствующих п сметчиков импульсов, а первый и второй входы к выходам соответственно первого и второго элементов совпадения, первые входы которых соединены соответствен но с первой и второй входными шинами вторые входы - с третьей входной шиной, а третьи входы - с первым входом формирователя импульсов, выход которого соединен со счетным входом первого счетчика импульсов и первым входом блока коррекции, второй вхрд которого соединен с выходом элемента ИЛИ,каждый из входов которого сое, динен с первым выходом каждого из формирователей группы импульсов, второй выход которого соединен со счетным входомследующего сметчика импульсов . . Недостатком известного устройства являеГся большая флуктуация фазы вы392ХОДНЫХ сигналов и сложность устройства. Цель изобретения - уменьшение флук туации фазы выходных импульсов при одновременном упрощении устройства. Указанная цель достигается тем, что в делителе частоты следования импульсов с регулируемым коэффициентом деления, содержащем блок памяти, каждая группа выходов которого соеди нена с соответствующей группой входов блока индикации и информационными входами соответствующих п формирователей группы импульсов, первые входы которых подключены к сметным входам соответствующих п счетчиков импульсов, а первый и второй входы к выходам соответственно первого и второго элементов совпадения, первые входы которых соединены соответственно с первой и второй входными шинами, вторые входы - с третьей входной шиной, а третьи входы - с первым выходом формирователя импульсов, второй выход которого соединен со счетным входом первого счетчика импульсов и первым входом блока коррек ции, второй вход которого соединен с выходом элемента ИЛИ, каждый из входов которого соединен с первым выходом каждого из формирователей группы импульсов, второй выход которого сое динен со счетным входом следующего счетчика импульсов, первый, второй и третий выходы каждого счетчика импульсов соединены соответственно с вторым, третьим и четвертым входами соответствующих формирователей группы импульсов, каждый из которых содержит, два инвертора, четыре элемента И и элемент ИЛИ, каждый из входов которого соединен с выходом каждого элемента И, первые входы которых сое динены с первым входом формирователя группы импульсов, вторые входы первого и второго элементов И непосредственно и второй вход третьего элемента И через первый инвертор соединены с вторым входом формирователя группы импульсов, третий вход второг элемента И соединен с третьим входом формирователя группы импульсов, третий вход первого элемента И непосредственно и второй вход четвертого элемента И через второй инвертор сое динены с четвертым входом формирователя группы импульсов, а четверть е входы первого, второго и третьего элементов И и третий вход четвертого элемента И соединены с информационными входами формирователя группы импульсов, при этом каждый формирователь группы импульсов, кроме последнего, содержат выходной элемент И, первый вход которого соединен с выходом первого инвертора, второй вход с четвертым входом формирователя группы импульсов, а выход - с вторым выходом формирователя группы импульсов. На фиг. 1 представлена структурная схема устройства; на фиг, 2 временные диаграммы, поясняющие его работу. Устройство содержит блок 1 памяти, включащий в себя разностные счетчики импульсов, элемент 3 ИЛИ, элементы 4 и 5 совпадения, блок 6 коррекции, счетчики импульсов, блок 8 индикации, блоки формирователей группы импульсов, включающие в себя инверторы 10 и 11, элементы 12-15 И, элемент 16 ИЛИ, выходной элемент 17 И, формирователь 18 импульсов. Кроме того, устройство содержит первую, вторую и третью входные шины 19, 20 и 21 соответственно. Устройство работает следующим образом. В исходном состоянии разностные счетчики блока памяти 1 находятся в нулевом состоянии. Сигналом подстройки по шине 20 подготавливаются элементы 4 и 5- При поступлении сигнала добавления на шине 19 открывается элемент Ц, через который импульсы от формирователя 18 начинают поступать на вход блока 1 памяти, увеличивая его содержимое, которое отображается в блоке 8. В блоке 1 записывается число, соответствующее требуемой величине подстройки (при поступлении сигнала вычитания на шину 20 содержимое блока 1 памяти уменьшается до требуемой величины, отображаемой на блоке 8 индикации) . Импульсы тактовой частоты поступают из формирователя 18 на вход первого счетчика (фиг. 2а). На выходах этого счетчика путем деления формируются сигналы (фиг. 2б,в,г,д), поступающие на вход блока 9 1 На выходах элементов И этого блока формируются срответственно один, два, четыре и восемь импульсов при поступлении на вход десятичного счетчика 7 1 десяти импульсов (фиг. 2е ж,з,и).

Импульсы на выходах элементов 121 блока 9 1 (фиг. 2,е,ж,з) не совпадают по фазе, поэтому суммирование их осуществляется непосредственно в элементе 16 ИЛИ. Импульсы на выходе элемента 15 И (фиг. 2а) могут суммироваться только с одним импульсом (фиг. 2е), так как в десятичном виде не может быть числа более Э, поэтому они не совпадают с этим импульсом Импульсы переноса в следующий десятичный счетчик формируются элементом 17 И (фиг. 2к) и не совпадают по фазе с импульсами данного формирования групп импульсов (фиг. 2е-и), поэтому в следующем десятичном счетчике 7 2 и блоке формирователей групп импульсов они не будут совпадать по фазе с импульсами старшего разряда и могут суммироваться в элементе 3 ИЛИ (сотни,десятки, единицы и т.д.). Количество импульсов, формируемых на выходе каждого формирователя групп импульсов, определяется кодом числа, набранного в разностном счетчике 2 данного разряда, выходные сигналы которого открывают соответствующие элементы 12, 13, и 15 И.

Выходной сигнал с элемента 3 ИЛИ поступает в блок 6 коррекции. При этом в зависимости от знака подстройки в последовательность импульсов, поступающих на вход блока коррекции 6 из формирователя 18 импульсов, добавляется или вычитается сформированное элементом 3 ИЛИ количество импульсов, и выходная частота изменяется на требуемое число процентов (долей процента) относительно номинального знамения.

Таким образом, предлагаемое устройство изменяет частоту следования импульсов на заданную (набранную в блоке памяти и отображаемую блоком индикации) величину в процентах к номинальному значению частоты.

В отличие от известных устройств, где пакет импульсов формируется неравномерно, путем пропускания определенного числа импульсов входной час тоты (несколько последовательных импульсов фиг. 2а), а предложенном устройстве формируются более равномерные структуры пакетов импульсов.

При равномерной структуре выходного сигнала уменьшается коэффициент

гармоник (при необходимости формирования синусоидального сигнала - синтезирования частот), уменьшаются краевые искажения при формировании

ч

информационных последовательностей и аппаратуре передачи данных.

При использовании делителя в измерительных устройствах уменьшаются погрешности за счет уменьшения мгновенных отклонений фронтов выходного сигнала делителя.

Формула изобретения

1.Делитель частоты следования импульсов с регулируемым коэффициентом деления, содержащий блок памяти, каждая группа выходов которого соединена с соответствующей группой входов блока индикации и информационным входами соответствующих п формирователей группы импульсов, первые входы которых подключены к счетным входам соответствующих п счетчиков импульсов, а первый и второй входы - к выходам соответственно первого и второго элементов совпадения, первые вхды которых соединены соответственно

с первой и второй входными шинами, вторые входы - с третьей входной шиной, а третьи входы - с первым выходом формирователя импульсов, второй выход которого соединен со счетным входом первого счетчика импульсов и первым входом блока коррекции, второй вход которого соединен с выходом элемента ИЛИ, каждый из входов которого соединен с первым выходом каждого из формирователей группы импульсов, второй выход которого соединен со счетным входом следующего счетчика импульсов, отличающийся тем, что, с целью уменьшения флуктуации фазы выходных импульсов при одновременном упрощении устройства, первый, второй и третий выходы каждого счетчика импульсов соединены соответственно с вторым, третим и четвертым входами соответствующих формирователей группы импульсов.

2.Делитель по п. 1, отличающийся тем, что формирователь группы импульсов содержит два ивертора, четыре элемента И и элемент ИЛИ, каждый-из входов которого соединен с выходом каждого элемента И, первые входы которых соединены с первым входом формирователя группы им7924

пульсов, вторые входы первого и второго элементов И непосредственно и второй вход третьего элемента И через первый инвертор соединены с вторым входом формирователя группы импульсов, третий вход второго элемента И соединен с третьим входом формирователя группы импульсов, третий вход первого элемента И непосредственно и второй вход четвертого элемента И через второй инвертор соединены с четвертым входом формирователя группы импульсов, а четвертые входы первого, второго и третьего элементов И и третий вход четвертого элемента И соединены с информационными входами формирователя группы

8

импульсов, при этом кахадый формирователь группы импульсов, кроме последнего, содержит выходЙЬй элемент И, первый вход которого соединен с выходом первого инвертора, второй вход - с четвертым входом формирователя группы импульсов, а выход - с вторым выходом формирователя группы импульсов.

Источники информации, принятые во внимание при экспертизе

1.Авторское свидетельство СССР № 53803, кл. Н 03 К 23/00, 1973.

2.Авторское свидетельство СССР по заявке V 28661 И/18-21,

кл. Н 03 23/00, 09.01.80.

,

мгг

| название | год | авторы | номер документа |

|---|---|---|---|

| Делитель частоты импульсов | 1980 |

|

SU869053A1 |

| ТАЙМЕР С КОНТРОЛЕМ | 1995 |

|

RU2113007C1 |

| Комбинированное цифровое устройство для измерения интервала времени | 1981 |

|

SU1018098A1 |

| Устройство контроля импульсной последовательности | 1983 |

|

SU1167520A1 |

| Система передачи и приема цифровой информации | 1988 |

|

SU1559361A1 |

| Устройство для измерения частоты сердечных сокращений | 1990 |

|

SU1759401A1 |

| Делитель частоты следования импульсов с переменным коэффициентом деления | 1983 |

|

SU1092730A1 |

| Устройство для сглаживания периодических случайных сигналов | 1983 |

|

SU1242987A2 |

| МНОГОКАНАЛЬНОЕ УСТРОЙСТВО КОНТРОЛЯ ТЕМПЕРАТУРЫ | 2015 |

|

RU2631018C2 |

| Устройство формирования электронного визира для съема координат с экрана электронно-лучевой трубки с растровой разверткой | 1991 |

|

SU1774273A1 |

Авторы

Даты

1982-04-30—Публикация

1980-10-24—Подача