торого подключен к входу разрешения установки третьего счетчика импульсов, а R-входы первого и второго триггеров управления подключены к выходу первого элемента И.

| название | год | авторы | номер документа |

|---|---|---|---|

| Делитель частоты следования импульсов с переменным коэффициентом деления | 1986 |

|

SU1383497A1 |

| Делитель частоты следования импульсовС пЕРЕМЕННыМ КОэффициЕНТОМ дЕлЕНия | 1979 |

|

SU843245A1 |

| Цифровой синтезатор частоты | 1989 |

|

SU1637022A2 |

| Цифровой синтезатор частоты | 1987 |

|

SU1503070A1 |

| Делитель частоты с переменным коэффициентом деления | 1983 |

|

SU1140248A1 |

| Делитель частоты с переменным коэффициентом деления | 1988 |

|

SU1653153A1 |

| Делитель частоты с переменным коэффициентом деления | 1987 |

|

SU1444939A1 |

| Делитель частоты с переменным коэффициентом деления | 1985 |

|

SU1248062A1 |

| Делитель частоты с переменным коэффициентом деления | 1989 |

|

SU1691958A1 |

| Делитель частоты с переменным коэффициентом деления | 1982 |

|

SU1081804A1 |

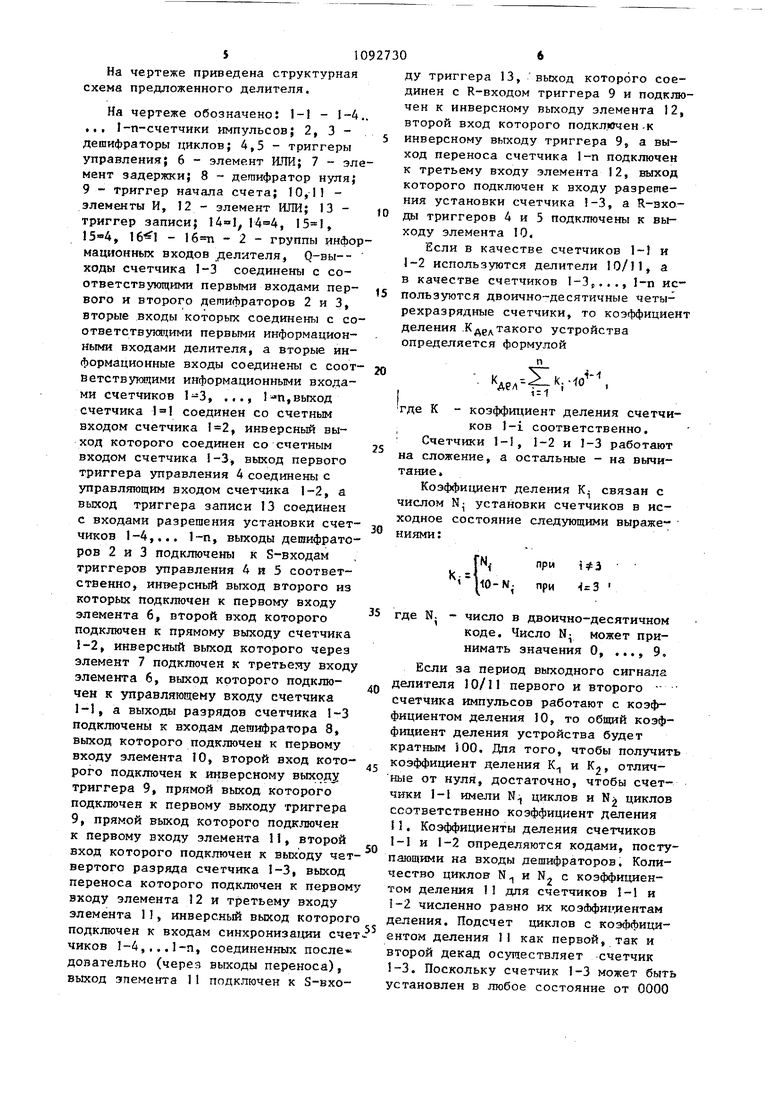

ДЕЛИТЕЛЬ ЧАСТОТЫ СЛЕДОВАНИЯ ИМПУЛЬСОВ С ПЕРЕМЕННЫМ КОЭФФИЦИЕНТОМ ДЕЛЕНИЯ, содержащий две цепи из последовательно соединенных с первого по третий и с третьего по п -и счетчиков импульсов, два триггера управления, триггер записи триггер начала счета, два дешифратора циклов и дешифратор нуля, Q-вькоды третьего счетчика импульсов соединены с соответствукяцими первыми входами первого . и второго дешифраторов циклов, вторые входы которых соединены с соот ветствующими первыми информационными входами делителя, а вторые информационные входы соединены с соответствующими информационными входами с третьего по ti-и счетчиков импульсов, выход первого триггера управления соединен с управляющим входом второго счетчика, импульсов, а выход триггера записи соединен с входами разрешения установки с четвертого по h-fl счетчикой импульсов, отличающийс я тем, что,с целью упрощения и С1гажения потребляемой мощности, в не го введены первый и второй элементы ИЛИ, первый и второй элементы И и элемент задержки, при этом выходы первого Н второго дешифраторов цмхлон подключены к 5-входам соответственно первого и второго триггеров управления, инверсный выход второго триггера управления подключен к первому входу первого элемента ИЛИ, второй вход которого подключен к прямоксу выходу второго счетчика импульсов, инверсный вьгход которого через элемент задержки подключен к третьему входу первого элемента ИЛИ, выход которого подключен к управляющему входу первого счетчика импульсов, а выходы разрядов третьего сЧетчика импульсов подключены к соответствующим входам дешифратора нуля, выход которого подключен к первому входу первого элемента И, второй вход которого подключен к инверсному выходу триггера начата счета, прямой вы- ход которого подключен к первому входу второго элемента И, второй вход которого подключен к выходу четвертого разряда третьего счетчика импульсов., выход переноса которого подключен к первому входу второго элемента ИЛИ и третьему входу второго элемента И, инверсный выход которого подключен к входам синхронизации с четвертого по п-и счетчиков импульсов, выход второго элемента И подкхаочен к 5-входу триггера записи, Р -вход которого соединен с R-входом триггера начала счета и инверсным выходом второго элемента ИЛИ, второй вход которого подключен к инверсному выходу триггера начала счета, а выход переноса п-го счетчика импульсов подключен к третьему входу второго элемента ИЛИ, выход ко

Изобретение относится к импульсной технике и может быть использовано в цифровых синтезаторах частоты приемно-передающей и измерительной аппаратуры, в устройствах дискретной автоматики и вычислительной техники.

Известен делитель частоты следования имлульсов с переменным коэффициентом деления, содержащий счетчик импульсов с постоянным коэффициентом пересчета с первым блоком установки, входы которых через элементы совпадения связаны с источником входного сигнала и с выходами триггера коммутации, а также триггер управления, инвертор, элементы И и ИЛИ, второй счетчик импульсов с переменным коэффициентом пересчета и с вторым блоком установки tl 3.

В известном устройстве многоэлементная суммарная задержка выходного сигнала затягивает времяпереключений триггера коммутации в конце каждого цикла деления, в связи с чем неполностью используется быстродействие счетчиков импульсов, в результате чего известньй делитель частоты следования импульсов с переменным коэффициентом леления имеет пониженное быстродействие, что является основным недостатком этого устройства.

Наиболее близким по технической сущности и достигаемому результату к предложенному является делитель частоты следования импульсов с переменным коэффициентом деления, содержащий п последовательно соединенных счетчиков импульсов, при этом первый и второй счетчики импульсов выполнены на основе делителя 10/11, а также триггер записи, два триггера управления, два блока опознавания, два дешифратора циклов, два дешифратора нуля, триггер начала счета и трит гер-формирователь, причем входы синхронизации первого и второго триггеров управления соединены с входами

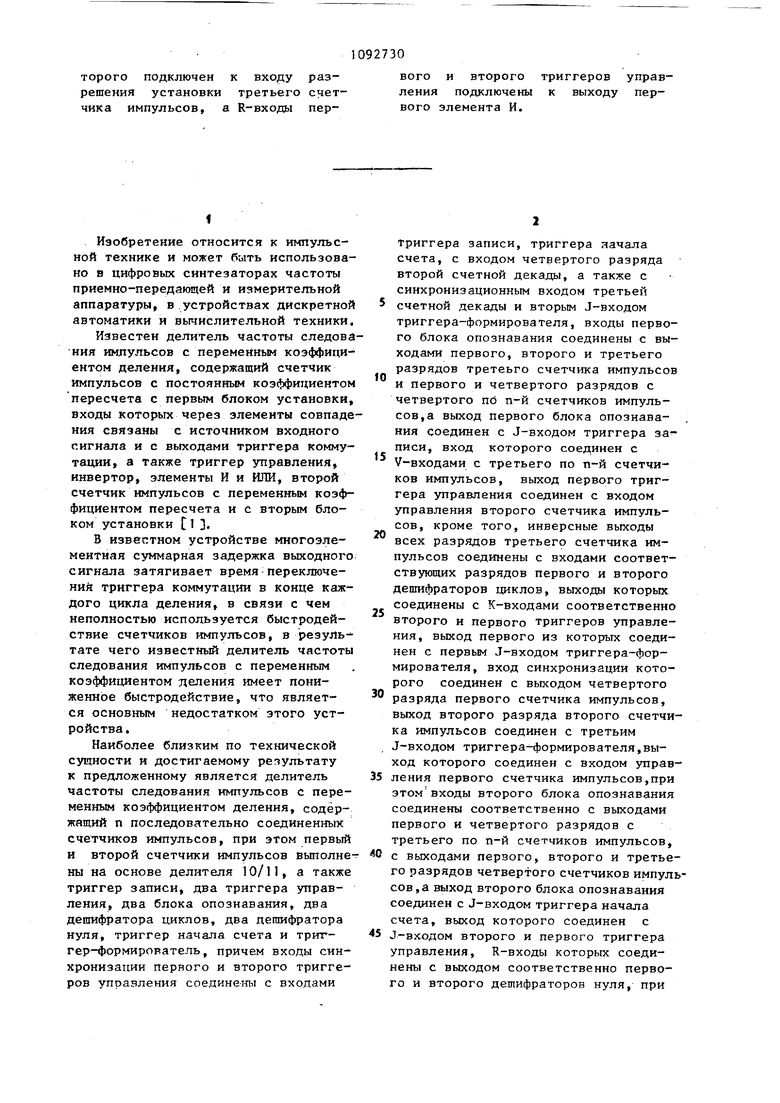

Триггера записи, триггера начала счета, с входом четвертого разряда второй счетной декады, а также с синхронизационным входом третьей счетной декады и вторым J-входом триггера-формирователя, входы первого блока опознавания соединены с выходами первого, второго и третьего разрядов третеьго счетчика импульсов и первого и четвертого разрядов с четвертого по п-й счетчиков импульсов, а выход первого блока опознавания соединен с J-входом триггера записи, вход которого соединен с V-входами с третьего по п-й счетчиков импульсов, выход первого триггера управления соединен с входом управления второго счетчика импульсов, кроме того, инверсные выходы всех разрядов третьего счетчика импульсов соединены с входами соответствующих разрядов первого и второго дешифраторов циклов, выходы которых соединены с К-входами соответственно второго и первого триггеров управления, выход первого из которых соединен с первьм J-входом триггера-формирователя, вход синхронизации которого соединен с выходом четвертого разряда первого счетчика импульсов, выход второго разряда второго счетчика импульсов соединен с третьим J-входом триггера-формирователя,выход которого соединен с входом управления первого счетчика импульсов,при этомвходы второго блока опознавания соединены соответственно с выходами первого и четвертого разрядов с третьего по п-й счетчиков импульсов, с выходами первого, второго и третьего разрядов четвертого счетчиков импулсов, а выход второго блока опознавания соединен с J-входом триггера начала счета, выход которого соединен с J-входом второго и первого триггера управления, R-входЫ которых соединены с выходом соответственно первого и второго дешифраторов нуля, при этом входы управления первых дешифра тора циклов и дешифратора нуля соединены с шинами управления первого . счетчика импульсов, а входы управления вторых дешифратора циклов и дешифратора нуля соединены с шинами управления второго счетчика импульсов. Устройство обладает высоким быстродействием и йироким диапазоном коэффициентов деления t JОднако в устройстве схема управления счетчиками импульсов сложна, так как для правильной и надежной работы устройства разносятся во вре мени момент записи кодов начальной установки счетчиков импульсов и момент начала счета циклов с помощью многовходовых блоков опознавания, при такой структуре управления необходимы дешифраторы нуля и 1К-триггеры, являющиеся более сложными и менее быстродействукяцими по отношению к RS-триггерам. Кроме того, все с третьего по п-й счетчики импульсов, а также блоки опознавания, все дешифраторы и триггеры управления, начала счета и записи должны обладать одинаковым быстродействием так как при начальной установке в эти счетчики импульсов больших чисел длительность импульсов, поступающих на их С-входы, может приближаться или быть равной длительности импульсов на выходе второго счетчика импульсов. Это не позволяет получить достаточно низкого потребления мощности и приводит к недоиспользованию элементной базы по быстродействию. Поэтому при увеличении числа счетчиков импульсов при сохранении быстродействия всего устройства требуется повьштать быстродействие этих счетчиков импульсов. При этом соответствен но повышается потребление мощности. Цель изобретения - упрощение дели теля и снижение потребляемой мощности. Поставленная цель достигается тем что в делитель, содержащий две цепи из последовательно соединенных с первого по третий и с третьего по п-й счетчиков импульсов, два триггера управления, триггер записи,триггер начала счета, два дешифратора циклов и дешифратор нуля, Q-выходы третьего счетчика импульсов соедине ны с соответствующими первыми входам первого и второго дешифраторов циков, вторые входы которых соединены с соответствующими первыми информаионными входами делителя, а вторые нформационные входы соединены с соответствующими информационными вхоами с третьего по п-й счетчиков импульсов, выход первого триггера управления соединен с управляющим входом второго счетчика импульсов, а выход триггера записи соединен с входами разрешения установки с четвертого по п-й счетчиков импульсов, введены первый и второй элементы ИЛИ, первый и второй элементы И и элемент задержки, при этом выходы первого и второго дешифраторов циклов подключены к S-входам соответственно первого и второго триггеров управления, инверсный выход второго триггера управления подключен к первому входу первого элемента ИЛИ, второй вход которого подключен к прямому выходу второго счетчика импульсов, инверсный выход которого через элемент задержки подключен к третьему входу первого элемента ИЛИ, выход которого подключен к управлякицему входу первого счетчика импульсов, а выходы разрядов третьего счетчика импульсов подключены к соответствуюгаим входам дешифратора нуля, выход которого подключен к первому в1сод первого элемента И, второй вход которого подключен к инверсному выходу триггера начала счета, прямой выход которого подключен к первому входу второго элемента И, второй вход которого подключен к выходу четвертого разряда третьего счетчика импульсов, выход переноса которого подключен к первому входу второго элемента ИЛИ и третьему входу второго элемента И, инверсный выход которого подключен к входам синхронизации с четвертого по п-й счетчиков импульсов, выход второго элемента И подключен к S-BXOду триггера записи, R-вход которого соединен с R-входом триггера начала счета инверсным выходом второго элемента ИЛИ, второй вход котррого подключен к инверсному выходу триггв ра начала счета, а выход переноса п-го счетчика импульсов подключен к третьему входу второго элемента ИЛИ, выход которого подключен к входу разрешения установки третьего счетчика импульсов, а R-входы первого и второго триггеров управления j подключены к выходу первого элемента И.На чертеже приведена структурная схема предложенного делителя. На чертеже обозначено: 1-1 - 1-4 ... 1-п-счетчики импульсов; 2, 3 дешифраторы циклов; 4,5 - триггеры управления; 6 - элемент ИЛИ; 7 - эле мент задержки; 8 - дешифратор нуля; 9 - триггер начала счета; 10,П элементы И, 12 - элемент ИЛИ; 13 триггер записи; , , , , - - 2 - группы инфор мационных входов делителя, Q-вы-ходы счетчика 1-3 соединены с соответствующими первыми входами первого и второго дешифраторов 2 и 3 вторые входы которых соединены с со о таете ТВ уклдими первыми информационньп входами делителя, а вторые информационные входы соединены с соот ветствугадими информационными входами счетчиков 1-3, ,.., ,выход счетчика соединен со счетным входом счетчика , инверсный выход которого соединен со счетным входом счетчика 1-3, выход первого триггера управления 4 соединены с управляющим входом счетчика 1-2, а выход триггера записи 13 соединен с входами разрешения установки счет чиков 1-4,... 1-п, выходы дешифраторов 2 и 3 подключены к S-входам триггеров управления 4 и 5 соответстаенно, иниерсный вьпсод второго из которых подключен к первому входу элемента 6, второй вход которого подключен к прямому выходу счетчика 1-2, инверсный выход которого через элемент 7 подключен к третьеяу входу элемента 6, выход которого подключен к з равляющему входу счетчика 1-1, а выходы разрядов счетчика 1--3 подключены к входам дейи ратора 8, выход которого подключен к первому входу элемента 10, второй вход которого подключен к инверсному выходу триггера 9, прямой выход которого подключен к первому выходу триггера 9, прямой выход которого подключен к первому входу элемента 11, второй вход которого подключен к выходу чет вертого разряда счетчика 1-3, выход переноса которого подключен к первом входу элемента 12 и третьему входу элемента 1J, инверсный выход которог подключен к входам синхронизации сче чиков 1-4,...1-п, соединенных после довательно (через выходы переноса), выход элемента 11 подключен к S-входу триггера 13, вькод которого соединен с R-входом триггера 9 и подключен к инверсному выходу элемента 12, второй вход которого подкл.кгчен -к инверсному выходу триггера 9, а выход переноса счетчика 1-п подключен к третьему входу элемента 12, выход которого подключен к входу разрешения установки счетчика -3, а R-BXOды триггеров 4 и 3 подключены к выходу элемента 10. Если в качестве счетчиков 1-1 и J-2 используются делители 10/И, а в качестве счетчиков 1-3,.., 1-п используются двоично-десятичные четырехразрядные счетчики, то коэффициент деления .Кдрдтакого устройства определяется формулой п где К коэффициент деления счетчиков I-i соответственно. Счетчики 1-1, 1-2 и 1-3 работают на сложение, а остальные - на вычитание. Коэффициент деления К связан с числом N- установки счетчиков в исходное состояние следующими выражениями: 10-N,. где N. в двоично-десятичном Число N; может принимать значения О, ..., 9, Если за период выходного сигнала делителя 10/11 первого и второго счетчика импульсов работают с коэффициентом деления 10, то общий коэффициент деления устройства будет кратным iOO. Для того, чтобы получить коэффициент деления К и К2, отличные от нуля, достаточно, чтобы счетчики 1-1 имели NJ, циклов и N циклов ссответственно коэффициент деления I1. Коэффициенты деления счетчиков 1-1 и 1-2 определяются кодами, поступающими на входы дешифраторов. Количество циклов N и N с коэффициентом деления 11 для счетчиков 1- и J-2 численно равно их коэЛфшиентам еления. Подсчет циклов с коэффициентом деления 1I как первой, так и второй декад осуществляет счетчик 1-3. Поскольку счетчик 1-3 может быть установлен в любое состояние от 0000 до 1001 в зависимости от коэффициента Kj, то переключение первых двух счетчиков импульсов на счет с коэффи циентом деления 11, а следовательно, и подсчет циклов осуществляется толь ко после того, как все разряды треть его счетчика импульсов установятся да нулевое состояние. Делитель работает следующим образом. Входная последовательность импуль сов с частотой fg и периодом Т по ступает на вход счетчика 1-1. С его выхода снимается сигнал, близкий к меандру с частотой следования f fg /10 или f f д /1 I. Это позволяет без дополнительных согласу ющих устройств сигнал с частотой f подать на вход счетчика 1-2, быстродействие которого в десять раз , ниже быстродейтсвия счетчика 1-1. С выхода счетчика 1-2 сигнал, также близкий к меандру, с частотой f или fj поступав- - ма счетный вход счетчика 1-3, что позво ляет снизить на порядок быстродейст.вие счетчика 1-3 по отношению к счетчику 1-2. Если импульсом в счетчик 1-3 записано число четыре, то на выходе четвертого разряда этого счетчика импульсов будет сигнал с укороченным начальным импульсом (при записи большего числа импульс еще короче), Поэтому в устройстве-прототипе четвертый и последующие счетчики импуль сов следует выбирать такого же быстродействия, как и третий. В данном устройстве импульс с выхода четверто го разряда счетчика 1-3 расширяется, что позволяет снизить требуемое быстродействие с четвертого по п-й счетчиков импульсов. Расгаирение этих импульсов осуществляется следующим образом. Триггер 9 устанавливаетс:я в исходное состояние положительным импульсов с выхода элемента 12, пред ставляющего собой инверсию, импульса записи, поступающего в счетчик 1-3, а импульс с дешифратора 8, появляющийся при обнулении всех разрядов счетчика 1-3, опрокидьтает триггер 9, в результате чего формируется импульс, при поступлении которого одновременно с выходным импульсом четвертого разряда счетчика 1-3 на элемент 11 образуется последовательност импульсов с раегаиренным начальным импульсом. Для ускорения момента начала первого импульса на третий вход элемента 11 подается импульс с йыхода переноса третьего счетчика импульсов. Импульсы с инверсного выхода элемента 11 поступают на вход синхронизации счетчиков 1-4, ..., 1-п. Импульсы с выходом переноса каждого из этих счетчиков импульсов поступают на вход переноса последующего счетчика импульсов, а выход переноса счетчика 1-п поступает на вход элемента 12. Если на другие входы этого элемента поступают отрицательный импульс с выхода переноса счетчика 1-3 и нулевой потенциал с -выхода триггера 9, то на выходе элемента 12.формируется импульс записи начального числа в счетчик 1-3. Поскольку счетчики 1-4,..., 1-п вы.бираются с низким быстродействием, то импульс записи дпя них расгаиряется с помощью триггера 13, который запускается по R-входу импульсом записи с инверсного выхода элемента 12 и сбрасывается по положительHcwy фронту импульса, поступающего на его S-вход с выхода элемента 11. Управление коэффи1 иентом деления .счетчиков 1-1 и 1-2 осуществляется следующим образом. I В момент обнуления всех разрядов счетчика 1-3 импульсы с выхода дешифратора 8 поступают на вход элемента 10, на другой вход которого поступают импульсы с -выхода триггера 9, в результате чего на выходе элемента 10 формируется положительный импульс, запускающий по R-входу триггеры А и 5, которые сбрасываются импульсами с выходов дешифраторов 2 и 3,соответственно, в момент совпадения кода разрядов счетчика Qj,..., Q. с кодами установки В.,,... В и А,..., А соответственно. При этом на выходе элемента 10 и, следовательно, на выходах триггеров 4 и 5 формируется только по одному импульсу 1за полный цикл работы устройства. При появлении на Q-выходе триггера 4 отрицательного импульса счетчик 1-2 делит на 11 частоту импульсов, поступающих на его вход,а по окончании этого импульса - на 10. Счетчик 1-1 вьтолняет деление на 11 только один цикл за один цикл работы счетчика 1-2. Процесс формирования импульсов управления коэффициентом деления счетчика 1-1 происходит следукицим образом. На элемеит 6 поступают импульсы с О-выхода счетчика 1-2 и задержанные с помощью эле мента 7 импульсы с И -выхода этого же счетчика импульсов, в результате чего на выходе элемента 6 формируется последовательность импульсов, которая проходит на вход управления счетчика 1-1 только во время наличия импульса, поступающего на третий вход элемента 6с и - выхода триггера 5. Длительность импульса управ ления, определяемая временем задерж ки на элементе 7, выбирается равной периоду импульсов на выходе счетчика 1-1, Задержка поступления импульсоэ управления на счетчики 1-1 и Н2 зависит от схемы этих счетчиков. Например, при использовании микросхем типа К193ИЕ 2 или К193ИЕ 3 импульсы управления могут быть задержа1Ш не более чем на семь периодов сигнала, пост5гпакщего на их вход. Счетчики 1-1 и 1-2 могут иметь и другие коэффициенты деления. Остальные счетчики импульсов также не обязательно должны выбираться двоично-десятичными. Например, при использовании двоичных счетчиков импульсов можно сократить их общзпо .разрядность без снижения диапазона, изменения коэффициентов, деления Использование данного изобретения позволяет упростить устройство за счет исключения многовходовых блоков опознавания и дешифратора нуля, а также заменить JK-трнггеры на более простые, экономичные и быстродействующие RS-триггеры. Кроме того, оно позволяет уменьшить на порядок быстродействие с четвертого по п-й счетчиков .импульсов, что он, жает потребление энергии.и, как правило, снижает его стоимость. Бели, например, при работе устройства-прототипа с частотой входного сигнала до 200-500 МГц в качестве счетчиков с третьего по п-й приходится использовать микросхемы типа К155ИЕ 7 или К133ИЕ7, каадый из которых потребляет ток около 100 мА, то в данном устройстве при работе на той же частоте входного сигнала используется только один третий счетчик на микросхеме такого типа, ас четвертого по п-й счетчики импульсов возможно выполнить на менее быстродействующих элементах, например К564ИЕ 14, потребляющих ток ие более. 1 мА. Аналогичное сокращение потребляемой мощиости достигается за счет замены не меиее быстродействующую ceptfio элементов регистров памяти, входящих в составделителей для хранения кодов начальной установки счетчиков импульсов. Таким образом, в зависимости от числа счетчиков п и частоты входного сигнала обеспечивается снижение потребляемой мощности более чем в 3 раза по сравнению с базовым объектом, выполненным по схеме прототипа

1-1

Lrfr

-с ,,

11адн

1

ЛШЪтРТ ъ

в

1Ь

-J

т

г

ts-t.

(t-f

S 9-i

Щ

f-#

- л

«ч

4 -«

-, М -К)

г« V-lfJ

«)

еуг

| I | |||

| Устройство для усиления микрофонного тока с применением самоиндукции | 1920 |

|

SU42A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Делитель частоты следования импульсовС пЕРЕМЕННыМ КОэффициЕНТОМ дЕлЕНия | 1979 |

|

SU843245A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1984-05-15—Публикация

1983-01-06—Подача