(54) УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ ОТНОШЕНИЯ СИГНАЛ/ПОМЕХА

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ОПРЕДЕЛЕНИЯ ДЛИТЕЛЬНОСТИ ЭЛЕМЕНТАРНОЙ ПОСЫЛКИ ТЕЛЕГРАФНЫХ СООБЩЕНИЙ С РАЗЛИЧНЫМИ СКОРОСТЯМИ ТЕЛЕГРАФИРОВАНИЯ | 1973 |

|

SU383218A1 |

| Устройство автовыбора канала при разнесенном приеме | 1980 |

|

SU886273A1 |

| Интегрирующее устройство дискретного действия | 1972 |

|

SU469953A1 |

| Устройство тактовой синхронизации | 1979 |

|

SU932642A1 |

| Устройство для измерения краевых искажений двоичных сигналов типа "преобладаний | 1984 |

|

SU1215186A1 |

| Устройство для адаптивной регистрации электрических посылок | 1985 |

|

SU1298941A2 |

| Устройство для измерения преобладаний дискретных сигналов | 1979 |

|

SU879805A1 |

| Устройство поэлементной синхронизации | 1987 |

|

SU1517142A1 |

| СИСТЕМА ПЕРЕДАЧИ И ПРИЕМА ДИСКРЕТНОЙ ИНФОРМАЦИИ ПО РАДИОКАНАЛАМ ИМПУЛЬСНО-ФАЗОВОЙ РАДИОНАВИГАЦИОННОЙ СИСТЕМЫ | 1994 |

|

RU2079855C1 |

| Цифровой асинхронный регенератор дискретных сигналов | 1990 |

|

SU1788582A1 |

I

Изобретение относится к электросвязи и может использоваться для измерения отношения сигнал/помеха в каналах частотного радиотелеграфирования.

Известно устройство для измерения отношения сигнал/помеха при передаче дискретной информации, содержащее последовательно соединенные задающий генератор, блок интегрирования, другой вход которого соединен с входом устройства,, и счетчик заполняющих импульсов, а также вычислительный блок, выход которого подключен ко входу индикатора 1 .

Однако известное устройство не позволяет оценить качество элементарной посылки и имеет низкую точность измерения.

Цель изобретения - повышение точности измерения и получение оценки качества каждой элементарной посылки.

Цель достигается тем, что в устройство для измерения отношения сигнал/помеха при передаче дискретной информации, содержащее последовательно соединенные задающий генератор, блок интегрирования, другой вход которого соединен с входом устройства, и счетчик заполняющих импульсов, а также вычислительный блок, выход которого подключей ко входу индикатора, введены накопитель действующей помехи, управляющий вход которого соединен с выходом счетчика заполняющих импульсов, а сигнальный вход соединен с вторым выходом блока интегрирования, и блок определения полярности посылки, счетный вход которого соединен с выходом счетчика заполняющих импульсов, а сигнальный вход соединен с третьим выходом блока интегрирования, при этом выходы накопителя действующей помехи и блока определения полярности посылки подключе10ны к входам вычислительного блока.

Кроме того, блок интегрирования выполнен в виде дискретного интегратора.

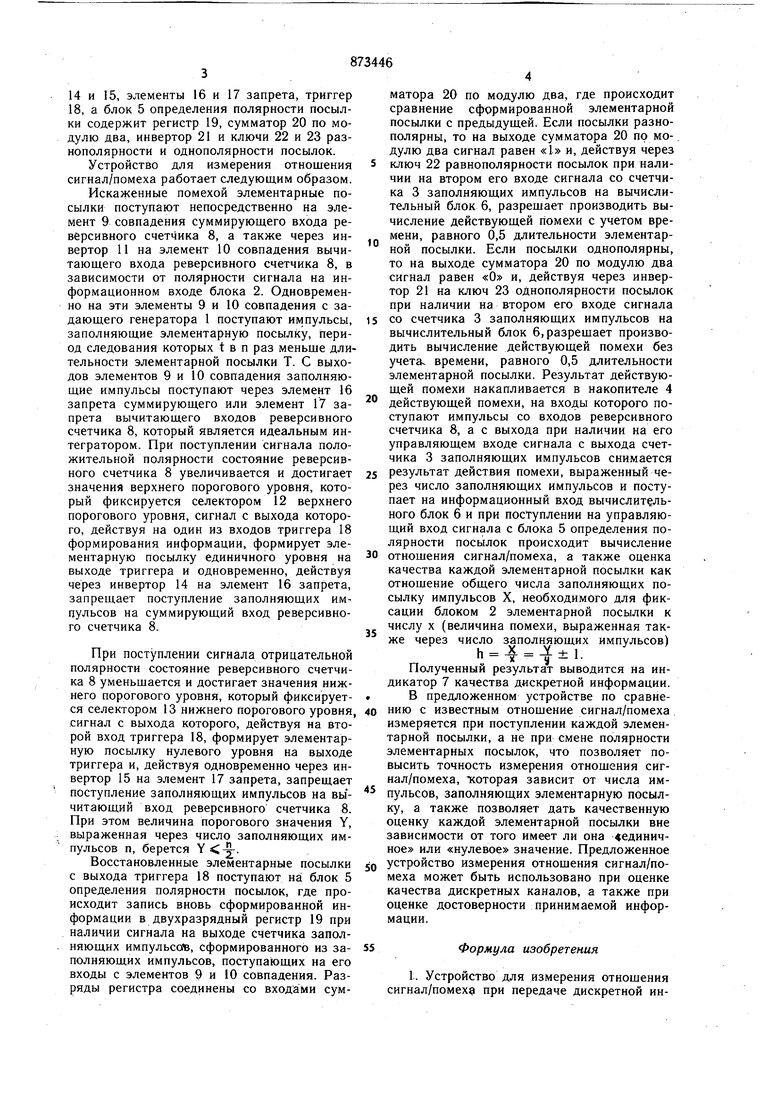

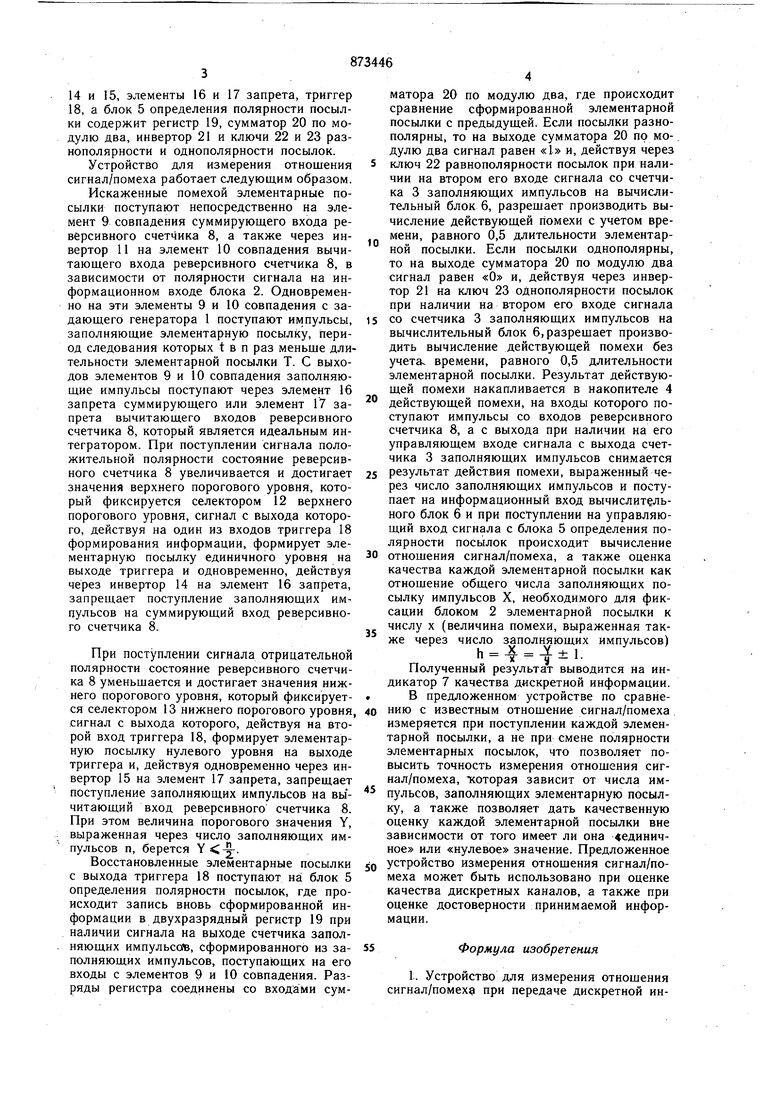

На чертеже приведена структурная электрическая схема предложенного устройства.

Устройство содержит задающий генераtsтор 1, блок 2 интегрирования, счетчик 3 заполняющих импульсов, накопитель 4 действующий помехи, блок 5 определения полярности посылки, вычислительный блок 6, индикатор 7. Кроме того, блок 2 интегрирования содержит реверсивный счетчик 8, эле30менты 9 и 10 совпадения, инвертор 11, селектор 12 верхнего порогового уровня, селектор 13 нижнего порогового уровня, инверторы 14 и 15, элементы 16 и 17 запрета, триггер 18, а блок 5 определения полярности посылки содержит регистр 19, сумматор 20 по модулю два, инвертор 21 и ключи 22 и 23 разнополярности и однополярности посылок. Устройство для измерения отношения сигнал/помеха работает следующим образом. Искаженные помехой элементарные посылки поступают непосредственно на элемент 9 совпадения суммирующего входа реверсивного счетчика 8, а также через инвертор 11 на элемент 10 совпадения вычитающего входа реверсивного счетчика 8, в зависимости от полярности сигнала на информационном входе блока 2. Одновременно на эти элементы 9 и 10 совпадения с задающего генератора 1 поступают импульсы, заполняющие элементарную посылку, период следования которых t в п раз меньше длительности элементарной посылки Т. С выходов элементов 9 и 10 совпадения заполняющие импульсы поступают через элемент 16 запрета суммирующего или элемент 17 запрета вычитающего входов реверсивного счетчика 8, который является идеальным интегратором. При поступлении сигнала положительной полярности состояние реверсивного счетчика 8 увеличивается и достигает значения верхнего порогового уровня, который фиксируется селектором 12 верхнего порогового уровня, сигнал с выхода которого, действуя на один из входов триггера 18 формирования информации, формирует элементарную посылку единичного уровня на выходе триггера и одновременно, действуя через инвертор 14 на элемент 16 запрета, запрещает поступление заполняющих импульсов на суммирующий вход реверсивного счетчика 8. При поступлении сигнала отрицательной полярности состояние реверсивного счетчика 8 уменьщается и достигает значения нижнего порогового уровня, который фиксируется селектором 13 нижнего порогового уровня сигнал с выхода которого, действуя на второй вход триггера 18, формирует элементарную посылку нулевого уровня на выходе триггера и, действуя одновременно через инвертор 15 на элемент 17 запрета, запрещает поступление заполняющих импульсов на вычитающий вход реверсивного счетчика 8. При этом величина порогового значения Y, выраженная через число заполняющих импульсов п, берется . Восстановленные элементарные посылки с выхода триггера 18 поступают на блок 5 определения полярности посылок, где происходит запись вновь сформированной информации в двухразрядный регистр 19 при наличии сигнала на выходе счетчика заполняющих импульсаь, сформированного из заполняющих импульсов, поступающих на его входы с элементов 9 и 10 совпадения. Разряды регистра соединены со входами сумматора 20 по модулю два, где происходит сравнение сформированной элементарной посылки с предыдущей. Если посылки разнополярны, то на выходе сумматора 20 по мо-. дулю два сигнал равен «1 и, действуя через ключ 22 разнополярности посылок при наличии на втором его входе сигнала со счетчика 3 заполняющих импульсов на вычислительный блок 6, разрешает производить вычисление действующей помехи с учетом времени, равного 0,5 длительности элементарной посылки. Если посылки однополярны, то на выходе сумматора 20 по модулю два сигнал равен «О и, действуя через инвертор 21 на ключ 23 однополярности посылок при наличии на втором его входе сигнала со счетчика 3 заполняющих импульсов на вычислительный блок 6, разрешает производить вычисление действующей помехи без учета, времени, равного 0,5 длительности элементарной посылки. Результат действующей помехи накапливается в накопителе 4 действующей помехи, на входы которого поступают импульсы со входов реверсивного счетчика 8, а с выхода при наличии на его управляющем входе сигнала с выхода счетчика 3 заполняющих импульсов снимается результат действия помехи, выраженный через число заполняющих импульсов и поступает на информационный вход вычислительного блок 6 и при поступлении на управляющий вход сигнала с блока 5 определения полярности посылок происходит вычисление отношения сигнал/помеха, а также оценка качества каждой элементарной посылки как отнощение общего числа заполняющих посылку импульсов X, необходимого для фиксации блоком 2 элементарной посылки к числу X (величина помехи, выраженная также через число заполняющих импульсов) h 4 -J±l. Полученный результат выводится на индикатор 7 качества дискретной информации. В предложенном устройстве по сравнению с известным отношение сигнал/помеха измеряется при поступлении каждой элементарной посылки, а не при смене полярности элементарных посылок, что позволяет повысить точность измерения отношения сигнал/помеха, которая зависит от числа импульсов, заполняющих элементарную посылку, а также позволяет дать качественную оценку каждой элементарной посылки вне зависимости от того имеет ли она чединичное или «нулевое значение. Предложенное устройство измерения отношения сигнал/помеха может быть использовано при оценке качества дискретных каналов, а также при оценке достоверности принимаемой информации. Формула изобретения 1. Устройство для измерения отнощения сигнал/помехэ при передаче дискретной информации, содержащее последовательно соединенные задающий генератор, блок интегрирования, другой вход которого соединен с входом устройства, и счетчик заполняющих импульсов, а также вычислительный блок, выход которого подключен ко входу индикатора, отличающееся тем, что, с целью повышения точности измерения и получения оценки качества каждой элементарной посылкн, введены накопитель действующей помехи, управляющий вход которого соединен с выходом счетчика заполняющих импульсов,а сигнальный вход соединен с вторым выходом блока интегрирования, и блок определения полярности посылки, счетный вхоД ко

(/ск1 тны1Гмнтег1 лтаР 2.

торого соединен с выходом счетчика заполняющих импульсов, а сигнальный вход соединен с третьим выходом блока интегрирования, при этом выходь накопителя действующей помехи и блока определения полярности посылки подключены к входам вычислительного блока. .

Источники информации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР № 557496, кл. Н 04 L 11/08, 1974 (прототип).

«1К.ИН9.

Авторы

Даты

1981-10-15—Публикация

1978-11-20—Подача