(5) УСТРОЙСТВО ТАКТОВОЙ СИНХРОНИЗАЦИИ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство тактовой синхронизации | 1981 |

|

SU1007211A1 |

| Устройство тактовой синхронизации | 1988 |

|

SU1614122A2 |

| Анализатор сигнала тактовой синхронизации | 1977 |

|

SU621112A1 |

| Анализатор сигнала тактовой синхронизации | 1976 |

|

SU560354A2 |

| Анализатор сигнала тактовой синхронизации | 1974 |

|

SU496688A1 |

| Устройство для детектирования фазоманипулированных сигналов | 1982 |

|

SU1042203A1 |

| Анализатор сигнала тактовой синхронизации | 1982 |

|

SU1125763A2 |

| Устройство для получения сигналов настройки синхронизации границ посылок в многоканальных системах связи с ортогональными синусоидальными сигналами | 1977 |

|

SU649147A2 |

| Частотный дискриминатор | 1978 |

|

SU790252A1 |

| Демодулятор для многоканальной системы передачи дискретной информации | 1974 |

|

SU540404A1 |

I

Изобретение относится к технике передачи дискретной информации по радиоканалам и может использоваться для тактовой синхронизации (синхронизации границ посылок) многоканальных модемов с ортогональными сигналами и относительной фазовой модуляции, .работающих короткими сеансами связи в KB радиоканала с длительным поддержанием синхронного состояния модема в перерывах между сеансами.

Известно устройство тактовой синхронизации, содержащее блок измерителей переходных помех, блок выбора режима подстройки, последовательно соединенные блок вычитания и интегратор, выход которого подключен к входу блока подстройки границ посылок сигнала, причем выход блока измерителей переходных помех подключен к входу блока вычитания ООднако известное устройство имеет длительное время вхождения в синхронизм и низкие помехоустойчивость

И точность подстройки при селективных замираниях и сосредоточенной помехе .

Цель изобретения - сокращение времени вхождения в синхронизм и повышение помехоустойчивости и точности подстройки при селективных замираниях и сосредоточенной помехе.

Указанная цель достигается тем, что в устройство тактовой синхрониза10|ции, содержащее блок измерителей переходных помех, блок выбора режима подстройки, последовательно соединенные блок вычитания и интегратор, выход которого подключен к входу бло15ка подстройки границ посылок сигнала, причем выход блока измерителей переходных помех подключен к входу блока вычитания, введены блок принудительной подстройки, анализатор состояний

X синхройиЗма и накопитель, при этом выход блока измерителей переходных помех через накопитель подключен к сигнальным входам блока выбора режима

подстройки и блока принудительной подстройки, выходы которого подключены соответственно к другому входу интегратора и к второму входу накопителя к третьему входу которого и к управляющим входам блока принудительной подстройки, блока измерителей переходных помех, блока вычитания,накопителя, анализатора состояния синхронизма и блока выбора режима подстройки подключен первый выход блока подстройки границ посылок сигнала, второй выход которого подключен к соответствующим входам интегратора и блока принудительной подстройки, к .соответствующему входу которого подключен первый выход блока выбора режима подстройки, второй выход которого подключен к управляющему входу ч блока подстройки границ посылок си1- нала и к соответствующему входу анализатора состояния синхронизма, выход которого подключен к четвертому накопителя.

При этом блок измерителей переходных помех выполнен в виде последовательно соединенных перемножителя, к опорному входу которого Подключен выход опорного генератора, интегратора с цепями обратной связи, выходы которых через блок коммутации подключены к входам блока вычитания, выход которого подключен к входу линейного детектора, причем к управляющим входам блока коммутации и цепей обратной связи интегратора подключен выход распределителя импульсов, вход которого является управляющим входом блока измерителей переходных помех.

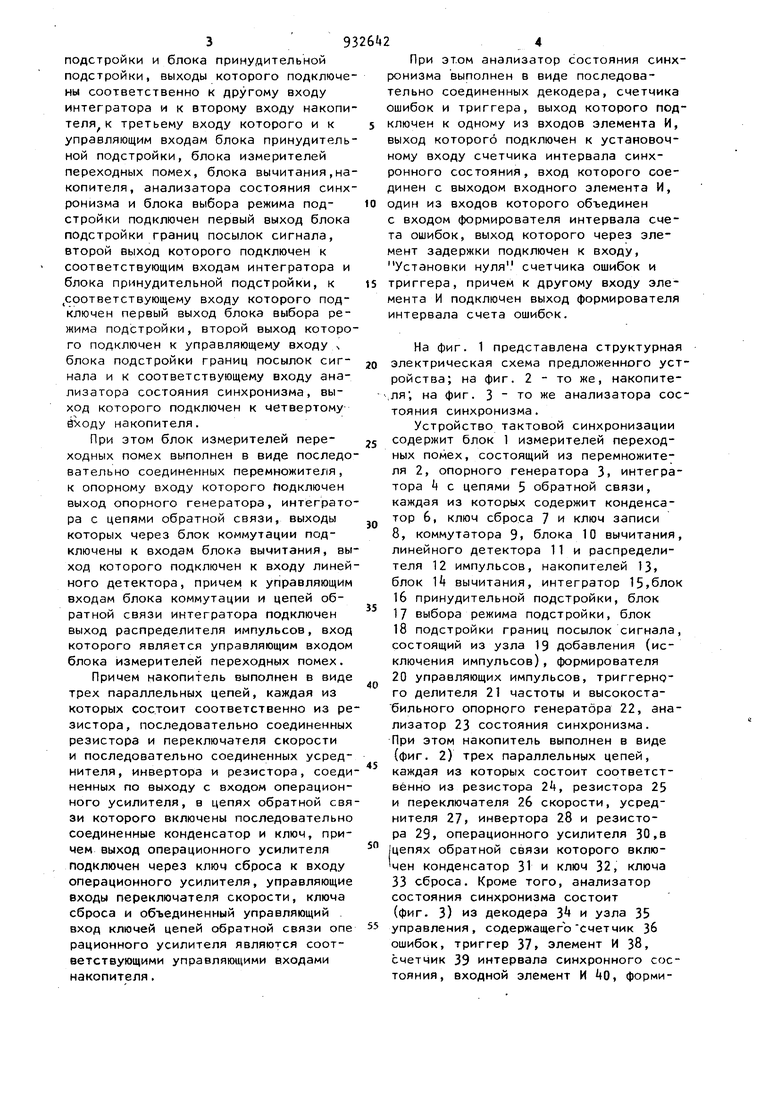

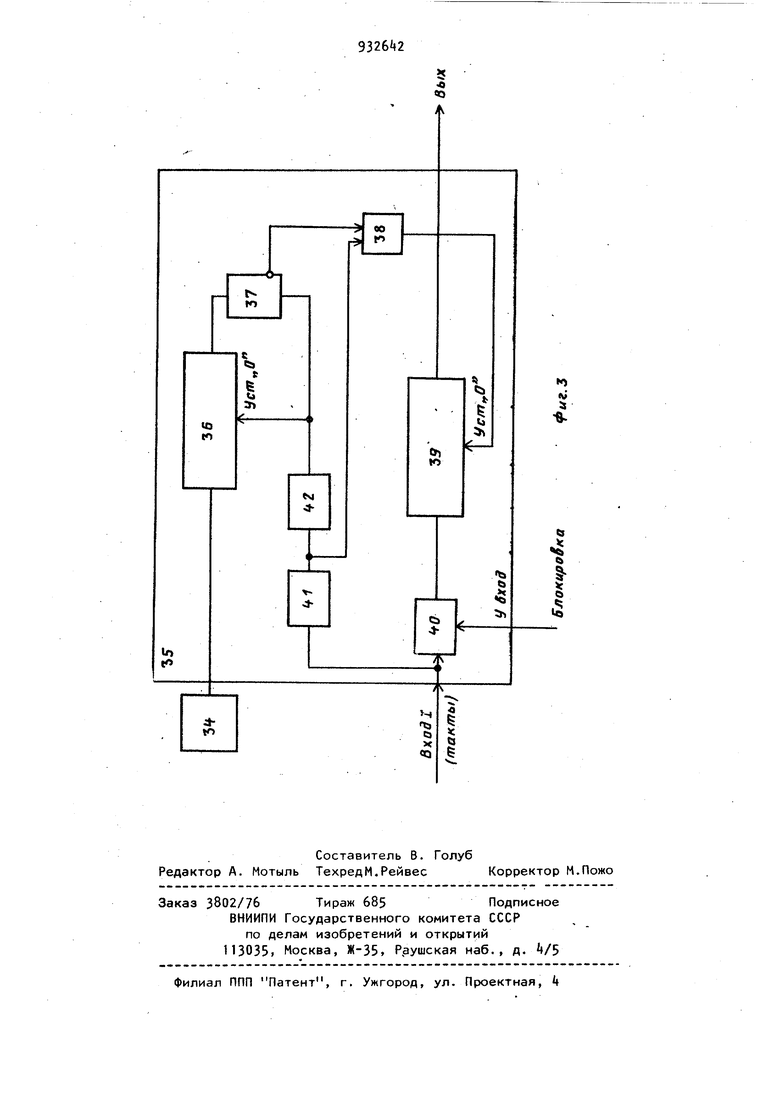

Причем накопитель выполнен в виде трех параллельных цепей, каждая из которых состоит соответственно из резистора, последовательно соединенных резистора и переключателя скорости и последовательно соединенных усреднителя, инвертора и резистора, соединенных по выходу с входом операционного усилителя, в цепях обратной связи которого включены последовательно соединенные конденсатор и ключ, примем выход операционного усилителя подключен через ключ сброса к входу операционного усилителя, управляющие входы переключателя скорости, ключа сброса и объединенный управляющий , вход ключей цепей обратной связи one рационного усилителя являются соответствующими управляющими входами накопителя,

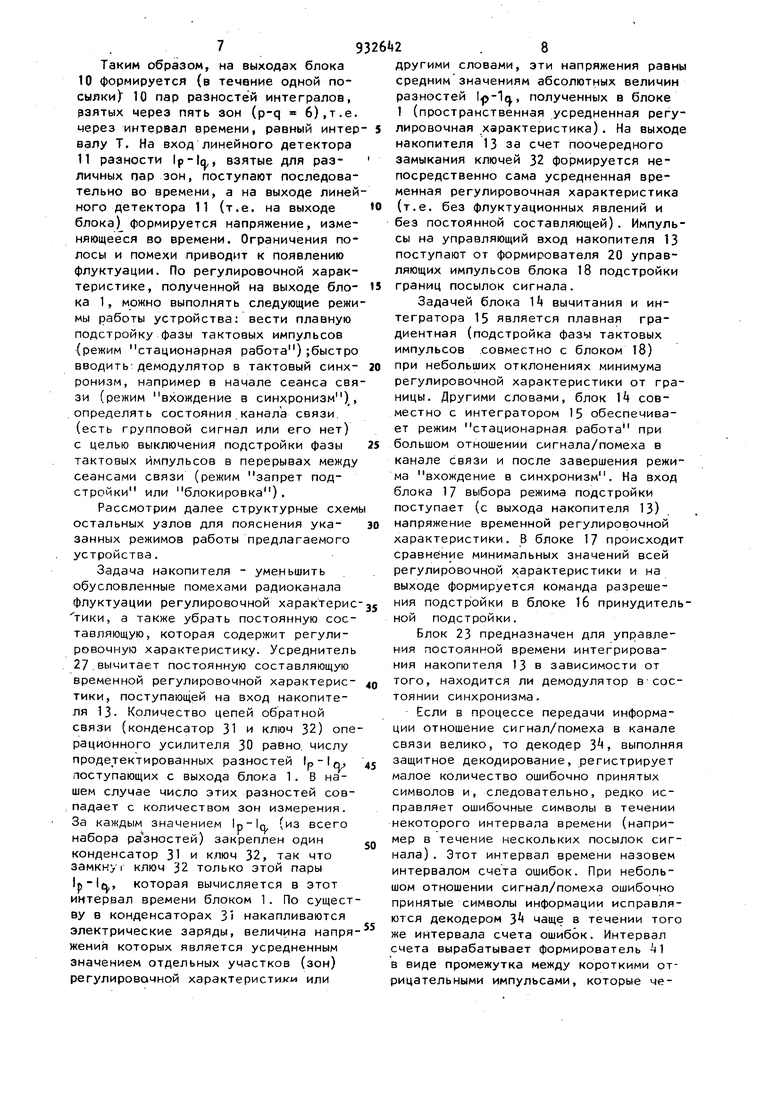

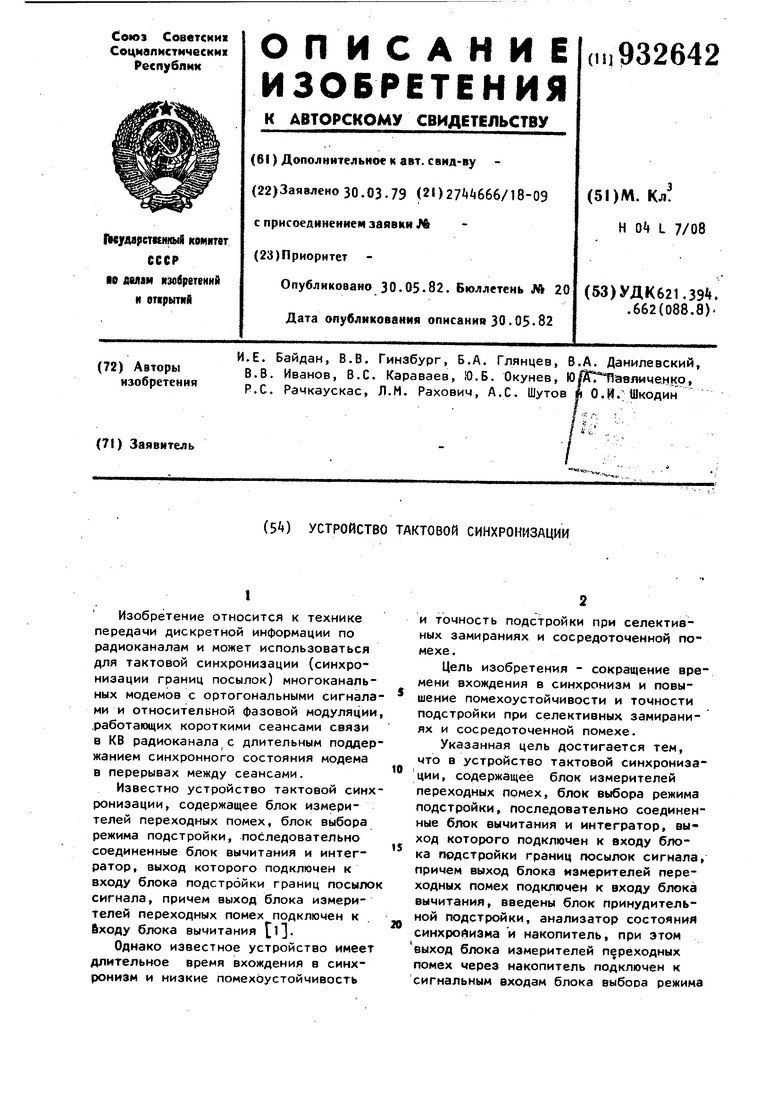

При этом анализатор состояния синхронизма выполнен в виде последовательно соединенных декодера, счетчика ошибок и триггера, выход которого подключен к одному из входов элемента И, выход которого подключен к установочному входу счетчика интервала синхронного состояния, вход которого соединен с выходом входного элемента И,

один из входов которого объединен с входом формирователя интервала счета ошибок, выход которого через элемент задержки подключен к входу, Установки нуля . счетчика ошибок и

5 триггера, причем к другому входу элемента И подключен выход формирователя интервала счета ошибок.

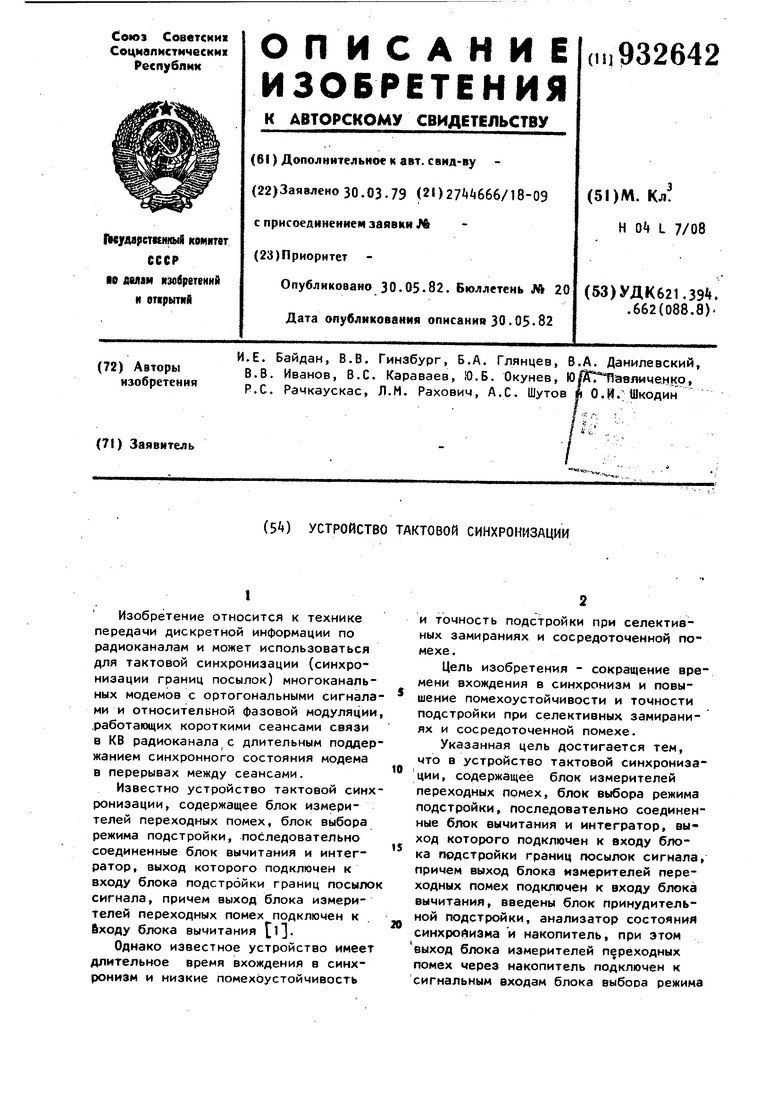

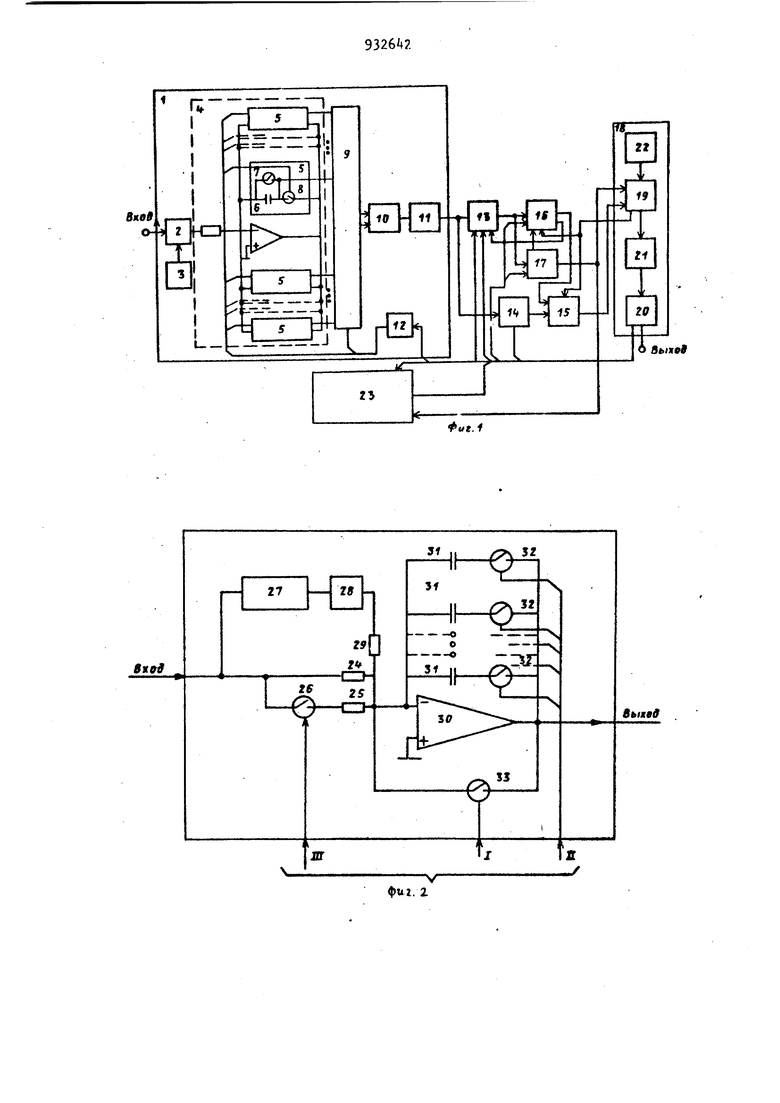

На фиг. 1 представлена структурная 0 электрическая схема предложенного устройства; на фиг. 2 - то же, накопите ,ля; на фиг. 3 то же анализатора состояния синхронизма.

Устройство тактовой синхронизации 5 содержит блок 1 измерителей переходных помех, состоящий из перемножителя 2, опорного генератора 3, интегратора k с цепями 5 обратной связи, каждая из которых содержит конденсатор 6, ключ сброса 7 и ключ записи 8, коммутатора 9 блока 10 вычитания, линейного детектора 11 и распределителя 12 импульсов, накопителей 13, блок 1 вычитания, интегратор 15,блок

16принудительной подстройки, блок

17выбора режима подстройки, блок

18подстройки границ посылок сигнала, состоящий из узла 19 добавления (исключения импульсов), формирователя

20 управляющих импульсов, триггерндго делителя 21 частоты и высокостабильного опорного генератора 22, анализатор 23 состояния синхронизма. При этом накопитель выполнен в виде {фиг. 2) трех параллельных цепей, каждая из которых состоит соответственно из резистора 2, резистора 25 и переключателя 26 скорости, усреднителя 27 инвертора 28 и резистора 29, операционного усилителя 30,в цепях обратной связи которого включен конденсатор 31 и ключ 32, ключа 33 сброса. Кроме того, анализатор состояния синхронизма состоит (фиг. 3) из декодера 3 и узла 35 5 управления, содержащего счетчик 36 ошибок, триггер 37. элемент И 38, счетчик 39 интервала синхронного состояния, входной элемент И 0, формирователь 4l интервала счета ошибок и элемент Ц2 задержки. Устройство работает следующим образом. Интервал посылки принимаемого группого сигнала условно разбивается на несколько одинаковых зон (например 10 таких зон). По количеству зон (в нашем случае 10) устанавливается число цепей 5 обратной связи интегратора k блока 1 измерителей пёреходных помех так, что конденсатор 6 с ключами сброса 7 и записи 8 одной цепи обратной связи обслуживают только одну зону, закрепленную за этой цепью 5 обратной связи. В процессе работы интегратора + блока 1 всегда замкнут ключ 8 записи только одной из цепей 5 обратной связи соответствующий интервалу времени, приходящемуся на данную зону. Однако перед замыканием ключа 8 записи данной зоны результат предыдущего интегрирования по этой зоне предвари тельно считывается коммутатором 9 на вход блока 10, а затем стирается клю чом 7 сброса. Управляющие импульсы для ключей и коммутатора поступают из распределителей 12 импульсов. , На интервале одной посылки групповой сигнал представляет собой сумму, синусоидальных колебаний кратных одной частоте. Тогда, сам групповой сигнал на интервале одной пот сылки представляет собой периодическую функцию времени. Отсчеты сигнала взятые через интервал времени, равный периоду группового сигнала (Т), равны между собой, если оба -отсчета принадлежат одной и той же посылке сигнала. Поэтому разность двух отсче тов будет малой (равной нулю с точностью до помех), если оба отсчета принадлежат одной и той же посылке (между отсчетами не было смены фаз) и будет большой, если отсчеты взяты на разных посылках (при условии,что на границе посылки имел место скачек фазы). В блоке 1 берутся не отсчеты сигнала, а интегрируется на интервале д t (т.е. на интервале зоны) произведение сигнала и опорного колебания среднего по частоте канала. При этом в качестве первого отсчета используется величина i tV-t}if«ifio-tav где S(t) - групповой сигнал , Шд - частота среднего канального сигнала; ut - интервал времени (длительность .одной зоны) , в нашем случае равный 0,1 длительности посылки. В качестве второго отсчета определяется такой же интеграл, взятый через время Т. T+u-fc Ip-f S(i)Sin(JUotdt причем ,s«(«;,t..f;,,«T, где К - номера каналов, - начальные фазы канальных сигналов , к,и - разность фаз соседних посылок ; N - число каналов в модеме пе- ; редачи данных. Учитывая взаимную ортогональность канальных сигналов, при которой ,((sl}Qгде m - целое число, можно показать, что величины интегралов IQ, и I р оказываются пропорциональными суммам синусов вида fj rtir (vY, . (,v,) Если оба интеграла интегрирования попадут на одну и туже посылку, то фазы f| для обоих интервалов и Чщ, для обоих интервалов будут одинаковыми и разность 1р-1й окажется равной нулю (с точностью до помехи), если же иитервалы попадут на разные посылки разность Ip-lq, будет большой по абсолютной величине) из-за разности значений фаз. Таким образом, заряд накопившийся в конденсаторе 6 по окончании интегрирования каждой из зон, отражает величину интеграла отсчета произведения, полученного в перемножителе 2 группового сигнала на колебание от опорного генератора 3На входы блока 10 считываются (коммутатором) одновременно напряжения от пары конденсаторов 6 цепей обратной связи 5 (так, чтобы получить разность pIft, через интервал Т) в следующем порядке: l7Hi 7 X. .f i-l5-J f г 7 Д 4 в 5 . б -«анаконец снова IT-I.

Таким образом, на выходах блока

10формируется (в течение одной посылки) 10 пар разностей интегралов, ээятых через пять зон (p-q 6),т.е. через интервал времени, равный интер- 5 валу Т. На вход линейного детектора

11разности lp-l(j,, взятые для разяичных пар зон, поступают последовательно во времени, а на выходе линейного детектора 11 (т.е. на выходе 0 блока) формируется напряжение, изменяющееся во времени. Ограничения полосы и помехи приводит к появлению флуктуации. По регулировочной характеристике, полученной на выходе бло- 5 ка 1, можно выполнять следующие режимы работы устройства: вести плавную подстройку фазы тактовых импульсов (режим стационарная работа);быстро вводить:демодулятор 8 тактовый синх- 20 ронизм, например в начале сеанса связи (режим вхождение в синхронизм), определять состояния канала связи, (есть групповой сигнал или его нет)

с целью выключения подстройки фазы 25 тактовых импульсов в перерывах между сеансами связи (режим запрет подстройки или блокировка).

Рассмотрим далее структурные схемы остальных узлов для пояснения ука- зо занных режимов работы предлагаемого устройства.

Задача накопителя - уменьшить обусловленные помехами радиоканала флуктуации регулировочной характерис-дд тики, а также убрать постоянную составляющую, которая содержит регулировочную характеристику. Усреднитель 27,вычитает постоянную составляющую временной регулировочной характерис- 40 тики, поступающей на вход накопителя 13- Количество цепей обратной связи (конденсатор 31 и ключ 32) операционного усилителя 30 равно, числу продетектированных разностей 1р-1ф 45 поступающих с выхода блока 1. В наем случае число этих разностей совпадает с количеством зон измерения. За каждым значением (из всего набора разностей) закреплен один ,конденсатор 31 и ключ 32, так что амкнут ключ 32 только этой пары

Iplq, которая вычисляется в этот нтервал времени блоком 1. По сущесту в конденсаторах 31 накапливаются лектрические заряды, величина напряения которых является усредненным начением отдельных участков (зон) егулировочной характеристики или

другими словами, эти напряжения равны средним значениям абсолютных величин разностей ., полученных в блоке 1 (пространственная усредненная регулировочная характеристика). На выходе накопителя 13 за счет поочередного замыкания ключей 32 формируется непосредственно сама усредненная временная регулировочная характеристика (т.е. без флуктуационных явлений и без постоянной составляющей). Импульсы на управляющий вход накопителя 13 поступают от формирователя 20 управляющих импульсов блока 18 подстройки границ посылок сигнала.

Задачей блока 1 вычитания и интегратора 15 является плавная градиентная (подстройка фазы тактовых импульсов .совместно с блоком 18) при небольших отклонениях минимума регулировочной характеристики от границы. Другими словами, блок 14 совместно с интегратором 15 обеспечивает режим стационарная работа при большом отношении сигнала/помеха в канале связи и после завершения режима вхождение в синхронизм. На вход блока 17 выбора режима подстройки поступает (с выхода накопителя 13) напряжение временной регулировочной характеристики. В блоке 17 происходит сравнение минимальных значений всей регулировочной характеристики и на выходе формируется команда разрешения подстройки в блоке 16 принудительной подстройки.

Блок 23 предназначен для управления постоянной времени .интегрирования накопителя 13 в зависимости от того, находится ли демодулятор всостоянии синхронизма.

Если в процессе передачи информации отношение сигнал/помеха в канале связи велико, то декодер 3 выполняя защитное декодирование, регистрирует малое количество ошибочно принятых символов и, следовательно, редко исправляет ошибочные символы в течении некоторого интервала времени (например в течение нескольких посылок сигнала) . Этот интервал времени назовем интервалом счета ошибок. При небольшом отношении сигнал/помеха ошибочно принятые символы инфор.мации исправляются декодером 3 чаще в течении того же интервала счета ошибок. Интервал счета вырабатывает формирователь 1 в виде промежутка между короткими отрицательными импульсами, которые че9рез элемент 2 задержки устанавливают счетчик Зб ошибок в нулевое сосг тояние. Таким образом, если число исправляемых символов за интервал счета не велико, то последний триггер счетчика Зб всегда будет в нулевом состоянии, а триггер 37 также будет в нуле вом состоянии. Высокий потенциал с выхода нуля триггера 37 будет удерживать первый элемент И 38 в открыто состоянии и счетчик 39 также будет в нулевом состоянии. Кроме того, при большом отношении сигнал/помеха в канале связи имеет место режим стационарная работа (или вхождение) и режим блокировка включен. На управляющий вход узла 35 управления при этом поступает низкий потенциал и входной элемен И закрыт. Тактовые импульсы, поступающие на вход блока 23, на вход счетчика 39 не проходят. На выход блока 23 присоединен вывод единицы последнего триггера счетчика 39, так что, когда последний не заполнен, низкий потенциал выхода блока 23 подается на управляющий вход накопителя 13 и имеет место большая постоян ная времени интегратора накопителя, что соответствует достаточной фильтрации помех и большой памяти RC-цепи интегратора. Это, в свою очередь, соответствует высокому порогу между наибольшим и наименьшим значением регулировочной характеристики накопи теля, т.е. высокому качеству прохождения сигнала в канале связи. Емкост счетчика 39 такова, что до его запол нения (установка последнего триггера в 1) нужен интервал времени в несколько десятков минут. Этот интерва является контрольным в перерывах меж ду сеансами связи при включенном режиме блокировка. При этом, если перерыв связи между сеансами (при включенном режиме блокировка) не превысил контрольного интервала, тог да в накопителе 13 все время будет включена большая постоянная времени, при этом поме-хи канала связи не могу привести к ошибочному выключению режима блокировки, и в накопителе сохраняется старое значение регулировочной характеристики относительно зон интегрирования системы тактовой синхронизации. Новый сеанс связи за счет этого наминается без режима вхождение в +2 синхронизм. Если, однако, перерыв между сеансами связи превысил контрольный интервал, то устанавливается малая постоянная времени, что соответствует большой скорости накопления накопителя 13. В этом режиме накопитель быстро отреагирует на появление сигнала и задержка включения режима вхождение будет небольшой . Однако при малой постоянной времени велика вероятность того, что помехи канала связи приведут к ошибочному выключению режима блокировки и старое значение регулировочной характеристики буд,ет потеряно. На новый сеанс связи предлагаемое устройство будет реагировать как на первый. Формула изобретения 4,Устройство тактовой синхронизации, содержащее блок измерителей переходных помех, блок выбора режима подстройки, последовательно соединенные блок вычитания и интегратор, выход которого подключен к входу блока подстройки границ посылок сигнала, причем выход блока измерителей переходных помех подключен к входу блока вычитания, отличающееся тем, что, с целью сокращения времени вхождения в синхронизм и повышения помехоустойчивости и точности подстройки при селектированных замираниях и сосредоточенной помехе, в него введены блок принудительной подстройки, анализатор состояния синхронизма и накопитель, при этом выход блока измерителей переходных помех через накопитель подключен к сигнальным вхо- дам блока выбора режима подстройки и блока принудительной подстройки, выходы которого подключены соответственно к другому входу интегратора и к второму входу накопителя, к третьему входу которого и к управляющим входам блока принудительной подстройки,блока измерителей переходных помех, блока вычитания, накопителя, анализато-. ра состояния синхронизма и блока выбора режима подстройки подключен первый выход блока подстройки границ посылок сигнала, второй выход которого подключен ксоответствующим входам интегратора и блока принудительной подстройки, к соответствуТощему входу которого подключен первый выход бло11 ,3 ка выбора режима подстройки, второй выход которого подключен к управляющ му входу блика подстройки границ пос лок сигнала и к соответствующему вхо анализатора состояния синхронизма ,вы ход которого подключен к четвертому входу накопителя. 2, Устройство по п. 1, о т л и чающееся тем, что блок измерителей переходных помех выполнен в виде последовательно соединенных перемножителя, к опорному входу которо го подключен выход опорного генерато ра , интегратора с цепями обратной связи, выходы которых через блок ком мутации подключены к в-ходам блока вы читания, выход которого подключен к входу линейного детектора, причем к управляющим входам блока коммутаци и цепей обратной связи интегратора подключен выход распределителя импульсов, вход которого является управляющим входом блока измерителей переходных помех. 3- Устройство по п. 1, о т л и чающееся тем, что накопитель выполнен в виде трех параллельных цепей, каждая из которых состоит соответственно из резистора, последовательно соединенных резистора и переключателя скорости и последовательно соединенных усреднителя, инвертора и резистора, соединенных по выходу с входом операционного усилителя, в цепях обратной связи которо2го включены последовательно соединенные конденсатор и ключ, причем выход операционного усилителя подключен через ключ сброса к входу операционного усилителя, управляющие входы переключателя скорости, ключа сброса и объединенный управляющий вход ключей цепей обратной связи операционного усилителя являются соответствующими управляющими входами накопителя. k. Устройство по п. 1, о т л и чающееся тем, что анализатор состояния синхронизма выполнен в виде последовательно соединенных декодера, счетчика ошибок и триггера,выход которого подключен к одному из входов элемента И, выход которого подключен к установочному входу счетчика интервала синхронного состояния, вход которого соединен с выходом входного элемента И, один из входов которого объединен с входом формирователя интервала счета ошибок, выход которого через элемент задержки подключен к входу Уст-ановка нуля счетчика ошибок и триггера, причем к другому входу элемента И подключен выход формирователя интервала счета ошибок. Источники информации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР № 56035, кл. Н 0 L 11/08, 1976 (прототип).

Suff

ге

31

11-OH

3f

ьг9г

лг

ss

е

s /

фиг. 1

J

о «о

Авторы

Даты

1982-05-30—Публикация

1979-03-30—Подача