(54) АНАЛОГОВОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналоговое запоминающее устройство | 1982 |

|

SU1108509A1 |

| Аналоговое запоминающее устройство | 1979 |

|

SU822294A1 |

| Аналоговое запоминающее устройство | 1979 |

|

SU847374A1 |

| Аналоговое запоминающее устройство | 1980 |

|

SU875465A1 |

| Аналоговое запоминающее устройство | 1985 |

|

SU1300567A1 |

| Аналоговое запоминающее устройство | 1979 |

|

SU841057A1 |

| Аналоговое запоминающее устройство | 1990 |

|

SU1734123A1 |

| Аналоговое запоминающее устройство | 1983 |

|

SU1104586A1 |

| Аналоговое запоминающееуСТРОйСТВО | 1979 |

|

SU809391A1 |

| Аналоговое запоминающее устройство | 1981 |

|

SU970474A1 |

1

Изобретение относится к измерительной технике и может быть использовано в устройствах обработки аналоговых величин, а также в электрических измерительных преобразователях.

Известно аналоговое запоминающее устройство (АЗУ), содержащее операционный усилитель, ключ, буферный повторитель напряжения, ко входу которого подключен запоминающий конденсатор, а выход через резистор соединен со входом операционного усилителя fl .

Однако в таком устройстве точность хранения информации мала из-оа утечки заряда накопительного конденсатора.

Наиболее близким к предлагаемому яозляется АЗУ, содержащее компаратор, один из входов которого соединен со входом устройства, а другой - с выходом устройства и выходом буферного повторителя напряжения, вход которого подключен к одной из обкладок накопительного конденсатора и через ключ к выходу компаратора. Вторая обкладка конденсатора соединена с шийой нулевого потенциала 2.

Низкая точность хранения информаш1И в таком АЗУ обусловлена утечкой заряда с конденсатора через входное сопротивление буферного повторителя напряжения, сопротивление замкнутого ключа и сопро- Т1тление утечки самого конденсатора. Время хранения запоминаемой величины в этом АЗУ редко превьпиает несколько се10кунд.

Цель изобретения - повышение точности хранения устройства.

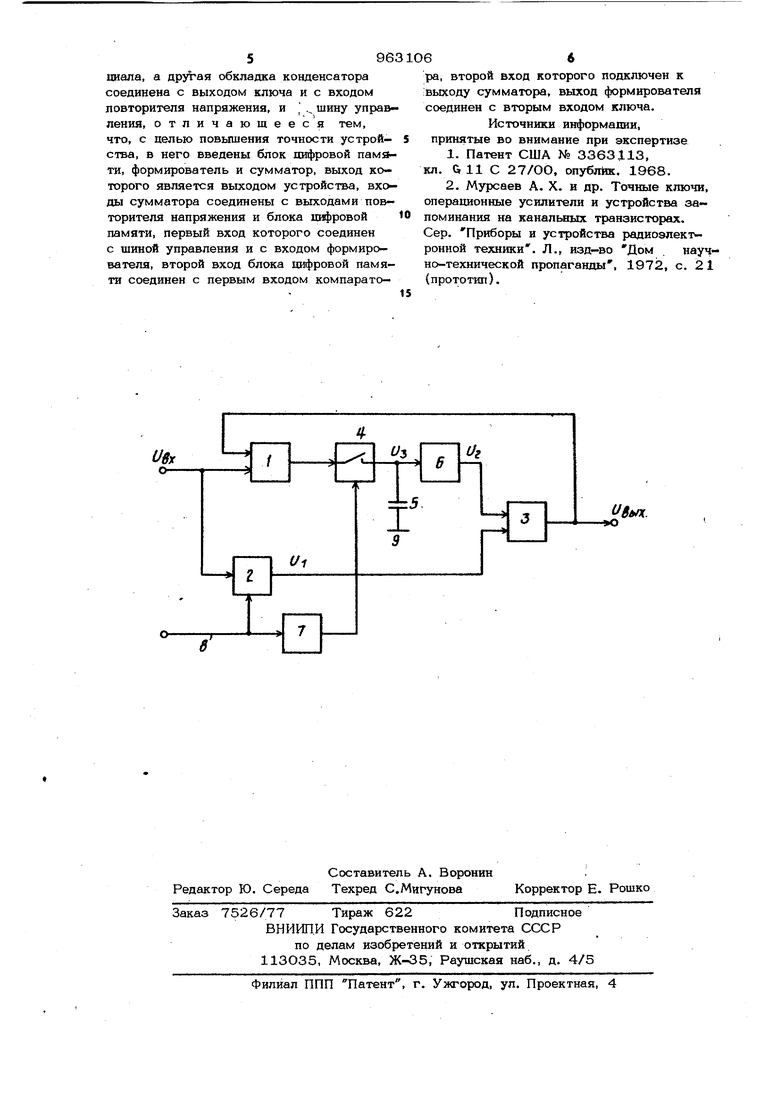

Поставленная цель достигается тем, что в аналоговое запоминающее устрой15ство, содержащее компаратор, первый вход которого является входом устройства, ключ, первый вход которого соединен с выходом компаратора, накопительный элемент, например конденсатор, одна из об20кладок которого соед1шена с шиной нулевого потенциала, а другая обкладка конденсатора соединена с выходом ключа и . с входом повторителя напряжения, и шину утфавления,. введены блок цифровой памяти, формирователь и суматор, выход ко торого является выходом устройства, вхо ды сумматора соединены с выходами повторителя напряжения и блока цифровой памяти, первый вход которого соединен с шиной управления и с входом формирователя, второй вход блока цифровой памяти соединен с первым входом компаратора ; второй вход которого подключен к выходу сумматора, выход формирователя соеди нен с вторым входом ключа. На чертеже изображена функциональная схема предлагаемого устройства. Устройство содержит компаратор 1, блок 2 цифровой памяти, сумматор 3, клю 4, накопительный элемент, например конденсатор 5, повторитель. 6 напряжения, формирователь 7, шину 8 управления, шину 9 нулевого потенциала. Устройство работает следующим образом. В начальный момент времени ключ 4 разомкнут. При подаче на шину 8 стро- бирующего импульса он вызьюает вначале сброс, а затем запуск блока 2 цифровой памяти. При этом блок 2 генерирует напряжение Ступенчатой.формы. Когда уровень очередной ступеньки достигает уровня входного сигналй, блок 2 переходит в режим Хранение. При этом на , выходе блока 2 устанавливается сигнал и иц,±ли/2 ли - величина ступеньки квантова- ния выходного напряжения бло ка 2 цифровой памяти. Величина uU определяется количеством разрядов п блока 2 и динамичес КИМ диапазоном входного сигнала Вх,идкс. BX.MUH. Д Вхмакс . мин. -соответственно максимальное и минимальное значения входного сигнала. После перехода блока 2 в режим Хра нение с выхода формирователя 7 на второй вход ключа поступает импульс, переводящий ключ 4 в замкнутое состояние. При этом замыкается контур отридательной обратной связи устройства и конденсатор 5 заряжается до тех пор, пЪка выходное напряжение устройства дости,гает уровня входного напряжения .где U2 - выходное напряжение повторителя 6 напряжения; k,K - коэффициенты передачи сумматора 3 соответственно по первому и второму входам. После окончания управляющего импульса ключ 4 размыкается и устройство переходит в режим Хранение. При условии, что коэффициент усиления компаратора 1 достаточно большая величина и коэффициенты передачи повторителя 6 напряжения и сумматора 3 по второму входу равны единице, на конденсаторе 5 устанавливается следующее напряжение UBX-. (4) -IK/ При этом величина К определяется величиной &(J и максимально допустимым выходным напряжением повторителя 6 напряжения . Например, при Ugx макс вх.мин -5 В; 11 8 макс +1ОВ на основании формуль (2) ди 39,06мВ, а на основании формулы (5) К / 1,95х хЮ , что намного меньше единицы. Благодаря тому, что коэффициентъ передачи сумматора 3 по первому и второму входам выбираются так, чтобы 1, 1, а 1 1, из формулы (3) следует, что основная доля выходного напряжения устройства хранится с высокой точностью в блоке 2 цифровой памяти, определяемой высокой стабильностью ее элементов, и как следствие из этого - влияние утечки заряда конденсатора 5 на точность хранения информа1ши устройства уменьшается в Ue,, раз. Смещение нуля повторителя 6 напряжения и сумматора 3 не влияют на точность работы устройства, так как они включены в контуре отридательной обратной связи компаратора 1, имеющего большой коэффициент усиления. Формула изобретения Аналоговое запоминающее устройство, содержащее компаратор, первый вход которого является входом устройства, ключ, первый вход которого соединен с выходом омпаратора, накопительный элемент, наример конденсатор, одна из обкладок которого соединена с шиной нулевого потенциала, а другая обкладка конденсатора соединена с выходом ключа и с входом повторителя напряжения, и , . шину управления, отличающееся тем, что, с целью повышения точности устрой- ства, в него введены блок дифровой памяти, формирователь и сумматор, выход которого является выходом устройства, входы сумматора соединены с выходами повторителя напряжения и блока цифровой памяти, первый вход которого соединен с шиной управления и с входом формирователя, второй вход блока хшфровой памяти соединен с первым входом компаратора, второй вход которого подключен к выходу сумматора, выход формирователя соединен с вторым входом ключа.

Источники информации, принятые во внимание при экспертизе

Авторы

Даты

1982-09-30—Публикация

1981-03-06—Подача