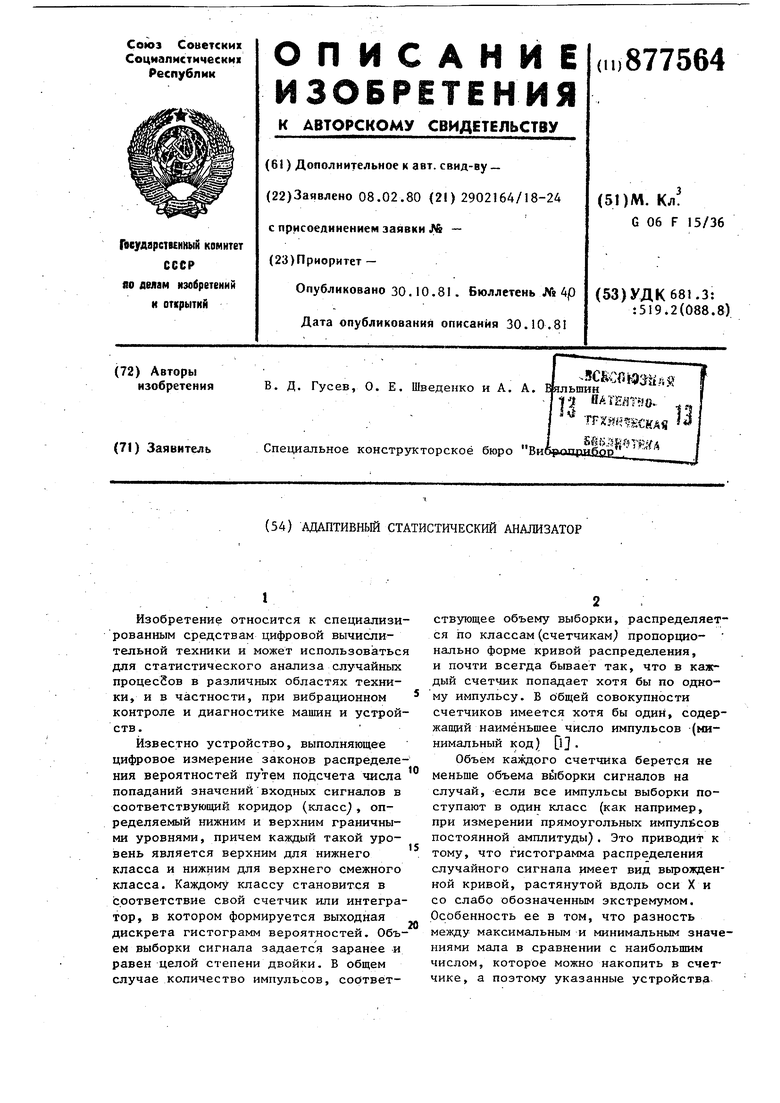

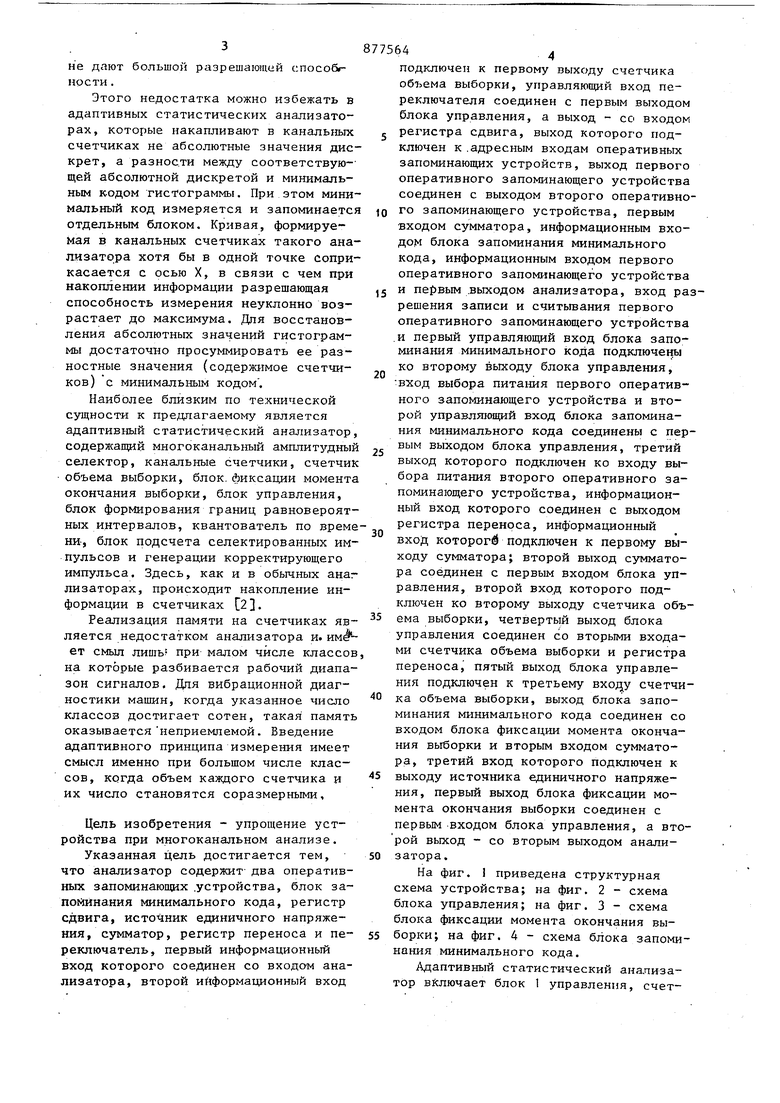

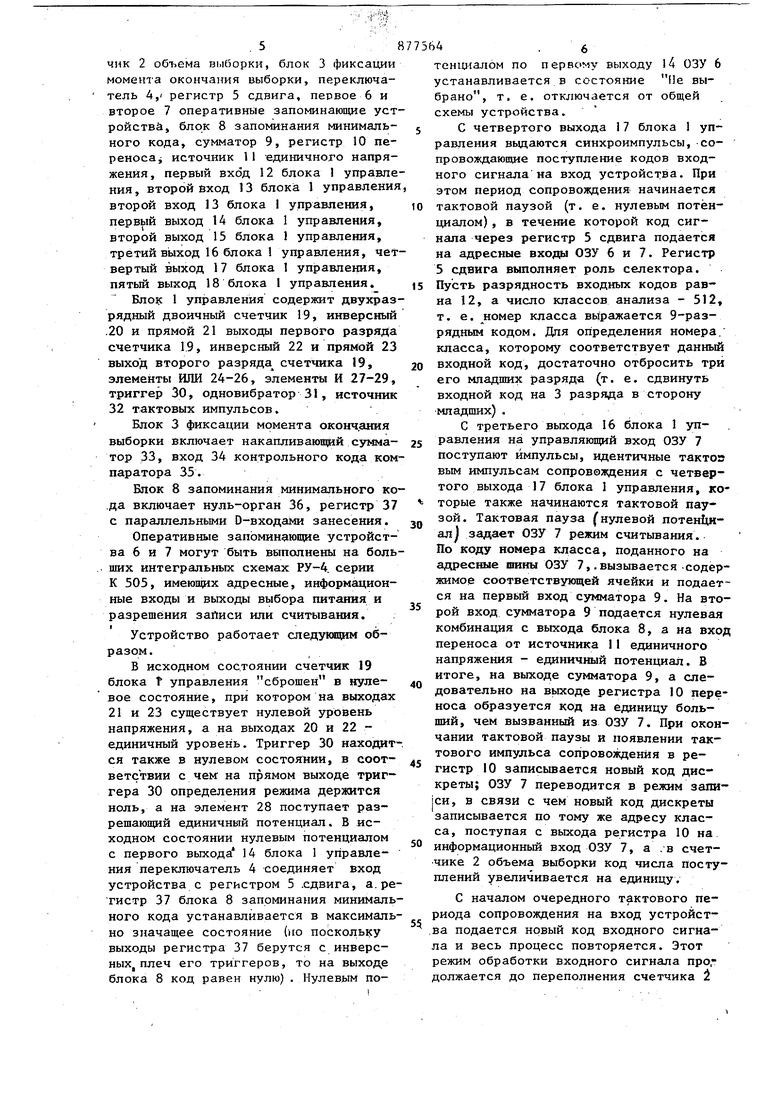

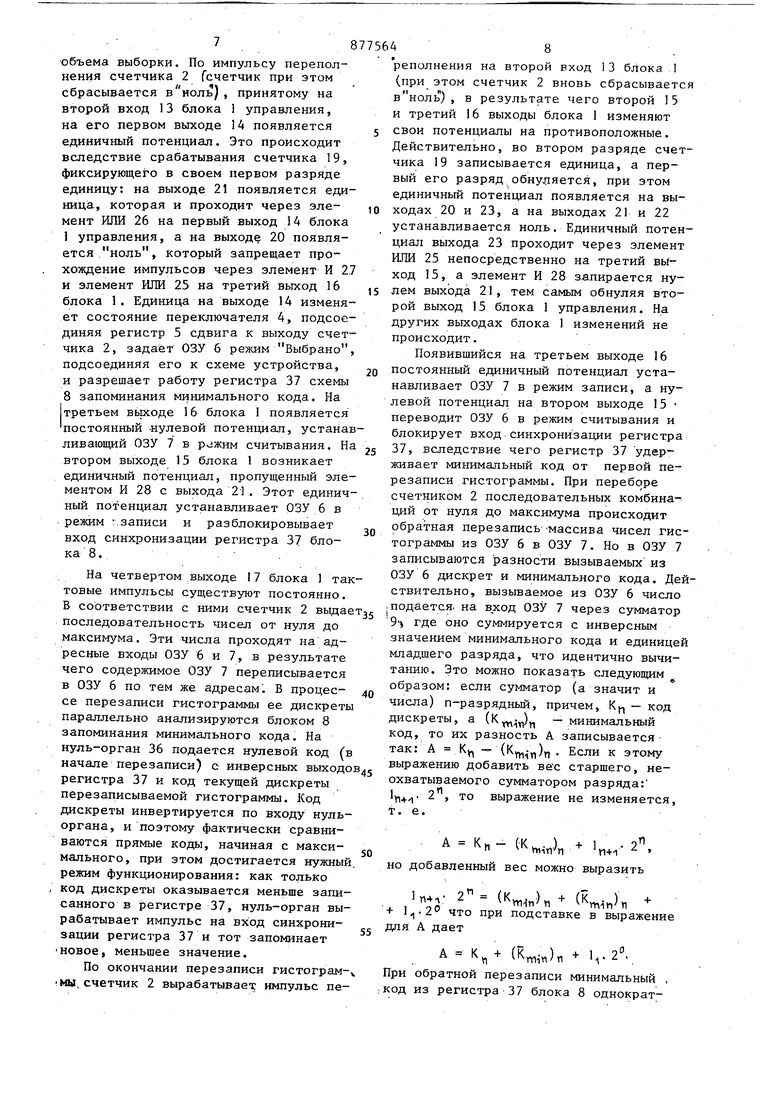

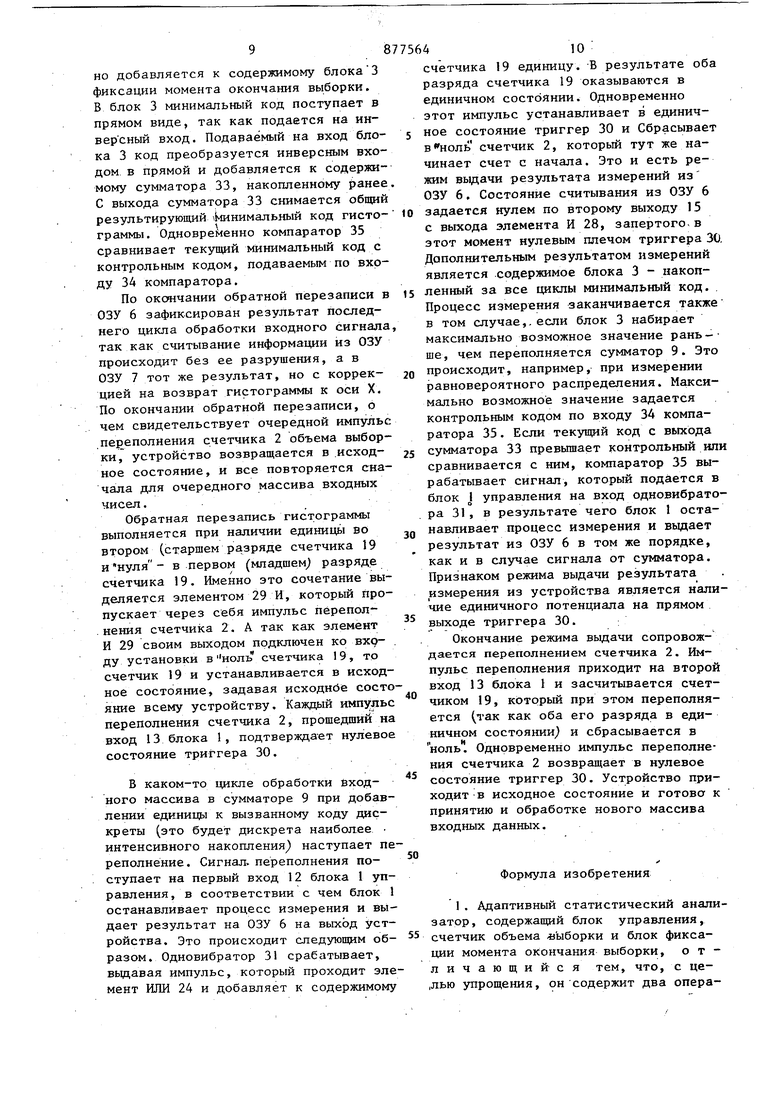

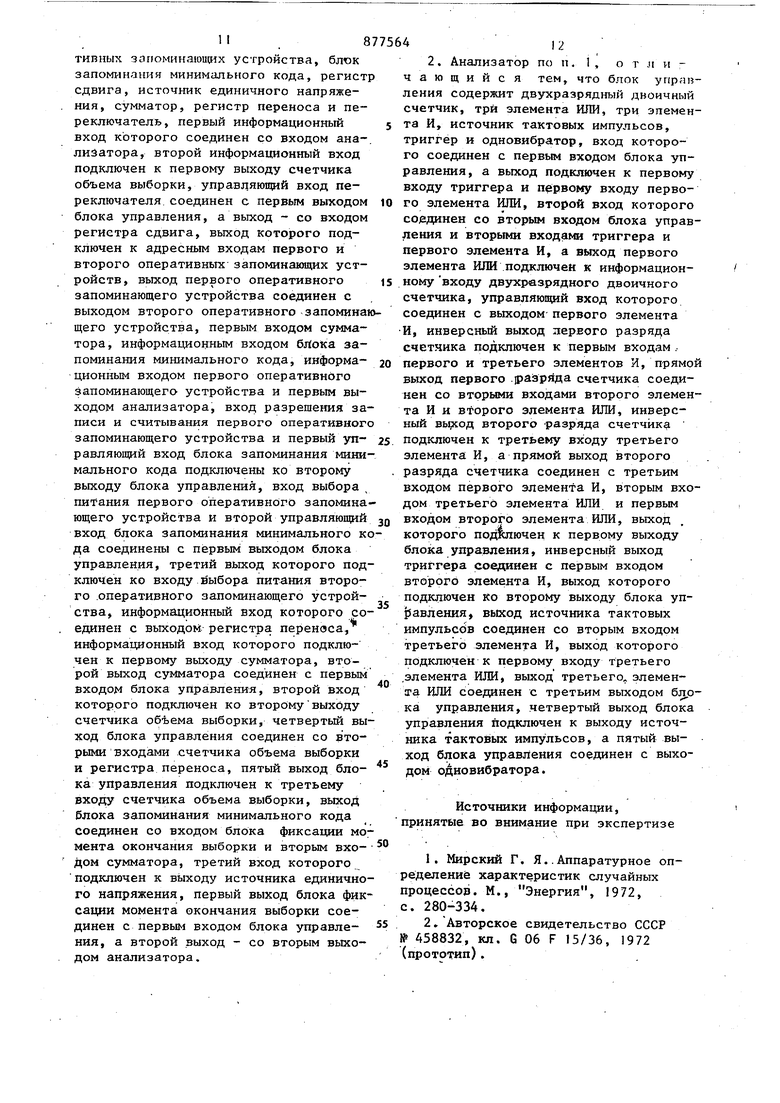

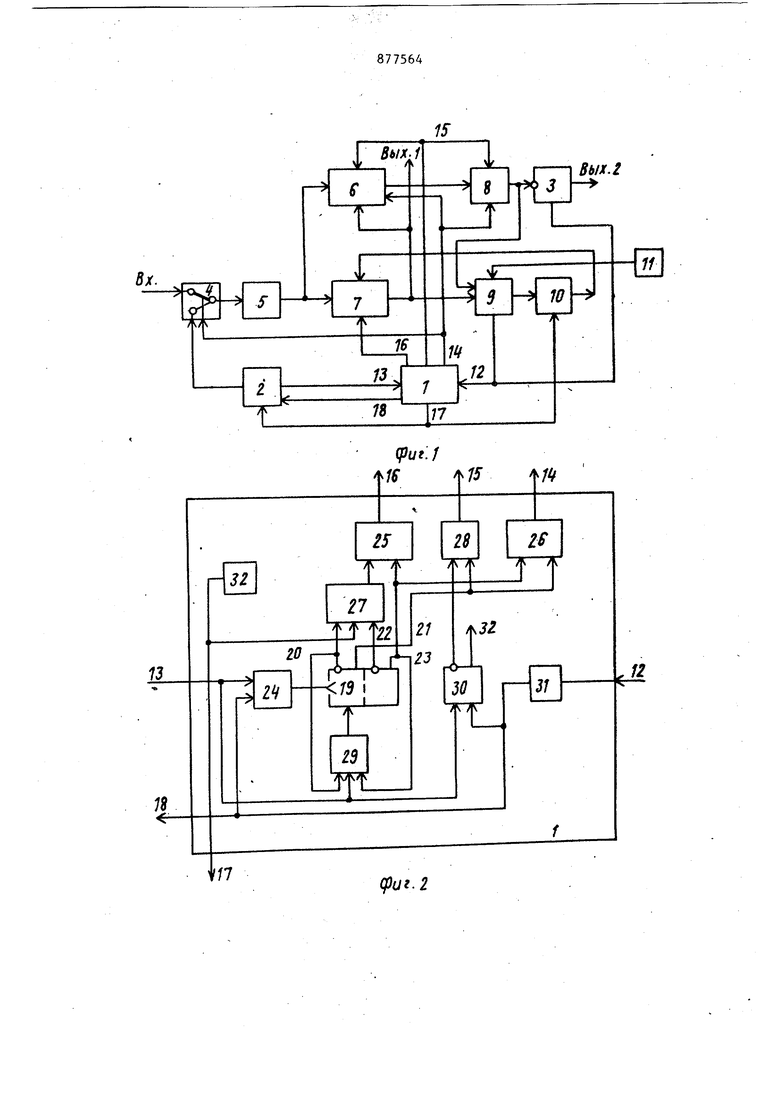

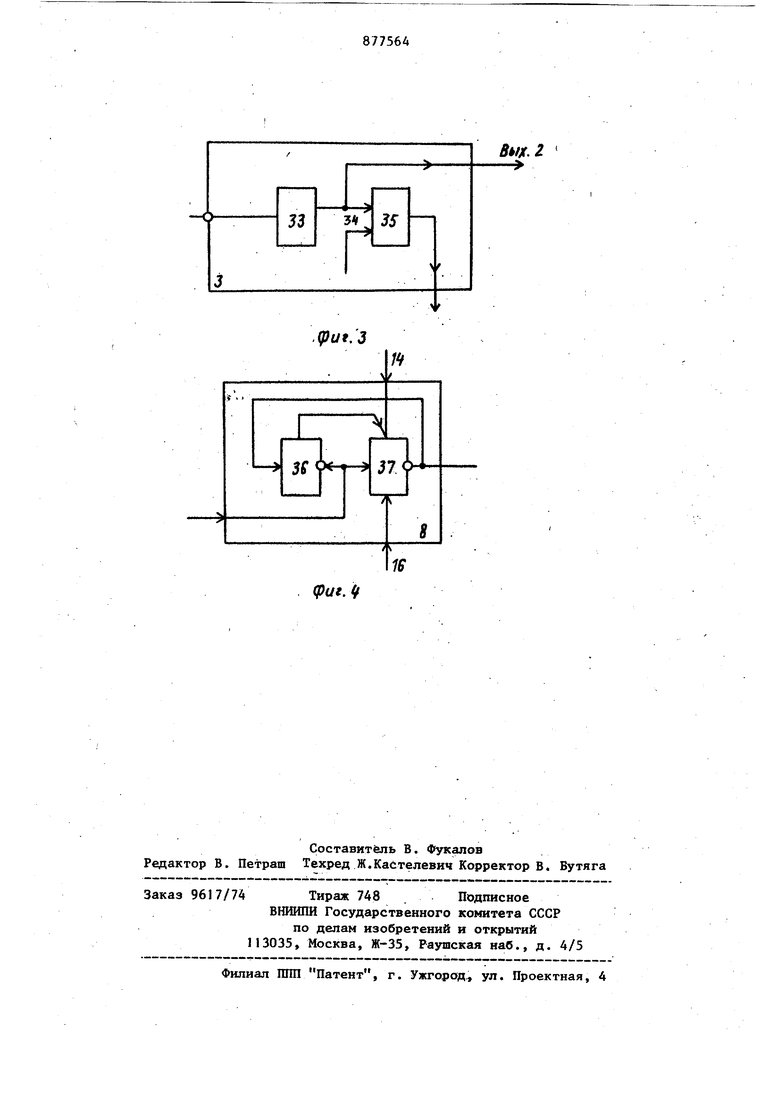

Изобретение относится к специализированным средствам цифровой вычислительной техники и может использоваться для статистического анализа случайных процессов в различных областях техники, и в частности, при вибрационном контроле и диагностике машин и устройств. Известно устройство, выполняющее цифровое измерение законов распределения вероятностей путем подсчета числа попаданий значений входных сигналов в соответствующий коридор (класс, определяемый нижним и верхним граничными уровнями, причем каждый такой уровень является верхним для нижнего класса и нижним для верхнего смежного класса. Каждому классу становится в соответствие свой счетчик или интегратор, в котором формируется выходная дискрета гистограмм вероятностей. Объем выборки сигнала задается заранее -и равен целой степени двойки. В общем случае количество импульсов, соответствующее объему выборки, распределяется по классам (счетчикам пропорционально форме кривой распределения, и почти всегда бывает так, что в казкдый счетчик попадает хотя бы по одному импульсу. Б общей совокупности счетчиков имеется хотя бы один, содержащий наименьшее число импульсов -(минимальный код) Qj. Объем каждого счетчика берется не меньше объема выборки сигналов на случай, если все импульсы выборки поступают Б один класс (как например, при измерении прямоугольных импулйсов постоянной амплитуды). Это приводит к тому, что гистограмма распределения случайного сигнапа имеет вид вырожденной кривой, растянутой вдоль оси X и со слабо обозначенным экстремумом. Особенность ее в том, что разность между максимальным и минимальным значениями мала в сравнении с наибольшим числом, которое можно накопить в счетчике, а поэтому указанные устройству не дают большой разрешающей епособ ности. Этого недостатка можно избежать в адаптивных статистических анализаторах, которые накапливают в канальных счетчиках не абсолютные значения дискрет, а разности между соответствующей абсолютной дискретой и минимальным кодом гистограммы. При этом минимальный код измеряется и запоминается отдельным блоком. Кривая, формируемая в канальных счетчиках такого анализатора хотя бы в одной точке соприкасается с осью X, в связи с чем при накоплении информации разрешающая способность измерения неуклонно возрастает до максимума. Для восстановления абсолютных значений гистограммы достаточно просуммировать ее разностные значения (содержимое счетчиков) с минимальным кодом . Наиболее близким по технической сущности к предлагаемому является адаптивный статистический анализатор, содержащий многоканальный амплитудный селектор, канальные счетчики, счетчик объема выборки, блок, фиксации момента окончания выборки, блок управления, блок формирования границ равновероятных интервалов, квантователь по време ни-, блок подсчета селектированных импульсов и генерации корректирующего импульса. Здесь, как и в обычных анаг лизаторах, происходит накопление информации в счетчиках 2 . Реализация памяти на счетчиках является недостатком анализатора и име ет смыл лишь при малом числе классов на которые разбивается рабочий диапазон сигналов. Для вибрационной диагностики машин, когда указанное число классов достигает сотен, такая память оказывается неприемлемой. Введение адаптивного принципа измерения имеет смысл именно при большом числе классов, когда объем каждого счетчика и их число становятся соразмерными. Цель изобретения - упрощение устройства при многоканальном анализе. Указанная цель достигается тем, что анализатор содержит два оперативных запоминаюпщх .устройства, блок запоминания минимального кода, регистр сдвига, источник единичного напряжения , сумматор , регистр переноса и переключатель, первый информационный вход которого соединен со входом анализатора, второй информационный вход 44 подключен к первому выходу счетчика объема выборки, управляющий вход переключателя соединен с первым выходом блока управления, а выход - со входом регистра сдвига, выход которого подключен к .адресным входам оперативных запоминающих устройств, выход первого оперативного запоминающего устройства соединен с выходом второго оперативного запоминающего устройства, первым входом сумматора, информационным входом блока запоминания минимального кода, информационным входом первого оперативного запоминающего устройства и первым .выходом анализатора, вход разрешения записи и считьгеания первого оперативного запоминающего устройства и первый управляющий вход блока запоминания минимального кода подключены ко второму выходу блока управления, :вход выбора питания первого оперативного запоминающего устройства и второй управляющий вход блока запоминания минимального кода соединены с первым выходом блока управления, третий выход которого подключен ко входу выбора питания второго оперативного запоминающего устройства, информационный вход которого соединен с выходом регистра переноса, информационный вход которогЙ подключен к первому выходу сумматора; второй выход сумматора соединен с первым входом блока управления, второй вход которого подключен ко второму выходу счетчика объема выборки, четвертый выход блока управления соединен со вторыми входами счетчика объема выборки и регистра переноса, пятый выход блока управления подключен к третьему счетчика объема выборки, выход блока запоминания минимального кода соединен со входом блока фиксации момента окончания выборки и вторым входом сумматора, третий вход которого подключен к выходу источника единичного напряжения, первый выход блока фиксации момента окончания выборки соединен с первым входом блока управления, а второй выход - со вторым выходом анализатора. На фиг. 1 приведена структурная схема устройства; на фиг. 2 - схема блока управления; на фиг. 3 - схема блока фиксации момента окончания выборки; на фиг. 4 - схема блока запоминания минимального кода. Адаптивный статистический анализатор включает блок 1 управления, счет.5 чик 2 объема выборки, блок 3 фиксации момента окончания выборки, переключатель 4, регистр 5 сдвига, первое 6 и второе 7 оперативные запоминаюпще уст ройстве, блок 8 запоминания минимального кода, сумматор 9, регистр 10 переноса источник 1 1 -единичного напряжения, первый вход 12 блока управле ния, второй 6ХОД 13 блока 1 управления второй вход 13 блока 1 управления, первый выход 14 блока 1 управления, второй выход 15 блока 1 управления, третий выход 16 блока 1 управления, чет вертый выход 17 блока 1 управления, пятый выход 18 блока 1 управления. Блок 1 управления содержит двухраз рядный двоичный счетчик 19, инверсный .20 и прямой 21 выходы первого разряда счетчика 19, инверсный 22 и прямой 23 выход второго разряда счетчика 19, элементы ШШ 24-26, элементы И 27-29, триггер 30, одновибратор 31, источник 32 тактовых импульсов, Блок 3 фиксации момента окончания выборки включает накапливающий сумматор 33, вход 34 контрольного кода ком паратора 35. Блок 8 запоминания минимального ко .да включает нуль-орган 36, регистр 37 с параллельными О-входами занесения. Оперативные запоминающие устройства 6 и 7 могут быть выполнены на боль ших интегральных схемах РУ-4. серии К 505, имеющих адресные, информационные входы и выходы выбора питания и разрешения зайиси или считывания. I . Устройство работает следукщим образом. В исходном состоянии счетчик 19 блока I управления сброшен в нулевое состояние, при котором на выходах 21 и 23 существует нулевой уровень напряжения, а на выходах 20 и 22 единичный уровень. Триггер 30 находит ся также в нулевом состоянии, в соответствии с чек на прямом выходе триггера 30 определения режима держится ноль, а на элемент 28 поступает разрешающий единичный потенциал. В исходном состоянии нулевым потенциалом с первого выхода 14 блока 1 управления переключатель 4 соединяет вход устройства с регистром 5 .сдвига, а.ре тистр 37 блока 8 запоминания минималь ного кода устанавливается в максималь но значащее состояние (но поскольку выходы регистра 37 берутся с инверсных, плеч его триггеров, то на выходе блока 8 код равен нулю). Нулевым по4, 6 тенциалом по первому выходу 14 ОЗУ 6 устанавливается в состояние Не выбрано, т. е. отключается от общей схемы устройства. С четвертого выхода 17 блока 1 управления вьщаются синхроимпульсы, сопровождающие поступление кодов входного сигналана вход устройства. При этом период сопровождения начинается тактовой паузой (т. е. нулевым потенциалом) , в течение которой код сигнала через регистр 5 сдвига подается на адресные входы ОЗУ 6 и 7. Регистр 5 сдвнга выполняет роль селектора. Пусть разрядность входных кодов равна 12, а число классов анализа - 512, т. е, номер класса выражается 9-разрядным кодом. Для определения номера, класса, которому соответствует входной код, достаточно отбросить три его младших разряда (т. е. сдвинуть входной код на 3 разряда в сторону младших) . . С третьего выхода 16 блока 1 управления на управляющий вход ОЗУ 7 поступают импульсы, идентичные тактоз вым импульсам сопровеяздения с четвертого выхода 17 блока 1 управления, которые также начинаются тактовой пауЗОЙ. Тактовая пауза (нулевой потен1шал задает ОЗУ 7 режим считывания. По коду номера класса, поданного на адресные шины ОЗУ 7,,вызывается содержимое соответствующей ячейки и подается на первый вход сумматора 9. На второй вход сумматора 9 подается нулевая комбинация с выхода блока 8, а на вход переноса от источника 1I единичного напряжения - единичный потенциал. В итоге, на выходе сумматора 9, а следовательно на выходе регистра 10 переноса образуется код на единицу больший, чем вызванный из ОЗУ 7. При окончании тактовой паузы и появлении тактового импульса сопровождения в регистр 10 записьшается новый код дискреты; ОЗУ 7 переводится в режим записи, в связи с чем новый код дискреты записывается по тому же адресу класса, поступая с выхода регистра 10 на информационный вход ОЗУ 7, а .в счетчике 2 объема выборки код числа поступлений увеличивается на единицу. С началом очередного тактового пеиода сопровождения на вход устройста подается новый код входного сигнаа и весь процесс повторяется. Этот ежим обработки входного сигнала проолжается до переполнения счетчика i объема выборки. По импульсу переполнения счетчика 2 Гсчетчик при этом сбрасывается ), принятому на второй вход 3 блока 1 управления, на его первом выходе 4 появляется единичный потенциал о Это происходит вследствие срабатывания счетчика 19, фиксирующего в своем первом разряде единицу: на выходе 21 появляется единица, которая и проходит через элемент ИЛИ 26 на первый выход 14 блока 1 управления, а на выходе 20 появляется ноль, который запрещает прохождение импульсов через элемент И 2.7 и элемент ИЛИ 25 на третий выход 16 блока . Единица на выходе 14 изменяет состояние переключателя 4, подсоединяя регистр 5 сдвига к выходу счетчика 2, задаёт ОЗУ б режим Выбрано подсоединяя его к схеме устройства, и разрешает работу регистра 37 схемы 8 запоминания минимального кода. На третьем вьрсоде 16 блока 1 появляется постоянный -нулевой потенциал, устанав ливающий ОЗУ 7 в рчгжим считывания. Н втором выходе 15 блока 1 возникает единичный потенциал, пропущенный элементом И 28 с выхода 2-1 . Этот единич ный потенциал устанавливает ОЗУ 6 в режим : записи и разблокировывает вход синхронизации регистра 37 блока 8 . На четвертом выходе 17 блока 1 так товые импульсы существуют постоянно. В соответствии с ними счетчик 2 выда последовательность чисел от нуля до максимума. Эти числа проходят на адресные входы ОЗУ 6 и 7, в результате чего содержимое ОЗУ 7 переписывается в ОЗУ 6 по тем же адресам . В процессе перезаписи гистограм1«1ы ее дискреты параллельно анализиру1ртся блоком 8 запоминания минимального кода. На нуль-орган 36 подается нулевой код (в начале перезаписи) с инверсных выходо регистра 37 и код текущей дискреты перезаписываемой гистограммы. Код дискреты инвертируется по входу нуль органа, и поэтому фактически сравниваются прямые коды, начиная с максимального, при этом достигается нужны режим функционирования: как только код дискреты оказывается меньше записанного в регистре 37, нуль-орган вы рабатывает импульс на вход синхронизации регистра 37 и тот запоминает новое, меньшее значение. По окончании перезаписи гистограм мы,счетчик 2 вырабатывает импульс переполнения на второй вход 13 блока 1 (при этом счетчик 2 вновь сбрасывается ) , в результате чего второй 15 и третий 16 выходы блока I изменяют свои потенциалы на противоположные. Действительно, во втором разряде счетчика 19 записывается единица, а первый его разряд обнуляется, при этом единичный потенциал появляется на выходах 20 и 23, а на выходах 21 и 22 устанавливается ноль. Единичный потенциал выхода 23 проходит через элемент ИЛИ 25 непосредственно на третий выход 15, а элемент И 28 запирается нулем выхода 21, тем самым обнуляя второй выход 15 блока 1 управления. На других выходах блока 1 изменений не происходит. Появившийся на третьем выходе 16 постоянный единичный потенциал устанавливает ОЗУ 7 в режим записи, а нулевой потенциал на втором выходе 15 переводит ОЗУ 6 в режим считывания и блокирует вход синхронизации регистра 37, вследствие чего регистр 37 удерживает минимальный код от первой перезаписи гистограммы. При переборе счетником 2 последовательных комбинаций от нуля до максимума происходит обратная перезапись-массива чисел гистограммы из ОЗУ 6 в ОЗУ 7. Но в ОЗУ 7 записываются разности вызываемых из ОЗУ 6 дискрет и минимального кода. Действительно, вызываемое из ОЗУ 6 число подается, на вход ОЗУ 7 через сумматор 9 где оно суммируется с инверсным значением минимального кода и единицей младшего разряда, что идентично вычитанию. Это можно показать следующим 7 образом: если сумматор (а значит и числа) п-разрядный, причем, К| - код дискреты, а (К) -минимальный код, то их разность А записывается так: А К, - () . Если к этому выражению добавить вес старшего, неохватываемого сумматором разряда: Ц. 2 , то выражение не изменяется, Т. е. A Kh- (К,Л т.- 2. но добавленный вес можно выразить . , ()«+ (.)i + 1 2 что при подставке в выражение для А дает А {К.„)„ -f Ц.2 При обратной перезаписи минимальный , код из регистра 37 блока 8 однократно добавляется к содержимому блока3 фиксации момента окончания выборки. В блок 3 минимальный код поступает в прямом виде, так как подается на инверсный вход. Подаваемый на вход блока 3 код преобразуется инверсным входом в прямой и добавляется к содержимому сумматора 33, накопленному ранее С выхода сумматора 33 снимается общий результирующий Минимальный код гистограммы. Одноврейенно компаратор 35 сравнивает текущий минимальный код с контрольным кодом, подаваемым по входу 34 компаратора. По окончании обратной перезаписи в ОЗУ 6 зафиксирован результат последнего цикла обработки входного сигнала так как считывание информации из ОЗУ происходит без ее разрушения, а в ОЗУ 7 тот же результат, но с коррекцией на возврат гистограммы к оси X. По окончании обратной перезаписи, о чем свидетельствует очередной импульс переполнения счетчика 2 объема выборки, устройство возвращается в .исходкое состояние, и все повторяется сначала для очередного массива входных чисел. Обратная перезапись гистограммы выполняется при наличии единиць во втором (старшем разряде счетчика 19 инуля - в первом (младшем разряде счетчика 19. Именно это сочетание выделяется элементом 29 И, который пропускает через себя импульс пёрепол.нения счетчика 2. А так как элемент И 29 своим выходом подключен ко вхрду установки счетчика 19, то счетчик 19 и устанавливается в исходное состояние, задавая исходное состо яние всему устройству. Каждый импульс переполнения счетчика 2, прошедший на вход 13 блока 1, подтверждает нулевое состояние триггера 30. В каком-то цикле обработки Входного массива в сумматоре 9 при добавлении единицы к вызванному коду wicкреты (это будет дискрета наиболее интенсивного накопления наступает пе реполнение. Сигнал, переполнения поступает на первый вход 12 блока 1 управления, в соответствии с чем блок 1 останавливает процесс измерения и выдает результат на ОЗУ 6 на выход устройства. Это происходит следующим образом. Одновибратор 31 срабатывает, выдавая импульс, который проходит эле мент ИЛИ 24 и добавляет к содержимому 410 счетчика 19 единицу. В результате оба разряда счетчика 19 оказываются в единичном состоянии. Одновременно этот импульс устанавливает в единичное состояние триггер 30 и Сбрасывает в ноль счетчик 2, который тут же начинает счет с начала. Это и есть режим выдачи результата измерений из ОЗУ 6. Состояние считывания из ОЗУ 6 задается нулем по второму выходу 15 с выхода элемента И 28, запертого-в этот момент нулевым плечом триггера 30, Дополнительным результатом измерений является содержимое блока 3 - накопленный за все циклы минимальный код. Процесс измерения заканчивается также в том случае,, если блок 3 набирает максимально возможное значение рань- ше, чем переполняется сумматор 9. Это происходит, например, при измерении равновероятного распределения. Максимально возможное значение задается контрольным кодом по входу 34 компаратора 35. Если текущий код с выхода сумматора 33 превышает контрольный или сравнивается с ним, компаратор 35 вырабатывает сигнал, который подается в блок J управления на вход одновибратора 31, в результате чего блок 1 останавливает процесс измерения и вьщает результат из ОЗУ 6 в том же порядке, как и в случае сигнала от сумматора. Признаком режима выдачи результата измерения из устройства является наличие единичного потенциала на прямом выходе триггера 30. Окончание режима выдачи сопровождается переполнением счетчика 2. Импульс переполнения приходит на второй вход 13 блока 1 и засчитывается счетчиком 19, который при этом переполняется (так как оба его разряда в единичном состоянии) и сбрасывается в ноль. Одновременно импульс переполнения счетчика 2 возвращает в нулевое состояние триггер 30. Устройство приходит -в исходное состояние и готово к принятию и обработке нового массива входных данных. Формула изобретения 1. Адаптивный статистический анализатор, содержащий блок управления, счетчик объема аыборки и блок фиксации момента окончания выборки, отичающийся тем, что, с цеью упрощения, онсодержит два опера11. 8 типных заг1омииаюи нх устройства, блок запоминания минимального кода, регист сдвига, источник единичного напряжения, сумматор, регистр переноса и переключатель, первый информационный вход которого соединен со входом anaлизатора, второй информационный вход подключен к первому выходу счетчика объема выборки, управляющий вход переключателя, соединен с первым выходом блока управления, а выход - со входом регистра сдвига, выход которого подключен к адресным входам первого и второго оперативных запоминающих устройств, выход первого оперативного запоминающего устройства соединен с выходом второго оперативного запомина щего устройства, первым входом сумматора, информационным входом блока запоминания минимального кода, информационным входом первого оперативного запоминающего устройства и первым выходом анализатора, вход разреше1шя за писи и считывания первого оперативног запоминающего устройства и первый уп- 25. равляющий вход блока запоминания мини мального кода подключены ко второму выходу блока управления, вход выбора питания первого оперативного запомина ющего устройства и второй управляющий вход блока запоминания минимального к да соединены с первым выходом блока управления, третий выход которого под ключен ко входу выбора питания второго .оперативного запоминающего устройства, информационный вход которого со единен с выходом регистра nepeHcsca, информационный вход которого подключен к первому выходу сумматора, второй выход сумматора соединен с первым входом блока управления, второй вход которого подключен ко второмувыходу счетчика объема выборки, четвертый вы ход блока управления соединен со вторыми входами .счетчика объема выборки и регистра переноса, пятый выход блока управления подключен к третьему входу счетчика объема выборки, выход блока запоминания минимального кода соединен со входом блока фиксации мо мента окончания выборки и вторым входом сумматора, третий вход которого подключен к выходу источника единично го напряжения, первый выход блока фик сации момента окончания выборки соединен с первым входом блока управления, а второй выход - со вторым выходом анализатора. 4 2. Анализатор по п. 1, о т л и чающийся тем, что блок управления содержит двухразрядный двоичный счетчик, три элемента ИЛИ, три эпемента И, источник тактовых импульсов, триггер и одновибратор, вход которого соединен с первым входом блока управления, а выход подключен к первому входу триггера и первому входу первого элемента ИЛИ, второй вход которого соединен со вторым входом блока управления и вторыми входами триггера и первого элемента И, а выход первого элемента ИЛИ подключен к информационномувходу двзгхразрядного двоичного счетчика, управляющий вход которого соединен с выходом первого элемента И, инверсный выход лервого разряда счетника подключен к первым входам .. первого и третьего элементов И, прямой выход первого .разряда счетчика соединен со вторыми входами второго элемента И и второго элемента ИЛИ, инверсный вькод второго разряда счетчику подключен к третьему входу третьего элемента И, а прямой выход второго разряда счетчика соединен с третьим входом первого элемента И, вторым входом третьего элемента ИЛИ и первым входом второго элемента ИЛИ, вьгход которого подключен к первому выходу блока управления, инверсный выход триггера соединен с первым входом второго элемента И, выход которого подключен ко второму выходу блока уп15авления, выход источника тактовых импульсов соединен со вторым входом третьего элемента И, выход которого подключен к первому входу третьего .элемента ИЛИ, выход третьего,, элемента ИЛИ соединен с третьим выходом блока управления, четвертый выход блока управления подключен к выходу источника тактойых импульсов, а пятый выход блока управления соединен с выходом одновибратора. Источники информации, принятые во внимание при экспертизе I. Мирский Г. Я..Аппаратурное определение характеристик случайных процессоэ. М., Энергия, 1972, с. 280-334. 2 Авторское свидетельство СССР № 458832, кл. G 06 F 15/36, 1972 (прототип).

Вых. 2

| название | год | авторы | номер документа |

|---|---|---|---|

| СТАТИСТИЧЕСКИЙ АНАЛИЗАТОР ОТКЛОНЕНИЙ НАПРЯЖЕНИЯ | 1992 |

|

RU2041497C1 |

| Параллельный статистический анализатор отклонений и колебаний напряжения | 1982 |

|

SU1076913A1 |

| Статистический анализатор отклонений напряжения | 1981 |

|

SU993469A1 |

| Устройство для измерения электромагнитных параметров объемных экранов | 1983 |

|

SU1228150A1 |

| Цифровой статистический анализатор случайных интервалов времени | 1980 |

|

SU943745A1 |

| СТАТИСТИЧЕСКИЙ АНАЛИЗАТОР | 2000 |

|

RU2208836C2 |

| МНОГОМЕРНЫЙ СТАТИСТИЧЕСКИЙ АНАЛИЗАТОР УСРЕДНЕННОЙ МОЩНОСТИ НЕСТАЦИОНАРНОЙ НАГРУЗКИ | 1992 |

|

RU2060542C1 |

| Устройство для непрерывного экспресс-анализа потоков случайных чисел | 1983 |

|

SU1101839A1 |

| Статистический анализатор отклонений напряжения сети | 1985 |

|

SU1262524A1 |

| Анализатор спектра случайныхпРОцЕССОВ | 1979 |

|

SU838600A1 |

(риг. 2

О

gjut.d

(риг. If

Buf. 2 -

Авторы

Даты

1981-10-30—Публикация

1980-02-08—Подача