(54) ЦИФРОВОЙ СТАТИСТИЧЕСКИЙ АНАЛИЗАТОР СЛУЧАЙНЫХ ИНТЕРВАЛОВ ВРЕМЕНИ

1

Изобретение относится к вычиспитепьной технике и может быть использовано для опредепения закона распределения периода случайной импульсной поспедовательности и, в частности, для определения закона распределения периода пупьса (R-R интервалов) при медико-биологических исследованиях.

Известен измеритель интервалов вреMesHH, содержащий квантующий генератор, Логическую схему, счетчик и устройство управпения, и позволяет измерять длительность интервалов времени QL .

Автоматическая статистическая обработка ре льтатов измерения в том чис- ,5 ле, определение закона распределения:

таким прибором невозможно.

Наиболее близким техническим решением к изобретению является цифровой статистический анализатор случайных ин- 20 тервалов времени, содержащий два измерительных канала, состоящих из счетчика, трех схем И и триггера, счетчик, блок запуска, состоящий из схемы И триггера и счетчика, блок переключения, содерокаший две схемы И и триггер, две схемы ИЛИ, блок схем И, бпок задания положения зоны селекции, содержащий счетчик, схему И и триггер 2j.

Недостаток устройства состоит в низком быстродействии, посколыдг в течение одной выборки осуществляется получение результата только для одного интервала гистограммы.

Цель изобретения - повьоиение бысг родейстзшя.

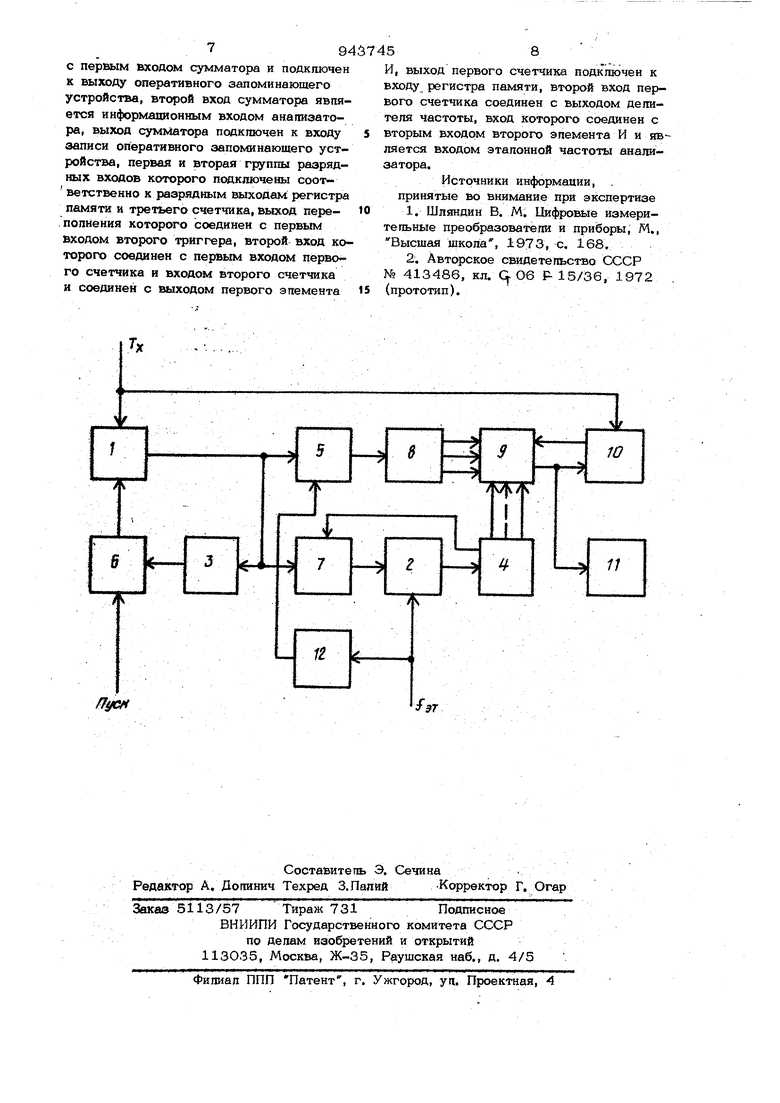

Эта цель достигается , что в цифровой статистический анализатор случайных интерваж в времени, содержащим первый счетчик, первый триггер, первый вход которого является входом Пуск анапизатора, выход первого триггера соединен с пербьтм хжодом первого элемента И, второй вход которого явпяется информационным входом анализатора, второй вход первого триггера соединен с выходшл второго счетчика, вход котороРо соединен с выходом первого элемента И, второй триггер, выход которого подключен к первому входу второго элемента И, выход которого соединен с входом третьего счетчика, введены делитель частоты, регистр памяти, оперативное за поминающее устройство, сумматор и сдви говый регистр, вход которого объединен с первым входом сумматора и подключен к выходу оперативного запоминающего устройства, второй вход сумматора явпяется информационным входом анализатора, выход сумматора подключен к входу записи оперативного запоминающего устройства, первая и вторая группы разрядных входов которого подключены соответ ственно к разрядным выходам регистра памяти и третьего счетчика, выход переполнения которого соединен с первым входом второго триггера, второй вход которого объединен с первым входом первого и входом второго счетчика и Соединен с выходом первого элемента И, выход первого счетчика подключен к входу регистра памяти, второй вход первого счетчика соединен с выходом делителя частоты, вход которого объединен с вторым входом второго элемента И и является входом эталонной частоты анализатора. Сущность работы анализатора состоит в измерении длительности каждого периода в импульсном потоке и подсчете количества появлений периодов одинаковой длительности в интервале существования закона распределения, для чего используется оперативное запоминающее устрой ство (ОЗУ). ОЗУ должно обладать возмож ностью накопления болыиого количества многоразряднь1Х чисел, каждое из которы соответствует количеству появлений периодов опреде;ленной длительности. Этим требованиям отвечают широко выпускаемые промышленностью ОЗУ. Например, существуют ОЗУ, позволяющие накапливать 16 шестнадцатиразрядных слов в использованием строчно-столбаовой адресации. Каждое слово соответствует количеству появлений периодов определенной длительности. Цифровой эквивалент длительности периода определяется в соответствии с выражением ПгТх/0 01 где х длительность периода импульсного потока ОСд- период генератора импупьсов. Если, например., odо Ю м с, то дляТу с, П 50, для TX 0,5i с, П г51 и т.д. Дпя адресации используются коды, начиная с нулевого: 0000 (ад рес нулевой строки), 0001 (адрес перво строки), ОО10 (адрес второй строки) и Т. Д. Поэтому для того, чтобы поставить в соответствие длительности периода адрес строки, из каждого в рассмотренном примере необходимо вычесть 50. Это может быть достигнуто начальной установкой счетчика не на нуль, а на число, соответствующее двоичному представлению числа -50, т.е. fn )-.50): в двоичном представЕсли использовать для адресации все разряды Г)J то в первой строке ОЗУ (адрес ОООО) накапливается число, равное количеству появлений периодов с длительностью 0,5 с. Во второй строке, адрес которой 0001, накапливается число, равное количеству появления периодов с длительностью 0,51 с и т.д. Разрешающая способность в этом случае равна 0,01. Если испольовать для адресации разрядь п -со второго справа, то в первой строке с адресом ОООО накапливается число, равное количеству появлений периодов с длительностью (5-0, 51) с. Разрешающая способность при этом становится равной 0,02 с. Таким образом, используя для адресации различные разряды, можно варьировать разрешающую способность. На чертеже приведена схема цифрового статистического анализатора случайных интервалов времени, содержащая элементы И 1 и 2, счетчики 3, 4, 5, триг- . геры 6, 7, регистр 8 Памяти, ОЗУ 9, сумматор 10 и сдвиговый регистр 11, а также делитель 12 частоты. Анализатор работает следующим образом. По сигналу Пуск триггер 6 открывает элемент И 1, и импупьсы исследуемого потока начинают поступать в схему. Длина выборки ограничивается емкостью счетчика 3, так как при его переполнении триггер 6 возвращается в исходное состояние и процесс обработки информации заканчивается выводом инфор мации в сдвиговый регистр 11. Измерение длительности периода происходит следующим образом. Импугаьсы эталонной частоты поступают на счетный вход счетчика 5 через делитель 12 частоты непрерывно. В момент поступления импульса от элемента И 1 код числа, записанного в счетчик 5, переносится в регистр 8 памяти, где хранится до следующего обновления. Счетчик 5 после этого устанавливается на число - 5О в paiccMOTjDeHHOM примере и начинает снова пересчитывать импульсы эталонной часто ты, но уже в следующем периоде иссле- дуемого потока, как указывалось, код числа, установленного в регистре 8 памяти, является адресом строки оперативного запоми1 ающего устройства 9 к со держимому которой необходимо добавить единицу. Это значит, что произошло событие, количество которых накапливается в строке по адресу, снимаемому с регис ра 8. памяти. Увеличение числа, хранимо го в выбираемой строке, на единицу про- исходит следующим путем. Очередной им пульс исследуемого потока, по которому закончилось формирование в счетчике 5 кода минувшего периода, поступает на вход первого слагаемрго сумматора 1О. Счётчик 4 производит поразрядный вызов выбранной строки. Для состояния 0000счетчика 4 ко второму входу сумматора 10 подключается первая ячейка выбранной строки. Если в этой ячейке за писан нуль, то на выходе сумматора 10 появляется единица, которая и записывается в первую ячейку. В случае, если в ячейке уже записана единица, то на выходе сумматора 1О будет нуль, который запищется в эту же ячейку, а триггер памяти переноса, входящий в сумматор 10, запомнит единицу. Для состояния 0001счетчика 4 ко входу сумматора 1О подключается вторая ячейка выбранной строки. Импульс исследуе5 ого пото ка на входе первого слагаемого уже дол жен кончиться, т.е. в сложении может :принимать участие только результат пере носа, возникший на предыдущем такте. Подобные операции продолжаются до тех пор, пока не переполнится счетчик 4, в результате чего триггер 7 возвратится в исходное состояние и элемент И 2 закроется. В этот момент закончится операция сложения числа, ранее записанного в выбранную строку, с единицей. Вкшочается триггер 7 с тем же импульсом исследуемого потока. Операция сложения числа, хранимого в строке с единицей, должна заканчиваться до появления на счетчике 5 кода нового периода. Поэтому работа счетчика 4 должна производиться с частотой, максимально допущенной для используемого ОЗУ, а кван-. тование периода исследуемого потока - с выхода Делителя 12 частоты. По окончании обработки всей выборки исследуемого потока импульсов начинается этап вывода информации, Счетчики 4 и 5 обеспечивают последовательный вывод содержимого каждой строки в сдвиговый регистр 11. На индикаторе, входящем в состав сдвигового регистра, индицируется количество появлений периодов, длительность которых соответствует выводимой строке в цифровом или аналоговом виде. Таким образом, включение перечисленных элементов позволяет автоматизировать процесс обработки информации, что приводит к сокращению времени определения закона распределения. Так для известного устройства общее время определения закона распределения равно произведению длительности реализаций на количество интервалов гистограммы. Для предлагаемого устройства этот процесс закончится за время одной реализации. Таким образом, с ростом количества интервалов гистограммы, т.е. с повышением разрешающей способности, эффективность предлагаемого устройства увеличивается. Формула изобретения Цифровой статистический анализатор сщгчайных интервалов времени, содержащий первый счетчик, дервый триггер, первый вход которого является входом Пуск анализатора, выход первого триггера соединен с первым входом первого элемента И, второй вход которого является информационным входом анализатора, второй вход первого триггера соединен с выходом второго счетчика, вход которого соединен с выходом первого элемента И, второй триггер, выход которого подкгаочен к первому входу второго элемента И. -Ёыход которого соединен с входом третьего счетчика, отличающийс я тем, что, с целью повышения быстроДейстШ1Я, он содержит делитель частоты, регистр памяти, оперативное запоминающее устройство, сумматор и сдвиговый регистр, вход которого объединен

с первым входом сумматора и подключен к выходу оперативного запоминающего устройства, второй вход сумматора является информационным входом анаггиэатора, выход сумматора подключен к входу записи оперативного запоминающего устройства, первая и вторая группы разрядных входов которого подключены соответственно к разрядным выходам регистра памяти и третьего счетчика, выход переполнения которого соединен с первьш входом второго триггера, второй вход которого соединен с первым входом первого счетчика и входом второго счетчика и соединен с выходом первого элемента

И, выход первого счетчика подключен к входу регистра памяти, второй вход первого счетчика соединен с выходом делителя частоты, вход которого соединен с вторым входом второго элемента И и является входом эталонной частоты анализатора.

Источники информации, принятые во внимание при экспертизе

1.Шляндин В. М. Цифровые измеритепьные преобразователи и приборы, М., Высшая школа, 1973, с. 168.

2.Авторское свидетельство СССР № 413486, кл. С Об Р- 15/36, 1972 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для формирования гистограммы изображения | 1990 |

|

SU1826081A1 |

| РАДИОЛОКАЦИОННАЯ СТАНЦИЯ | 1993 |

|

RU2037842C1 |

| УСТРОЙСТВО ДЛЯ РАЗДЕЛЕНИЯ НАПРАВЛЕНИЙ ПЕРЕДАЧИ И ПРИЕМА В ДУПЛЕКСНЫХ СИСТЕМАХ СВЯЗИ | 1993 |

|

RU2039415C1 |

| Параллельный статистический анализатор отклонений и колебаний напряжения | 1982 |

|

SU1076913A1 |

| Устройство для контроля параметров двигателя внутреннего сгорания | 1988 |

|

SU1733946A1 |

| Устройство распознавания изображений | 1989 |

|

SU1674153A1 |

| Устройство для формирования адресов операндов процессора быстрого преобразования Фурье | 1982 |

|

SU1056207A1 |

| Анализатор спектра | 1984 |

|

SU1237987A1 |

| УСТРОЙСТВО СЧИТЫВАНИЯ СИГНАЛЬНОГО ЗАРЯДА С МАТРИЧНОГО ПЗИ-ФОТОПРИЕМНИКА | 2007 |

|

RU2341850C1 |

| Устройство для контроля полупроводниковой оперативной памяти | 1982 |

|

SU1051586A1 |

Авторы

Даты

1982-07-15—Публикация

1980-03-18—Подача