(54) ПРОГРАММНОЕ ЗАДАЮЩЕЕ УСТРОЙСТВО

| название | год | авторы | номер документа |

|---|---|---|---|

| Программное задающее устройство | 1979 |

|

SU903808A2 |

| Цифровое задающее устройство | 1981 |

|

SU983123A1 |

| Программное задающее устройство | 1976 |

|

SU693337A1 |

| Устройство для вычисления массы нефти и нефтепродуктов в резервуарах | 1983 |

|

SU1117653A1 |

| Устройство для регулирования расхода | 1986 |

|

SU1377832A1 |

| Устройство для контроля преобразователей угла поворота вала в код | 1983 |

|

SU1231608A1 |

| Устройство для обучения оператора | 1987 |

|

SU1550568A1 |

| Устройство для программного счета изделий | 1983 |

|

SU1113824A1 |

| Устройство для программного управления | 1985 |

|

SU1280571A1 |

| Программно-временное устройство | 1982 |

|

SU1062645A1 |

1

Изобретение относится к области автоматики и может быть использовано в системах автоматического регулирования с программным заданием регулируемого параметра.

Известно устройство для задания программы 1 , содержащее блоки набора программы, формирователь импульсов, управляемый делитель частоты, блоки задания скорости, уровня сигнала и времени участка, переключающего схему и реверсивный счетчик.

Недостатком данного устройства является большой объем предварительных вычислительных операций, что усложняет устройство, снижает точность его работы и надежность.

Наиболее близким к изобретению техническим решением является программное задающее устройство 2, содержащее блок задания уровня, выход которого соединен с одним входом первого блока сравнения и через запоминающий блок и непосредственно со входами вычитателя, подключенного выходом через включенные последовательно преобразователь код-частота другой вход которого соединен с выходом генератора тактовых импульсов, и управляемый делитель к первому входу реверсивного счетчика, второй вход которого подключен к выходу блока коррекции, соединенного первым входом через включенные последовательно ком10мутатор участков и счетчик времени с вьпсодом блока задания времени, подключенного входом ко входу блока задания уровня и выходу коммутатора участков. Втсфой вход блока коррекции соединен

IS с другим входом счетчика времени и выходом генератора тактовых импульсов. Выход реверсивного счетчика подключен к другому входу первого блока сравнения, одному входу второго блока

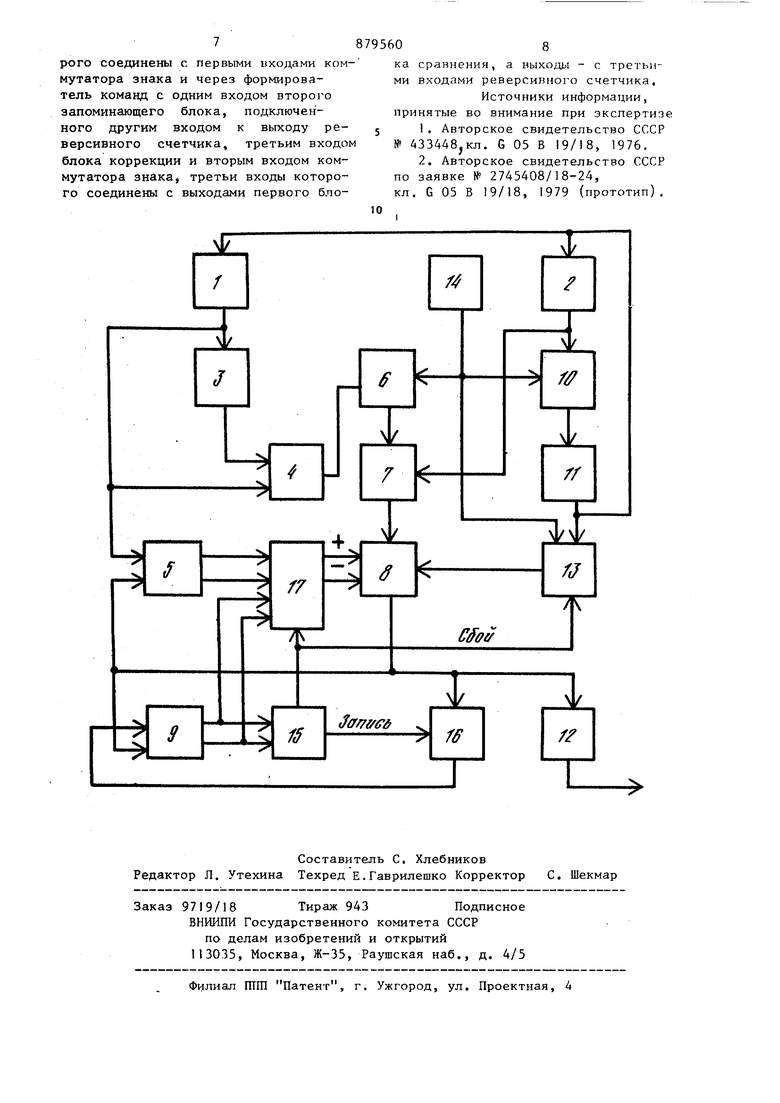

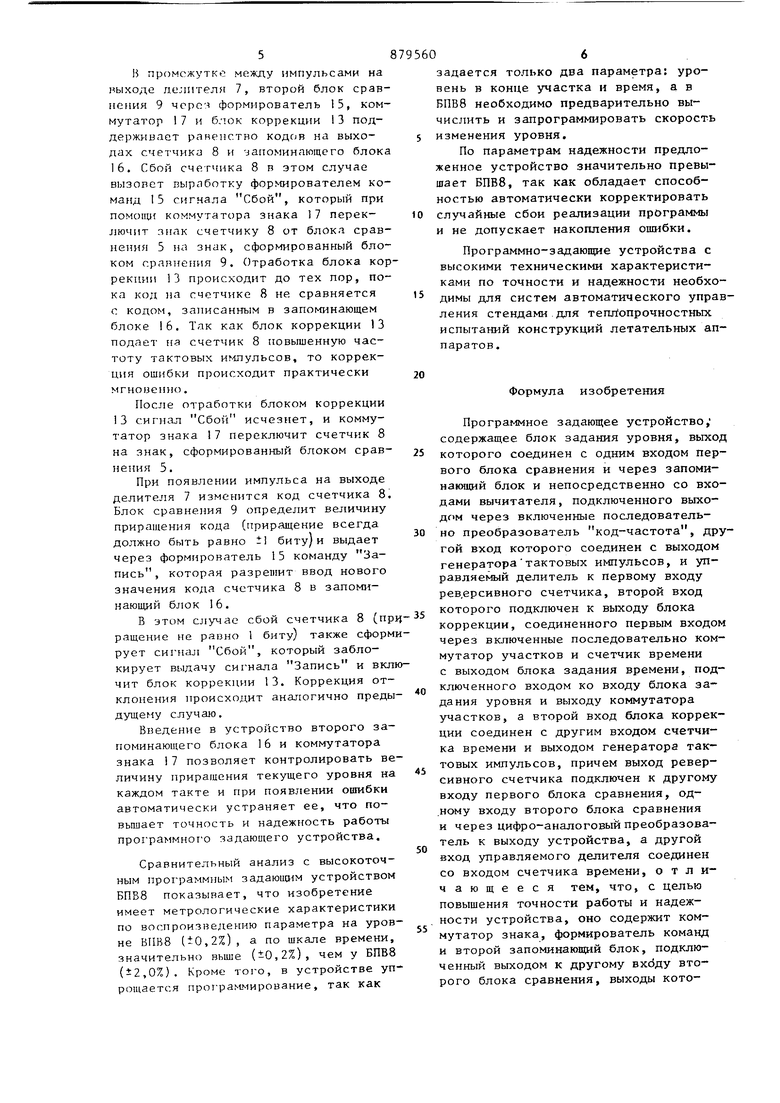

20 сравнения и через цифро-аналоговый преобразователь к выходу устройства, а другой вход управляемого делителя соединен со входом счетчика времени. 38 Однако данное ycTpc iii-TRo ограниченные функщ10Н1Ъ1е но-змпжгюсти по коррекции ошибок при реали ацнн npoi- раммы; блоки сравнения данного устройства контролирует 1зых(д гчначония текущего уровня (Н) за пределы тоны ограниченной начаг1 ч1ым (4.) и кснечным (Нка) уровнями участка iipor;)aMMi.i, а блок коррекции ос;у1иеств;1Яет подтяжку текущего уровня (Нг) до заданного значения Нкг , ecjnr уровень этого значения не достиг ц момент переключения на следующий участок. .)то снижает точ ность работы и надежность ус:тройстна Целью изобретения является поньпиение точности работы и надежности уст ройства. Эта цель достиг-астся тем, что программное задающее устройство, содержащее блок, задания У1нэвня, выход которого соединен с одним входом нер вого блока сравнения и через запомин ющий блок и неносредств(и1нс со входами вычитателя, подключенного выходом через включенные последовательно преобразователь код-частота, другой вход которого соединен с выходом генератора тактовых импульсов, и управляемый делитель к нервому вхо ду реверсивного счетчика, второй вхо которого подключен к выходу блока коррекции, соединенного первым входом через включенн)1е носледовательно коммутатор участков и счетчик вре мени с выходом блока задания времени подключенного входом ко входу блока задания уровня и выходу коммутатора участков, а второр вход блока коррекции соединен с другим входом счет чика времени и выходом генератора та товых импульсов, причем выход реверсивного счетчика подключен к другому входу первого блока сравнения, одному входу второго блока сравнения и ч рез цифро-аналоговый преобразователь к выходу устройства, а другой вход управляемого делителя соединен со входом счетчика времени, введены ком мутатор знака, формирователь команд и второй запоминаю1Щ1й блок, подключенный выходом к другому входу второго блока сравнения, выходы которог соединены с первыми входами коммутатора знака и черея формирователь команд с одним входом второго запоминающего блока, нодключенного другим входом к выходу реверсивно1-о счетчика, третьим входом блока коррекПНИ и вторым вхолом коммутатора знака, третьи входы когорого соединены с; выходами первого блока сравнения, а )ьгход111 с тргпьими входами реверсивного счетчика. На чертеже представлена структурная схема устройства. Програм -1пое задающее устройство содержит блок задаьшя уровня I, блок задания 2, запоминающий блок 3, вычитатель 4, первый блок сравнения 3, преобразователь код-частота 6, yпpaвляe п,ш делитель 7, реверсивны счетчик 8, второй бдок сравнения 9, счетчик времени 10, коммутатор участков 11, ЦАП 12, блок коррекдии 13, генератор тактовых импульсов 14, фор шровате.чь команд 15, второи заггомпнающий блок 16 и коммутаТчОр знака 1 7, Устройство 1)абитает следующим образом. По команде Пуск тактовые импудьсы для работы устройства форм -1рует генератор 14. Частота импульсов с преобразовате.чя 6 поступает на управляемый д.еjniTejib 7, коэфф1П|;иент деления которого задает код времени участка, хранящийся в блоке задания времени 2. Частота импулг.сов о..) с, де.читсля 7 П1К)порционал1 на разности уровней Нц--Пк, и обратно пропорииона.льна времени отработки t участка ,.,. и поступает на счетчик 8, выходной сигнал которого представляет собой код текущего значения уровня Н. Код текущего уровня через ILUl 12 формирует выходной аналоговый ситнал устройства. При истечении заданного времени участка счетчик 10 подает команду на комгтутатор участков 1 1 о переключении на отработку с;гедующого участка. В момент 1 ереключения участка включается блок коррекции 13, который подтянет текущий уровень до значения lii,. если он этого значения не достпг. Первый блок сравнения 3 )ырабатывает сигн.-1-1Ы знака (, -) д;гя счетчика 8, сравнивая Н, с к-. Прп дс.чстижении текуишм уровне.м значонпя HT на выходах б.чока сравпсмшн 3 и коммутатора знака 1 7 исчочпу lut налы знака ( , -), что пришмег к останову счетчика 8 и с-1-аб1 лизации догтнгнутого )1я уровня Ик; .

В промежутке между импульсами на выходе делителя 7, второй блок сравнения 9 черс. формирователь 15, коммутатор 17 и блок коррекции 13 поддерживает раненстно кодов на выходах счетчика 8 и запоминающего блока 16. Сбой счетчика 8 в этом случае вызовет выработку фop fиpoвaтeлeм команд 15 сигнала Сбой, который при помощи коммутатора знака 17 переключит знак счетчику 8 от блока сравнения 5 на знак, сформированный блоком сравнения 9. Отработка блока коррекции 13 происходит до тех пор, пока код на счетчике 8 не сравняется с кодом, записанным в запоминающем блоке 16. Так как блок коррекции 13 подает на счетчик 8 повышенную частоту тактовых титулъсов, то коррекция ошибки происходит практически мгновенно.

После отработки блоком коррекции 13 сигнал Сбой исчезнет, и коммутатор знака 17 переключит счетчик 8 на знак, сформированный блоком сравнения 5.

При появлении импульса на выходе делителя 7 изменится код счетчика 8. Блок сравнения 9 определит величину приращения кода (приращение всегда должно быть равно il биту)и выдает через формирователь 15 команду Запись , которая разрешит ввод нового значения кода счетчика 8 в запоминающий блок I6.

В этом случае сбой счетчика 8 (прращение ьге равно 1 биту) также сформрует сигнал Сбой, который заблокирует выдачу сигнала Запись и вклчит блок коррекции 13. Коррекция отклонения происходит аналогично преды дущену случаю.

Введение в устройство второго запоминающего блока 16 и коммутатора знака 17 позволяет контролировать величину приращения текущего уровня на каждом такте и при появлении ошибки автоматически устраняет ее, что повьщ ает точность и надежность работы программного задающего устройства.

Сравнительный анализ с высокоточным программным задающим устройством БПВ8 показывает, что изобретение имеет метрологические характеристики по воспроизведению параметра на урон не B1IB8 (±0,2%), а по шкале времени, значительнее вьш1е (0,2%), чем у БПВ8 (i2,0%). Кроме того, в устройстве упрощается прот-рам-мирование, так как

задается только два параметра: уровень в конце участка и время, а в БПВ8 необходимо предварительно вычислить и запрограммировать скорость изменения уровня.

По параметрам надежности предложенное устройство значительно превышает БПВ8, так как обладает способностью автоматически корректировать случайные сбои реализации программы и не допускает накопления ошибки.

Программно-задающие устройства с высокими техническими характеристиками по точности и надежности необходимы для систем автоматического управления стендами для тешт;опрочностных испытаний конструкций летательных аппаратов.

Формула изобретения

Программное задающее устройство, содержащее блок задания уровня, выхо которого соединен с одним входом первого блока сравнения и через запоминающий блок и непосредственно со входами вычитателя, подключенного выходом через включенные последовательно преобразователь код-частота, другой вход которого соединен с выходом генераторатактовых импульсов, и управляемый делитель к первому входу рев.ерсивного счетчика, второй вход которого подключен к выходу блока коррекции, соединенного первым входом через включенные последовательно коммутатор участков и счетчик времени с выходом блока задания времени, подключенного входом ко входу блока задания уровня и выходу коммутатора участков, а второй вход блока коррекции соединен с другим входом счетчика времени и выходом генератора так товых импульсов, причем выход реверсивного счетчика подключен к другому входу первого блока сравнения, од.ному входу второго блока сравнения и через цифро-аналоговый преобразователь к выходу устройства, а другой вход управляемого делителя соединен со входом счетчика времени, отличающееся тем, что, с целью повышения точности работы и надежности устройства, оно содержит коммутатор знака, формирователь команд и второй запоминающий блок, подключенный выходом к другому вхбду второго блока сравнения, выходы которого соединены с первыми «ходами ком мутатора знака и через формирователь команд с одним входом второго запоминающего блока, подключенного другим входом к выходу реверсивного счетчика, третьим входо блока коррекции и вторым входом коммутатора знака, третьи входы которого соединены с выходами первого блоNT

- ff

f7

i

Jfff7ffC6

15

Т

f4

/

fff

L

//

ФФ

fj

/

/

//

fff 08 срав)1ения, а ныходы - с третьивходами реверсияного счетчика. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР № 433448,кл. G 05 В 19/18, 1976. 2,Авторское свидетельство СССР по заявке № 2745408/18-24, кл. G 05 В 19/18, 1979 (прототип).

Авторы

Даты

1981-11-07—Публикация

1980-01-18—Подача