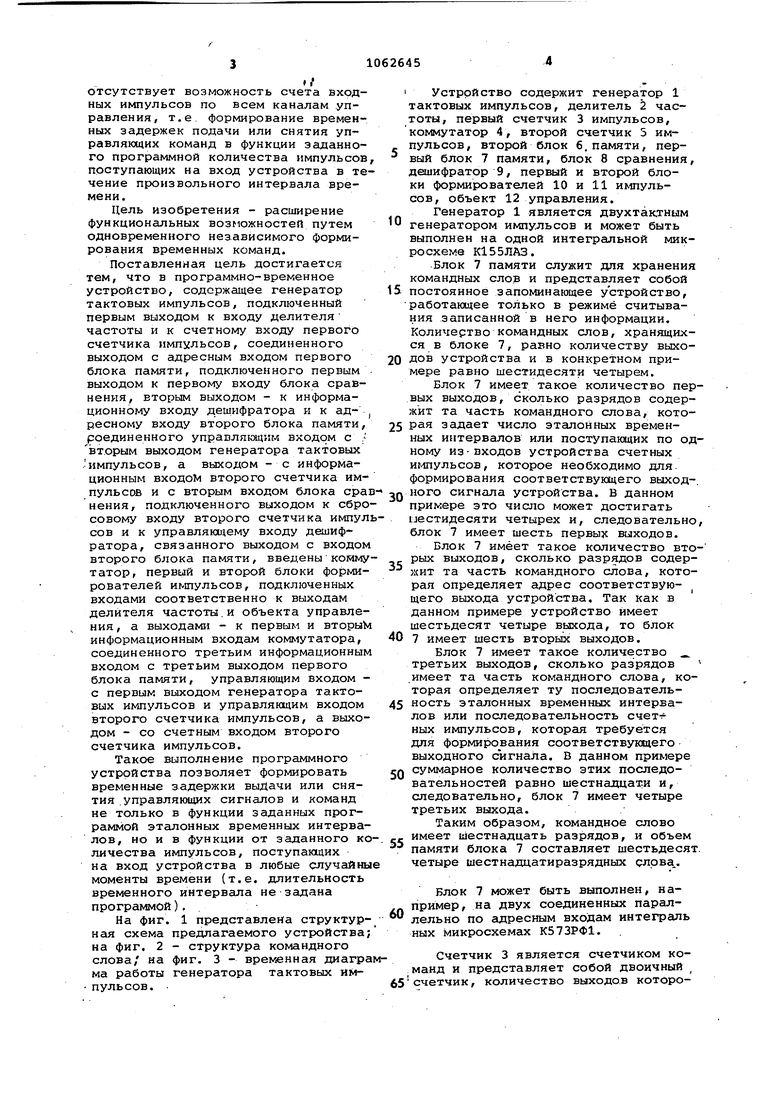

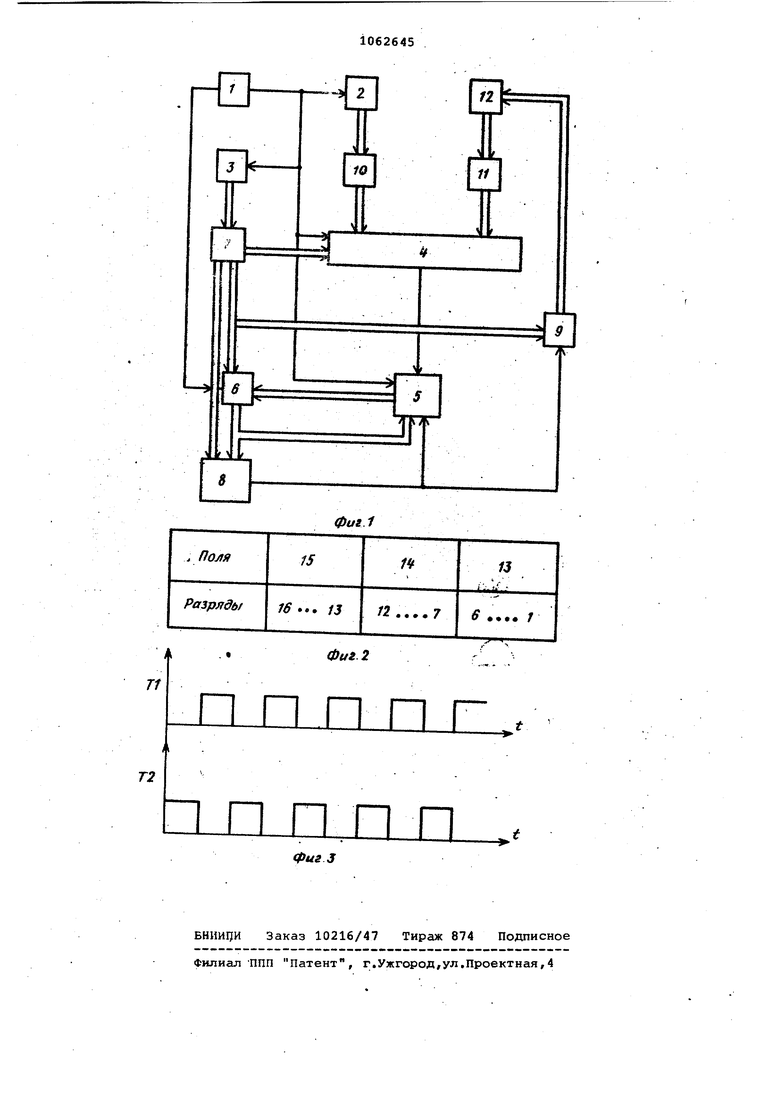

Изобретение относится к автомат ке и вычислительной технике и может быть использовано для управления станками, автоматическими лини ми и другими объектами, где по тех нологическому циклу требуется осуществлять различные задержки упраб ляювдих сигналов в зависимости от заданного времени или от заданного числа срабатываний входных механиз мов и устройств. Известно устройство, содержащее генератор импульсов, группу элейен тов И, делитель частоты, счетчик времени, дешифратор, запоминаюишй блок,.счетчик номера команды, первый элемент ИЛИ выходом соединенный со счетным входом, счетчика времени, выход которого подключен к счетному входу счетчика номера команда, выходами подсоединенного к входам запоминающего блока. Выходы запоминающего блока соединены с входами счетчика времени и дешифратора, выходщ которого среди нены с первыми .входами групгщ эЛементов И. В устройство также введены реверсивный счетчик, токовые ключи, блок коррекции реверсивного счетчика, блок управления ревер сивным счетчиком, элементы И выбора счетных входов реверсивного счетчика, элемент НЕ, первый и втор элементы И и второй элемент ИЛИ, первый вход которого соединен с выходом первого элемента И. Первый вход элемента И подсоединен к.одному из выходов запоминакадего блока, а второй вход - к выходу первого элемента ПЛИ, первый вход котдрого подсоединен к выходу делителя частоты, а второй - к выходу второг элемента И, nejjBHM входом.соединенного с одним из выходов дешифратора, а вторым - к первым входам груп пы элементов И и к выходу генератора импульсов. Выход второго элемента ИЛИ. соединен с: первыми выходами элементбв И выбора счетных входов реверсивного счетчика, выходы которых подсоединены к соответствующим счетным входам, вторые входы з лемен тон И соединены соответственно с пе вым выходом блока управления реверсивным счетчиком, входами соединенного с выходами счетчика номера .команды, а вторым выходом - с входом блока коррекции реверсивного счетчика, выходы которого через реверсивный счетчик подсоединены) к входам токовых ключей l . Однако устройство имеет только одий канал формирования заданного временного интервала для всего диапазона возможньзх значений временных задержек. Формирование заданных временных интервалов происходит пос ледовательно один за другим в зависимости от номера команды, причем . формирование величины заданного вре-. менного интервала происходит с помощью одних и тех же элементов Устройства. Недостатком устройства являются ограниченные функциональные возможности, состоящие в том, что формирование временных интервалов осуществляется только последовательно и исключена возможность одновременного независимого формирования временных команд. Кроме того, в устройстве исключена возможность счета числа срабатываний входньж устройств и механизмов. Наиболее близким-к изобретению является устройство, содержащее счетчик времени, перрый блок памяти, соединенный адресными входами .с выходами счетчика команд, первыми информационными выходами - с входами дешифратора, подключенного выходами к первым входам блока элементов И, делитель частоты, связанный счетным входом с первымвыходом генератора импульсов, а схему сравнения и второй блок памяти, соединенный адресными входами с пepвы ли выходами первого блока памяти, информационными входами - с выходами счетчика времени, управляю-дам входом с вторым выходом генератора импульсов, а выходами - с установочными входами счетчика времени и с первыми входами схемы сравнения, подключенной вторыми входами к вторым выходам первого блока памяти, выходом - к вторым входам блока элементов Ник входу сброса счетчика времени, соединенного счетным входом с выходом делителя.частоты, подключенного установочными входами к третьим выходам первого блока памяти. Устройство имеет число каналов управления по числу выходов. Формирование заданных выдержек времени по различным каналам управления происходит независимо друг от друга и одновременно по всем каналам. Текущее значение отсчитываемого времени по всем каналам управления хранится во втором блоке памяти, а номера каналов управления и величины выдержек времени, которые заданы, Х1 анятся в первом блоке памяти. Таким образом, формирование заданных выдержек времени для всех каналов управления происходит с помощью одних и тех же элементов и одновременно по всем каналам управения . Недостатком устройства являются ограниченные функциональные возможности, состоящие в , что наряду с формированием выдержек времени отсутствует возможность счета входных импульсов по всем каналам управления, т.е. формирование временных задержек подачи или снятия управляющих команд в функции заданного программной количества импульсов поступающих на вход устройства в те чение произвольного интервала времени. Цель изобретения - расширение функциональных возможностей путем одновременного независимого формирования временных команд. Поставленная цель достигается тем, что в программно-временное устройство, содержащее генератор тактовых импульсов, подключенный первым выходом к входу делителя частоты и к счетному входу первого счетчика импульсов, соединенного выходом с адресным входом первого блока памяти, подключенного первым выходом к первому входу блока сравнения, вторым выходом - к информационному входу дешифратора и к адресному входу второго блока памяти, соединенного управля(яцям входом с вторым выходом генератора тактовых .импульсов, а вьлходом - с информационным входом второго счетчика им пульсов и с вторым входом блока сра нения, подключенного выходом к сбро совому входу второго счетчика импул сов и к управлякадему входу дешифратора, связанного выходом с входо второго блока памяти, введены комм татор, первый и второй блоки форми рователей иктульсов, подключенных входами соответственно к выходам делителя частоты.и объекта управле ния , а выходами - к первым и вторы информационным входам коммутатора, соединенного третьим информационны входом с третьим выходом первого блока памяти, управляющим входом с первым выходом генератора тактовых импульсов и управляктим входом второго счетчика импульсов, а выхо дом - со счетным входом второго счетчика импульсов. Такое выполнение программного устройства позволяет формировать временные задержки выдачи или снятия .управляющих сигналов и команд не только в функции заданных программой эталонных временных интерва лов, но и в функции от заданного к личества импульсов, поступающих на вход устройства в любые случайн моменты времени (т.е. длительность временного интервала не задана програквиой) , . На фиг. 1 представлена структур ная схема предлагаемого устройства на фиг. 2 - структура командного слова/ на фиг. 3 - временная диагр ма работы генератора тактовых им пульсов. . Устройство содержит генератор 1 тактовых импульсов, делитель 2 частоты, первый счетчик 3 импульсов, коммутатор 4, второй счетчик 5 импульсов, второй блок 6, памяти, первый блок 7 памяти, блок 8 сравнения, дешифратор 9, перилй и второй блоки формирователей 10 и 11 импульсов, объект 12 управления. Генератор 1 является двухтактным генератором импульсов и может быть выполнен на одной интегральной микросхеме К155ЛАЗ. Блок 7 памяти служит для хранения командных слов и представляет собой постоянное запоминающее устройство, работающее только в режиме считывания записанной в него информации. Количество командных слов, хранящихся в блоке 7, равно количеству выходов устройства ив конкретном примере равно шестидесяти четырем. Блок 7 имеет такое количество первых выходов, сколько разрядов содержит та часть командного слова, которая задает число эталонных временных интервалов или поступаквдих по одному из-входов устройства счетных импульсов, которое необходимо для. формирования соответствующего выход-. иого сигнала устройства. В данном примере это число может достигать иестидесяти четырех и, следовательно, блок 7 имеет шесть первых выходов. Блок 7 имеет такое количество вторых выходов, сколько разрядов содержит та часть командного слова, которая определяет адрес соответствующего вькода устройства. Так как в данном примере устройство имеет шестьдесят четыре выхода, то блок 7 имеет шесть вторых выходов. Блок 7 имеет такое количество третьих выходов, сколько разрядов имеет та часть командного слова, которая определяет ту последовательность эталонных временных интервалов или последовательность счет-г ных импульсов, которая требуется для формирования соответствующего выходного сигнала. В данном примере суммарное количество этих последовательностей равно шестнадцати и, следовательно, блок 7 имеет четыре третьих выхода. Таким образом, командное слово имеет шестнадцать разрядов, и объем памяти блока 7 составляет шестьдесят, четыре шестнадцатиразрядных слрва. Блок 7 может быть выполнен, например, на двух соединенных параллельно по адресным входам интеграль ных микросхемах К573РФ1. Счетчик 3 является счетчиком команд и представляет собой двоичный , счетчик, количество выходов которого зависит от числа командных слов, iхранящихся в блоке 7, и в данном примере равно шести.

Такой.счетчик может быть выполне на двух последовательно соединенных интегральных микросхемах К155ИЕ5.

Блок 6 представляет собой оперативное запоминающее устройство, имещее режимы считывания и записи информации. .

Объем памяти блока б в данном примере составляет шестьдесят четыре шестиразрядных слова.

Блок, б может быть выполнен на шести параллельно соединенных пр адресным входам микросхемах К565РУ2

Блок 8 сравнения предназначен для поразрядного сравнения двух двоичных кодов. Разрядность этих кодов равна,числу первых выходов блока 7, в данном случае шести. Такая схема может быть реализована на двух интегральных микросхемах K134CII1.

Делитель 2 частоты представляет собой двоичный счетчик, предназнач:енный для формирования последовательностей эталонных временных интервалов путем деления частоты сигНсша, поступающего на его вход с первого выхода генератора 1.

Число выходов делителя 2 частоты определяется количеством последовательностей эталонных импульсов, необходимых для формирования устройством выходных сигналов. Разрядность счетчика определяется ве 1ичинами эталонных временных интервалов в каждой из последовательности и частотой сигнала, поступающего на делитель 2 частрты от генецатора 1.

В данном примере число выходов равно восьми. Делитель 2 частоты может быть выполнен на последовательно соединенных интегральных микросхемах К155НЕ5.

Счетчик 5 может быть реализован на двух последовательно соединенных интегральных микросхемах К155ИЕ7.

Коммутатор 4 предназначен для коммутации одной из группы последовательностей эталонных временных интервалов, поступающих с выходов делителя 2 частоты, либо одной из группы последовательностей входных импульсных сигналов, поступанвдих с выходов управляег гого объекта через произвольные интервалы времени.

Число первых информационных входов комкчутатора 4 равно числу выходов делителя 2 частоты, в данном примере восьм. Число вторых информационных входов коммутатора 4 равно числу входов устройства и, в данном примере восьми. I Коммутатор 4 может быть выполнен на одной микросхеме К155КП1.

Формирователи 10 и 11 являются формирователями импульсов, дпительность которых равна длительности цикла работы устройства.

Формирователи 10 формируют импульсы, поступающие с выходов делителя 2 частоты на первые входы коммутатора 4. Число формирователей

10равно числу выходов делителя частоты 2.

Формирователи 11 формируют импульсы, поступающие с входов устройства на вторые входы коммутатора 4, Число формирователей 11 равно числу входов устройства.

В данном примере число форгдарователей ID равно числу формирователей

11и.равно восьми. Формирователи 10 так же, как и

формирователи 11, могут быть выполнены, в данном примере, на восьми интегральных микросхемах К155АГ1 каждый.

Дешифратор 9 может быть реализован на пяти интегральных микросхемах К155НДЗ.

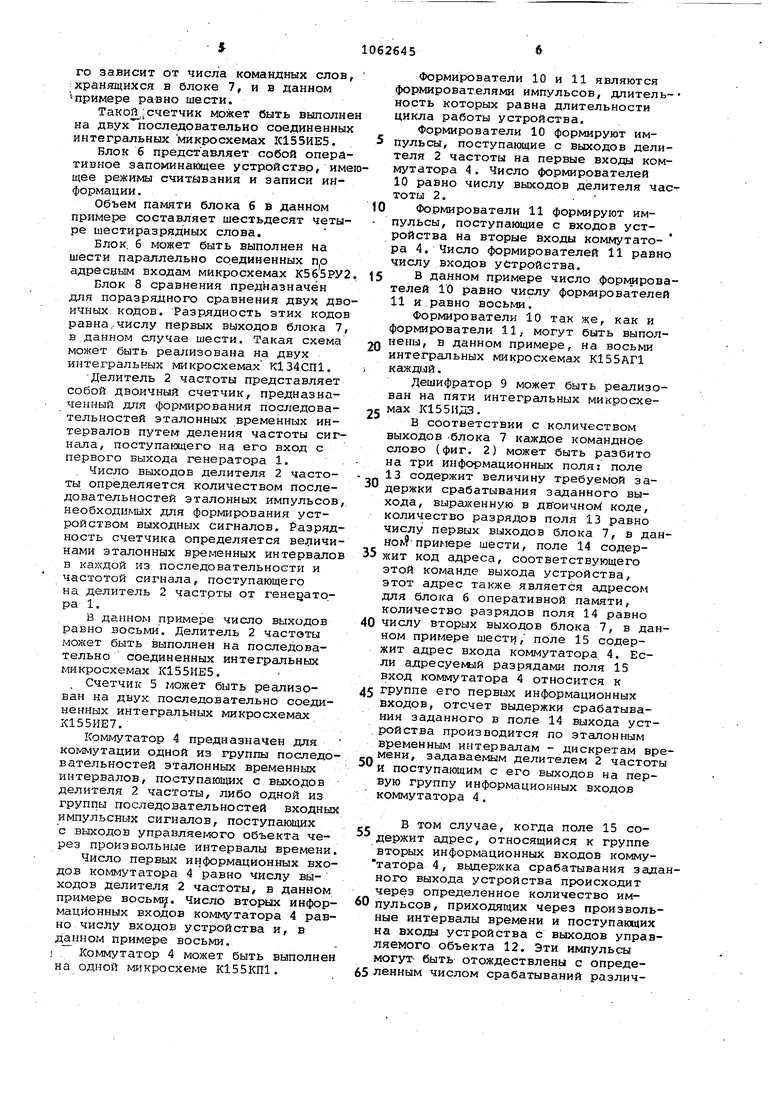

В соответствии с количеством выходов -блока 7 командное слово (фиг. 2) может быть разбито на три информационных поля: поле 13 содержит величину требуемой задержки срабатывания заданного выхода, выраженную в двоичноМ коде, количество разрядов поля 13 равно числу первых выходов блока 7, в даннол -примере шести, поле 14 содерХ(ит код адреса, соответствующего этой команде выхода устройства, этот адрес также является адресом для блока б оперативной памяти, количество разрядов поля 14 равно числу вторых выходов блока 7, в данном примере шести, поле 15 содержит адрес входа KOMiviyTaTopa. 4. Если адресуеьий разрядами поля 15 вход коммутатора 4 относится к группе его первых информационных входов, отсчет выдержки срабатывания заданного в поле 14 выхода устройства производится по эталонным временным интервалам - дискретам врмени, задаваемым делителем 2 частот И поступающим с его выходов на первую группу информационных входов коммутатора 4.

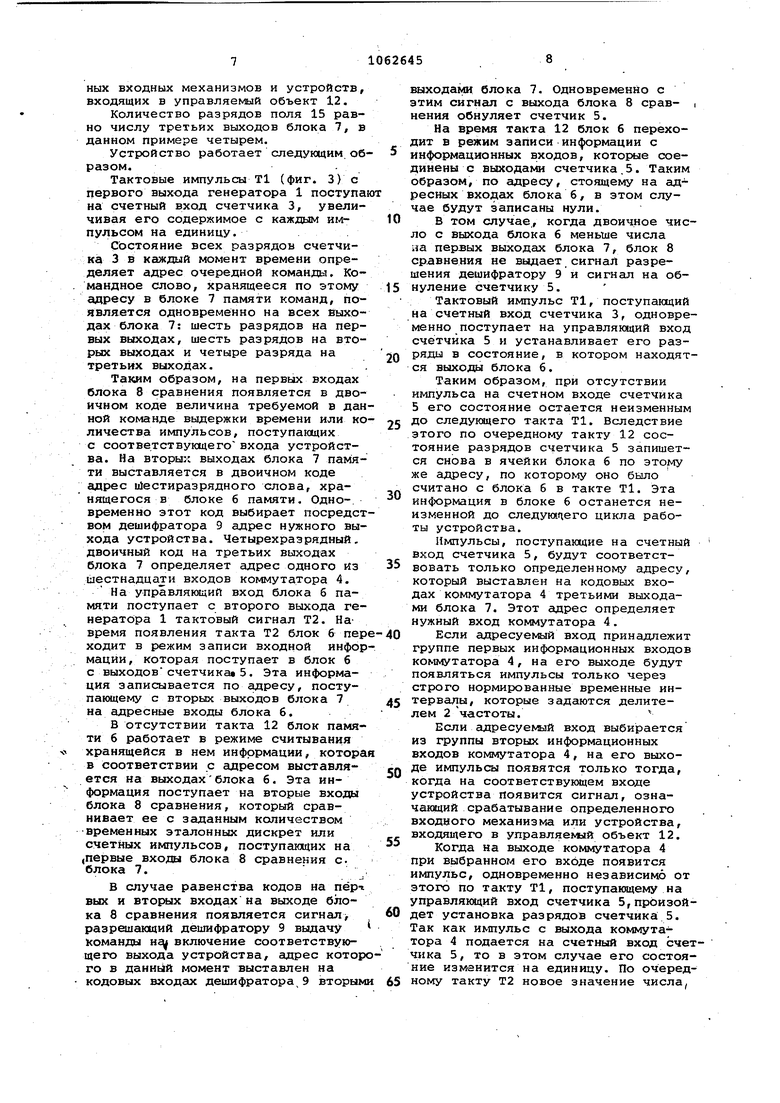

В том случае, когда поле 15 содержит адрес, относящийся к группе вторых информационных входов коммутатора 4, выдержка срабатывания заданого выхода устройства происходит через определенное количество пульсов, приходящих через произвольные интервалы времени и поступающих на входы устройства с выходов управляемого объекта 12. Эти импульсы могут- быть отождествлены с опреде65 ленным числом срабатываний различных входных механизмов и устройств, входящих в управлявь-ый объект 12. Количество разрядов поля 15 равно числу третьих выходов блока 7, в данном примере четырем. Устройство работает следующим об разом.Тактовые импульсы Т1 (фиг. 3) с первого выхода генератора 1 поступа на счетный вход счетчика 3, увеличивая его содержимое с каждым импульсом на единицу. Состояние всех разрядов счетчика 3 в каждый момент времени определяет адрес очередной команды. Командное слово, хранящееся по этому адресу в блоке 7 памяти команд, появляется одновременно на всех выходах блока 7: шесть разрядов на первых выходах, шесть разрядов на вто рых выходах и четыре разряда на третьих выходах. Таким образом, на первых входах блока 8 сравнения появляется в дво ичном коде величина требуемой в да ной команде выдержки времени или к личества импульсов, поступающих с соответствующего входа устройства. На вторы:: выходах блока 7 памя ти выставляется в двоичном коде адрес йестиразрядного слова, хранящегося в блоке 6 памяти. Одно-, временно этот код выбирает посредс вом дешифратора 9 адрес нужного вы хода устройства. Четырехразрядный, двоичный код на третьих выходах блока 7 определяет адрес одного из шестнадцати входов коммутатора 4. На управляющий вход блока б памяти поступает с второго выхода ге нератора 1 тактовый сигнал Т2. Навремя появления такта Т2 блок 6 пе ходит в режим записи входной инфо мации, которая поступает в блок 6 с выходовсчетчика 5. Эта информация записывается по адресу, поступающему с вторых выходов блока 7 на адресные входы блока 6. В отсутствии такта 12 блок памя ти 6 работает в режиме считывания хранящейся в нем информации, котор в соответствии с адресом выставляется на выходахблока 6. Эта информация поступает на вторые входы блока 8 сравнения, который сравнивает ее с заданным количеством временных эталонных дискрет или счетных импульсов, поступающих на ,первые входы блока 8 сравнения с. блока 7. В случае равенства кодов на nep вых и вторых входах на выходе блока 8 сравнения появляется сигналу разранающий дешифратору 9 выдачу Команды игу включение соответствующего выхода устройства/ адрес кото го в данный момент выставлен на кодовых входах дешифратора,9 вторы выходами блока 7. Одновременно с этим сигнал с выхода блока 8 срав- i нения обнуляет счетчик 5. На время такта 12 блок 6 переходит в режим записи информации с информационных входов, которые соединены с выходами счетчика.5. Таким образом, по адресу, стояоцему на адресных входах блока 6, в этом случае будут записаны нули. В том случае, когда двоичное число с выхода блока 6 меньше числа иа первых выходах блока 7, блок 8 сравнения не выдает сигнал разрешения дешифратору 9 и сигнал на обнуление счетчику 5. Тактовый импульс Т1, поступающий на счетный вход счетчика 3, одновременно поступает на управляющий вход счётчика 5 и устанавливает его разряды в состояние, в котором находятся выходы блока б. Таким образом, при отсутствии импульса на счетном входе счетчика 5 его состояние остается неизменным до следуюцего такта Т1. Вследствие этого по очередному такту 12 состояние разрядов счетчика 5 запишется снова в ячейки блока 6 по этому же адресу, по которому оно было считано с блока б в такте Т1. Эта информация в блоке 6 останется неизменной до следующего цикла работы устройства. Импульсы, поступающие на счетный вход счетчика 5, будут соответствовать только определенному адресу, который выставлен на кодовых входах коммутатора 4 третьими выходами блока 7. Этот адрес определяет нужный вход коммутатора 4. Если адресуег-ый вход принадлежит группе первых информационных входов коммутатора 4, на его выходе будут появляться импульсы только через строго нормированные временные интервалы, которые задаются делителем 2 частоты. Если адресуемый вход выбирается из группы вторых информационных входов коммутатора 4, на его выходе импульсы появятся только тогда, когда на соответствующем входе устройства появится сигнал, означаквдий срабатывание определенного входного механизма или устройства, входящего в управляемой объект 12. Когда на выходе коммутатора 4 при выбранном его входе появится импульс, одновременно независимо от этого по такту Т1, поступающему на управляющий вход счетчика 5,произойдет установка разрядов счетчика 5. Так как импульс с выхода коммутатора 4 подается на счетный вход счетчика 5, то в этом случае его состояние изменится на единицу. По очередному такту Т2 новое значение числа,

увеличенное на единицу, находящеес в счетчике 5, запишется по тому же адресу в блок 6.

Независимо от результата сравнения в блоке 8 сравнения счетчик 3 переходит к следукмдей команде в момент начала очередного такта Т1 и перебирает таким образом все каналы управления объекта 12. После исполнения последней команды счетчик 3 в результате переполнения обнуляется и выдает на адресные входы блока 7 вновь адрес первой по программе команды, имеющей нулевой адрес.

Таким образом, весь цикл работы устройства повторяется.

В блоке 6 (оперативной памяти) происходит, таким образом, накопление по определенным адресам количества поступивших строг.о, нормированных временных дискретлибо количества импульсов или срабатывани постула ощих через произвольные интервалы времени с входов устройства. Это накопление для каждой команды происходит по адресу, указанному в командном слове, и который является одновременно адресом для блока 6 оперативной памяти и адресом выхода устройства.

Как только величина этой накопленной информации сравняется с заданным числом, поступающим с блоЛа 7, с первых его выходов, блок 8 сравнения выдаст сигнал на включение соответствующего канала управления объектом 12 и одновременно с этим обнулит счетчик 5. Это нулевое значение запишется в блок 6 по тому же адресу. Таким образом, этот канал управления вновь готов для отсчета временной задержки либо количества срабатываний, заданного в команде входного устройства.

Таким образом, предложенное программное устройство может управлять i сложным объектом техники, в частности, металлорежущим станком, выдавая команды управления по несколь5 КИМ каналам управления одновременно, формируя при этом эти команды не только с заданной в програг ле выдержкой времени, но и по истечении заданного в программе числа

0 срабатывания входных механизмов и устройств, поступающих через произвольные промежутки времени. Предлагаемое устройство может быть использовано на любых станках,

5 автоматических линиях и Других установках, где по технологическому циклу требуется формировать команды управления с заданной вьщержкой времени или через заданное количество срабатываний различных ханизмов, кнопок, конечных выключателей и других входных устройств.

введение в устройство двух групп C .формирователей и коммутатора позволяет существенно расширить функции программного устройства и область его применения, так как при этом команды управления с выхода устройства формируются не только че0 рез заданные выдержки времени,

но и через заданное число срабатываний определенных механизмов И устройств, входящих в объект уггравления. 5

Это позволяет с помощью предлагаемого программного устройства строить системы многоразового, многбциклового управления, учиты0 вающие количество пройденных объектом управления шагов, количество выполненных операций или другие импульсные сигналы от управляемых -объектов.

фиг.1

| название | год | авторы | номер документа |

|---|---|---|---|

| Программно-временное устройство | 1981 |

|

SU1003025A1 |

| Устройство для последовательного программного управления | 1983 |

|

SU1126928A1 |

| Устройство для контроля функционирования логических блоков | 1987 |

|

SU1432528A2 |

| Программируемый контроллер | 1983 |

|

SU1238032A1 |

| УСТРОЙСТВО ДЛЯ ЦИФРОВОЙ МАГНИТНОЙ ЗАПИСИ ИНФОРМАЦИИ НА ВИДЕОМАГНИТОФОНЕ | 1993 |

|

RU2042218C1 |

| Система автоматического контроля параметров электронных схем | 1989 |

|

SU1700538A1 |

| Устройство для вычисления булевых функций | 1980 |

|

SU955027A1 |

| Устройство для сопряжения ЦВМ с накопителями на магнитной ленте | 1985 |

|

SU1288708A1 |

| Вычислительное устройство для реализации логических функций | 1983 |

|

SU1269130A1 |

| Устройство для вычисления массы нефти и нефтепродуктов в резервуарах | 1983 |

|

SU1117653A1 |

ПРОГРАММНО-ВРЕМЕННОЕ УСТРОЙСТЮ, содержащее генератор тактовых импульсов, подключенный первым выходом к входу делителя частоты и к счетному входу первого счетчика импульсов, соединенного выходом с адресным входом первого блока памяти, подключенного первым выходом к первому входу блока сравнения, вторым выходом - к информации онному входу дешифратора и к адрест ному входу второго блока памяти, соединенного управляющим входом с вторим выходом генератора тактовых импульсов, а выходом - с информационным входом второго счетчика импульсов и с вторым входом блока сравнения, подключенного выходом к сбросовому входу второго счетчика импульсов и к управляющему входу дешифратора, связанного выходом с входом второго блока памяти, о т л и ч а ю .ад е е с я тем, что,- с целью расширения функциональных возможностей устройства путем одновременного независимого формирс вания временных команд, в него введены коммутатор, первый и второй блоки формирователей импульсов, С SS подключенных входами соответственно к выходам делителя частоты и (/) объекта управления, а выходами - к первым и вторым информационным входам коммутатора, соединенного третьим, информационным входом с третьим выходом первого блока памяти, управляющим входом - с первым выходом генератора тактовых импульсов и управляющим входом второго счетчика импульсов, а выходом - со счетным входом второго счетчика импульсов.

Фиг 2

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Программное временное устройство | 1976 |

|

SU647655A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Авторское свидетельство СССР по заявке 3348057/18-24, кл | |||

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1983-12-23—Публикация

1982-10-22—Подача