Изобретение относится к автомати-,- е и вычислительной технике и может ыть использовано для автоматическоо контроля преобразователей .угла оворота вала в код накапливающего ипа.

Цель изобретения -.повьшение достоверности контроля преобразователей гла поворота вала в код.

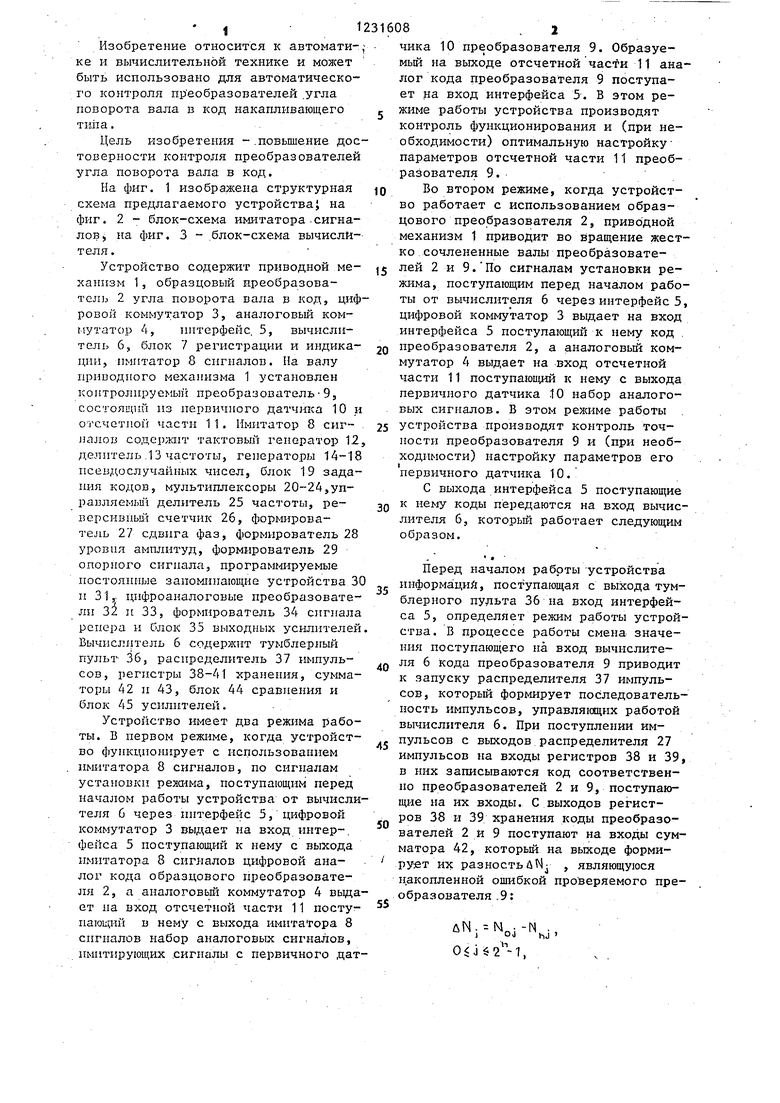

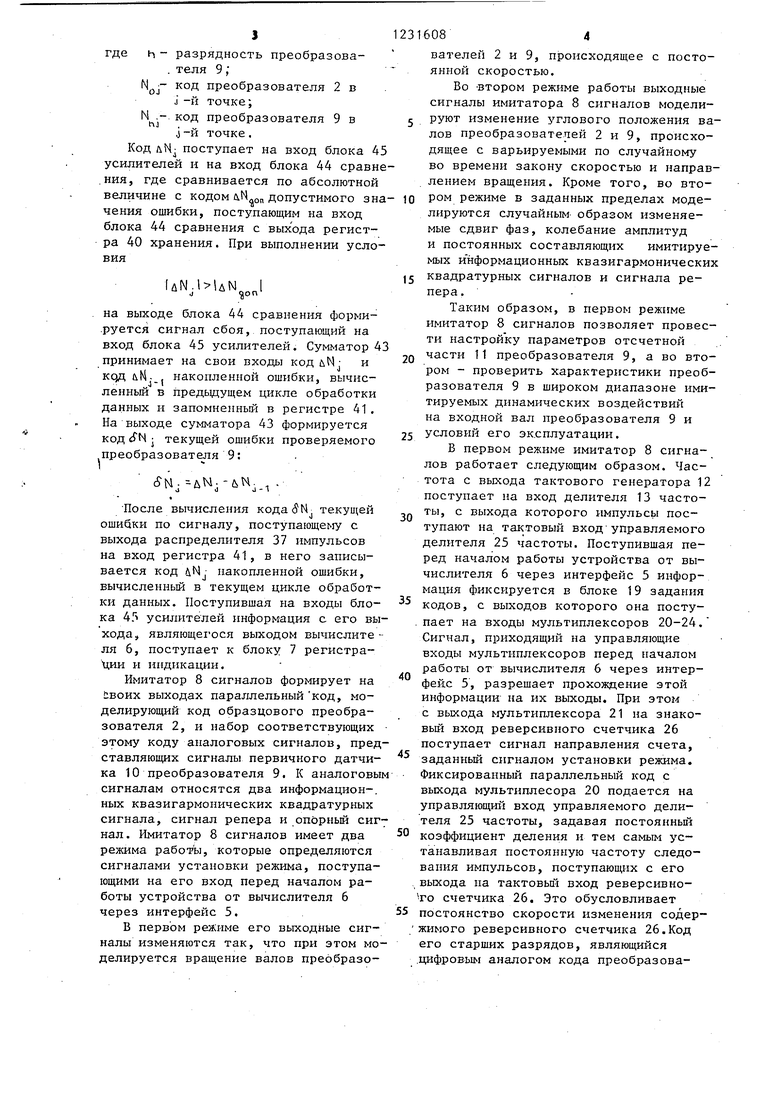

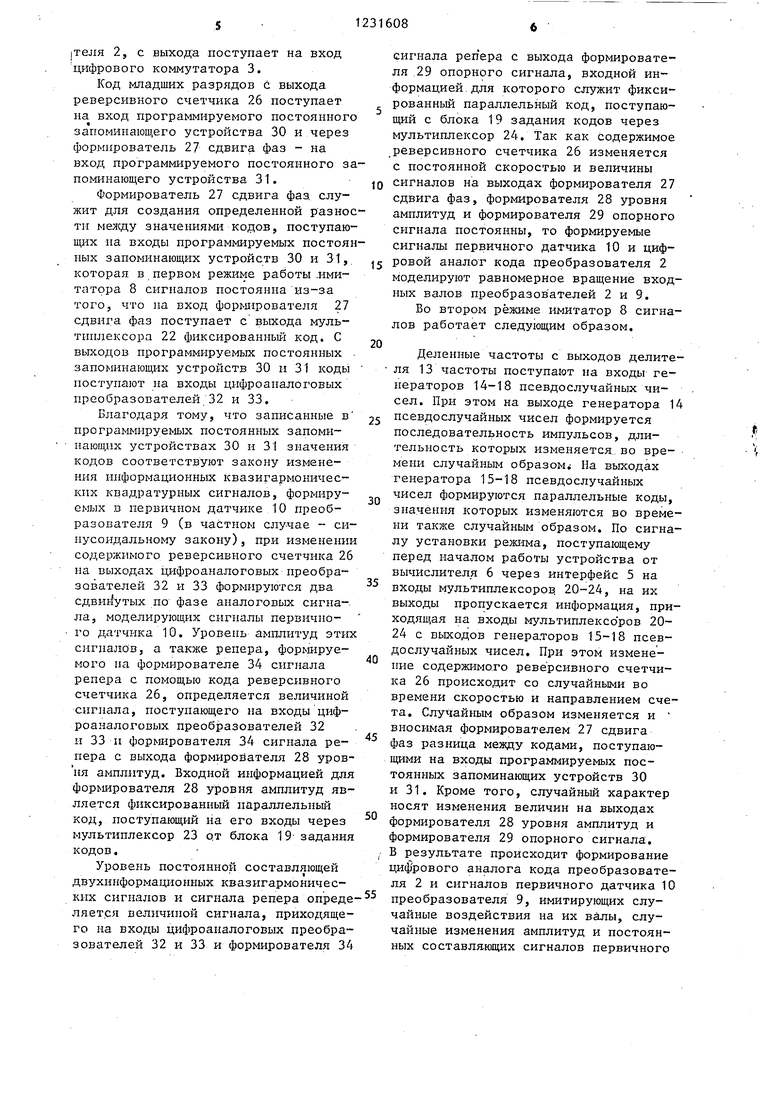

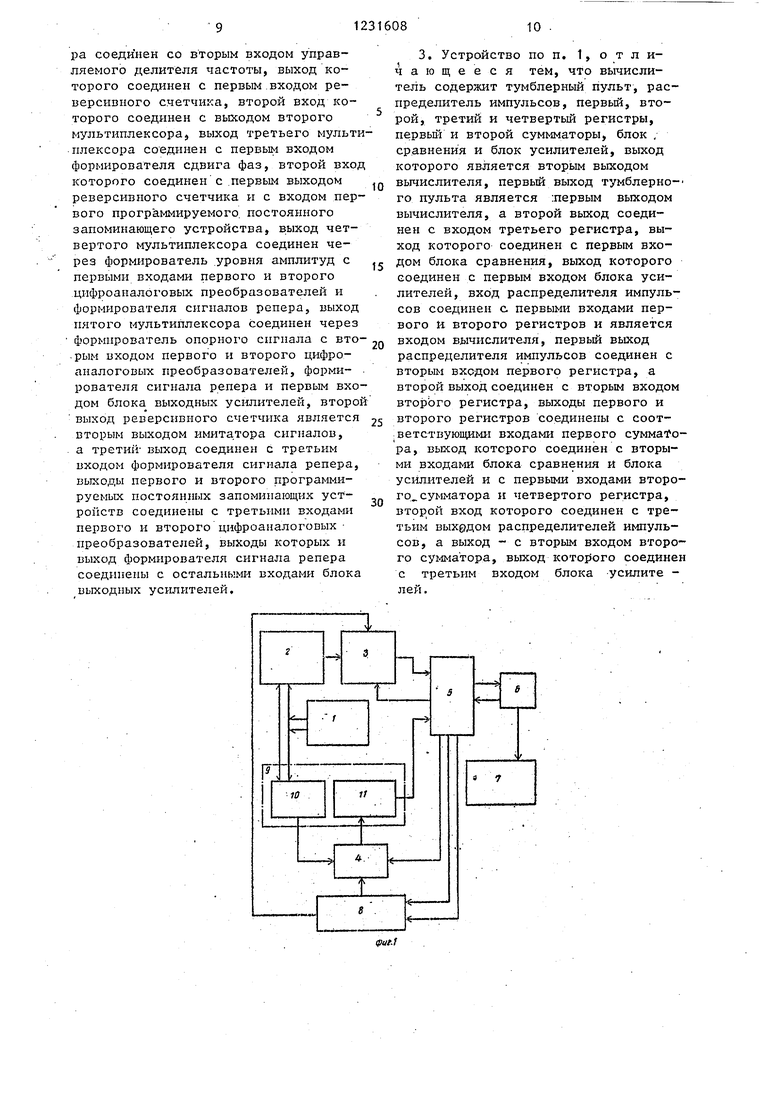

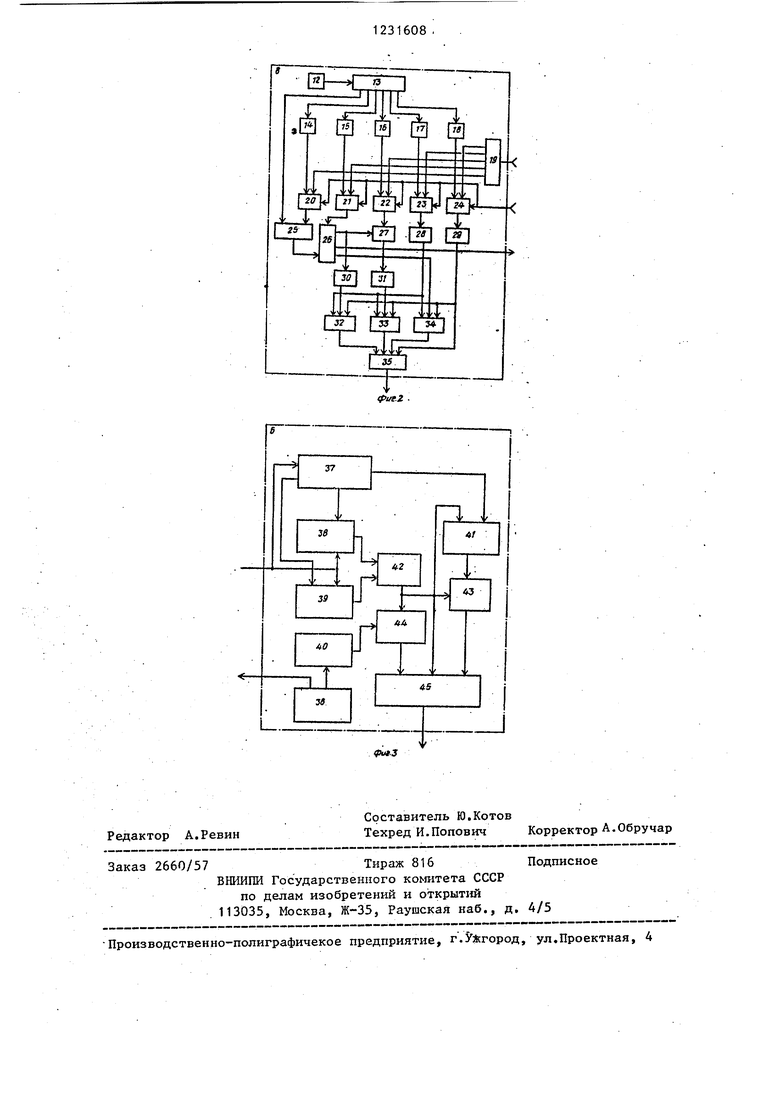

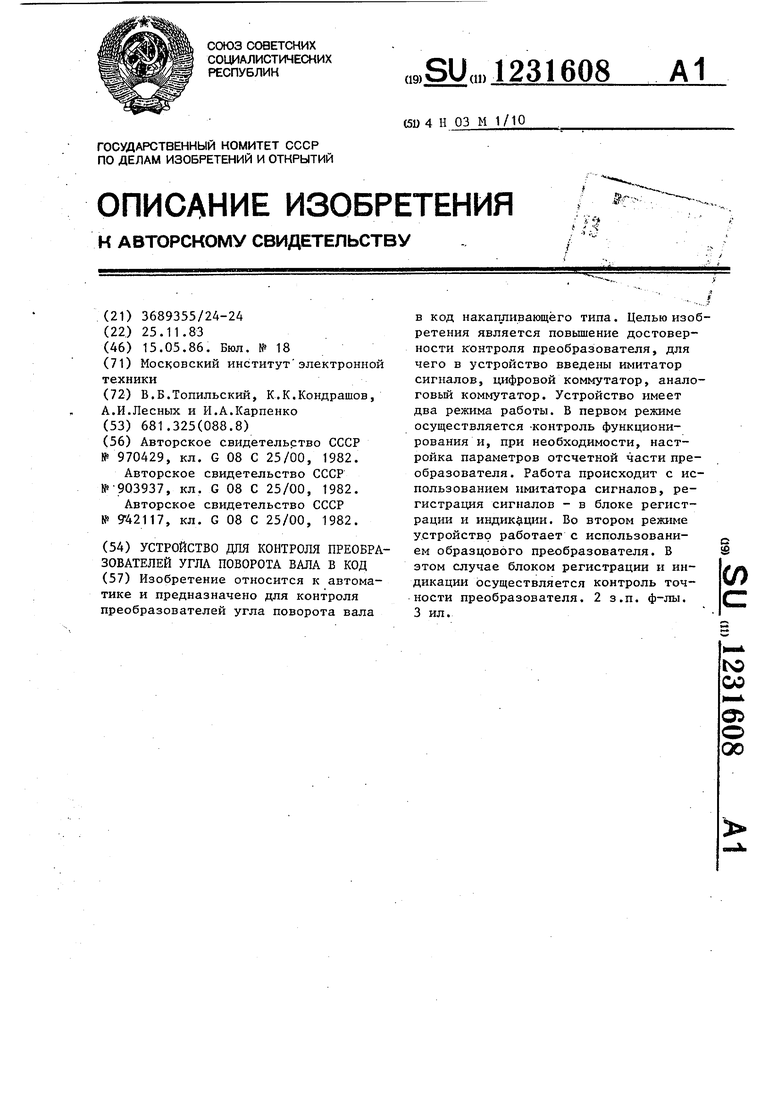

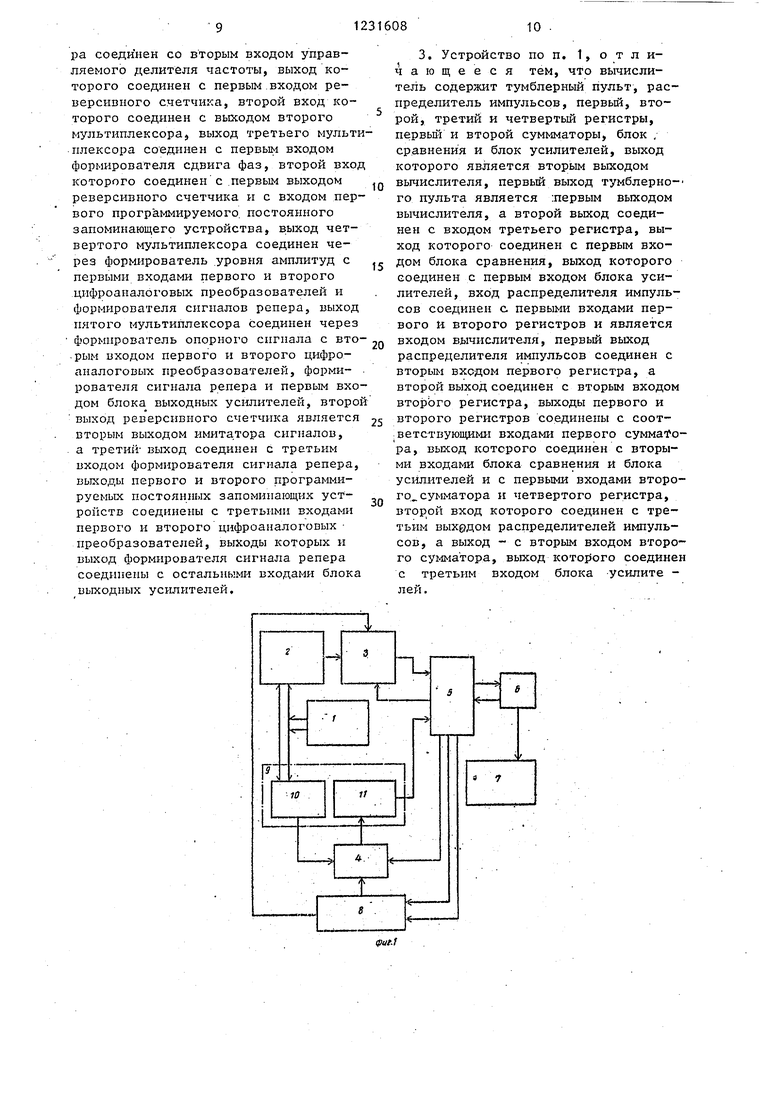

На фиг. 1 изображена структурная схема предлагаемого устройстваJ на фиг. 2 - блок-схема имитатора-сигнаов на фиг. 3 - .блок-схема вычислителя .

Устройство содержит приводной механизм 1, образцовый преобразователь 2 угла поворота вала в код, цифровой коммутатор 3, аналоговый коммутатор 4, интерфейс, 5, вычислитель б, блок 7 регистрации и индикации, имитатор 8 сигналов. На валу приводного механизма 1 установлен контролируемый преобразователь9, состоящий из первичного датчика 10 и отсчетной части 11. Имитатор 8 сиг- . налов содержгг тактовый генератор 12, делитель,13 частоты, генераторы 14-18 псевдослучайных чисел, блок 19 задания кодов, мультиплексоры 20-24,уи- равляемьй делитель 25 частоты, реверсивный счетчик 26, формирователь 27 сдвига фаз, формирователь 28 уровня амплитуд, формирователь 29 опорного сигнала, програм1 Шруемые постоянные запоминающие устройства 30 и 31,. цифроаналоговые преобразователи 32 и 33, формирователь 34 сигнала репера и блок 35 выходных усилителей. Вычислитель 6 содержит тумблерный пульт 36, распределитель 37 импульсов, регистры 38-41 хранения, сумматоры 42 и 43, блок 44 сравнения и блок 45 усилителей.

Устройство имеет два режима работы. В первом режиме, когда устройство функционирует с использованием имитатора 8 сигналов, по сигналам установки релшма, поступающим перед началом работы устройства от вычислителя 6 через интерфейс 5, цифровой коммутатор 3 выдает на вход 1штер-. фейса 5 поступающий к нему с выхода имитатора 8 сигналов цифровой аналог кода образцового преобразователя 2, а аналоговьш коммутатор 4 вьща- ет на вход, отсчетной части 11 поступающий в нему с выхода имитатора 8 сигпалов набор аналоговых сигналов, имитирующих .сигналы с первичного дат1231608

5

0

5

0

5

0

5

0

55

чика 10 преобразователя 9. Образуе- иьй на выходе отсчетной части 11 аналог кода преобразователя 9 поступает на вход интерфейса 5. В этом режиме работы устройства производят контроль функционирования и (при необходимости) оптимальную настройку параметров отсчетной части 11 преобразователя 9.

Во втором режиме, когда устройство работает с использованием образцового преобразователя 2, приводной механизм 1 приводит во вращение жестко сочлененные валы преобразователей 2 и 9. По сигналам установки режима, поступающим перед началом работы от вычислителя 6 через интерфейс 5, цифровой коммутатор 3 выдает на вход интерфейса 5 поступающий к нему код . преобразователя 2, а аналоговьй коммутатор 4 выдает на вход отсчетной части 11 поступаюицш к нему с выхода первичного датчика 10 набор аналоговых сигналов. В этом режиме работы . устройства производят контроль точности преобразователя 9 и (при необходимости) настройку параметров его первичного датчика 10.

С выхода интерфейса 5 поступающие к нему коды передаются на вход вычислителя 6, который работает следующим образом.

Перед началом работы устройства информации, поступающая с выхода тумблерного пульта 36 на вход интерфейса 5, определяет режим работы устройства. В процессе работы смена значения поступающего на вход вычислителя 6 кода преобразователя 9 приводит к запуску распределителя 37 импульсов, которьй формирует последовательность импульсов, управляющих работой вычислителя 6. При поступлении импульсов с выходов распределителя 27 импульсов на входы регистров 38 и 39, в них записываются код соответственно преобразователей 2 и 9, поступающие на их входы. С выходов регистров 38 и 39 хранения коды преобразователей 2 и 9 поступают на входы сумматора 42, который на выходе формирует их разностьuMj , являющуюся накопленной ошибкой проверяемого преобразователя .9:

Ni--NoJ-N,j 0 j $2 -1,

J

где h - разрядность преобразова. теля 9; Njjj- код преобразователя 2 в

j-и точке; М.- код преобразователя 9 в

j-и точке.

Код uNj поступает на вход блока 45 усилителей и на вход блока 44 сравне- .НИН, где сравнивается по абсолютной величине с кодом й. допустимого значения ошибки, поступающим на вход блока 44 сравнения с выхода регистра 40 хранения. При выполнении условия

uN.

оп

на выходе блока 44 сравнения форми- .руется сигнал сбоя, поступающий на вход блока 45 усилителей. Сумматор 4 принимает на свои входы код bNj и код ьН-.. накопленной ошибки, вычис- ленньй в предыдущем цикле обработки данных и запомненный в регистре 41 . На выходе сумматора 43 формируется код N текущей ошибки проверяемого преобразователя 9:

(Ум,--дМ--.,.1 После вычисления , текущей

о

ошибки по сигналу, пocтyпaющe ry с выхода распределителя 37 импульсов на вход регистра 41, в него записывается код uNj накопленной ошибки, вычисленньш в текущем цикле обработки данных. Поступившая на входы блока 43 усилителей информация с его вы хода, являющегося выходом вычислителя б, поступает к блоку 7 регистрации и индикации.

Имитатор 8 сигналов формирует на Своих выходах параллельный код, моделирующий код образцового преобразователя 2, и набор соответствующих этому коду аналоговых сигналов, представляющих сигналы первичного датчика 10 преобразователя 9. К аналоговы сигналам относятся два информацион-. ных квазигармонических квадратурных сигнала, сигнал репера и опорньй сигнал. Имитатор 8 сигналов имеет два режима работы, которые определяются сигналами установки режима, поступающими на его вход перед началом работы устройства от вычислителя 6 через интерфейс 5.

В первом режиме его выходные сигналы изменяются так, что при этом моделируется вращение валов преобразо316084

вателей 2 и 9, происходящее с постоянной скоростью.

Во -втором режиме работы выходные сигналы имитатора 8 сигналов модели- 5 руют изменение углового положения валов преобразователей 2 и 9, происходящее с варьируемыми по случайному во времени закону скоростью и направлением вращения. Кроме того, во вто0 ром режиме в заданных пределах моделируются случайным образом изменяемые сдвиг фаз, колебание амплитуд и постоянных составляющих имитируемых и нформационных квазигармонических

5 квадратурных сигналов и сигнала репера .

Таким образом, в первом режиме имитатор 8 сигналов позволяет провести настройку параметров отсчетной

0 части 11 преобразователя 9, а во втором - проверить характеристики преобразователя 9 в широком диапазоне имитируемых динамических воздействий на входной вал преобразователя 9 и

5 условий его эксплуатации.

Б первом режиме имитатор 8 сигналов работает следующим образом. Частота с выхода тактового генератора 12 поступает на вход делителя 13 частод ты, с выхода которого импульсы поступают на тактовый вход управляемого делителя 25 частоты. Поступившая перед началом работы устройства от вычислителя 6 через интерфейс 5 информация фиксируется в блоке 19 задания

кодов, с выходов которого она посту- . пает на входы мультиплексоров 20-24. Сигнал, приходящий на управляющие входы мультиплексоров перед началом работы от вычислителя 6 через интерфейс 5, разрешает прохождение этой информации на их выходы. При этом с выхода мультиплексора 21 на знаковый вход реверсивного счетчика 26 поступает сигнал направления счета, заданньш сигналом установки режима. Фиксированньш параллельный код с выхода мультиплесора 20 подается на управляющий вход управляемого делителя 25 частоты, задавая постоянньй

0 коэффициент деления и тем самым устанавливая постоянную частоту следования импульсов, поступающих с его выхода на тактовьш вход реверсивно- го счетчика 26. Это обусловливает

5 постоянство скорости изменения содер- жимого реверсивного счетчика 26.Код его старших разрядов, являющийся .цифровым аналогом кода преобразова0

5

|теля 2, с выхода поступает на вход цифрового коммутатора 3.

Код младших разрядов с выхода реверсивного счетчика 26 поступает иа вход программируемого постоянного запоминающего устройства 30 и через формирователь 27 сдвига фаз - на вход программируемого постоянного запоминающего устройства 31.

Формирователь 27 сдвига фаз. служит для создания определенной разности между 3Ha4emmMii кодов, поступающих на входы программируемых постоянных запоминающих устройств 30 и 31,, которая в первом режиме работы .имитатора 8 сигналов постоянна из-за того, что на вход формирователя 27 сдвига фаз поступает с выхода мультиплексора 22 фиксированный код. С выходов программируемых постоянных . запоминающих устройств 30 и 31 коды поступают на входы цифроаналоговых преобразователей 32 и 33.

Благодаря тому, что записанные в программируемых постоянных запоминающих устройствах 30 и 31 значения кодов соответствуют закону изменения информационных квазигармонических квадратурных сигналов, формируемых в первичном датчике 10 преобразователя 9 (в частном случае - синусоидальному закону), при изменении содержимого реверсивного счетчика 26 на выходах цифроаналоговых преобразователей 32 и 33 формируются два сдвиь{утых по фазе аналоговых сигнала, моделирующих сигналы первично- го датчика 10. Уровень амплитуд этнх сигналов, а также репера, формируемого па формирователе 34 сигнала репера с помощью кода реверсивного счетчика 26, определяется величиной сигнала, поступающего на входы цифроаналоговых преобразователей 32 и 33 и формирователя 34 сигнала репера с выхода формирователя 28 уров- ня амплитуд. Входной информацией для форьшрователя 28 уровня амплитуд является фиксированный параллельньш код, поступающий на его входы через мультиплексор 23 от блока 19 задания кодов.

Уровень постоянной составляющей двухинформационных квазигармонических сигналов и сигнала репера опреде ляется величиной сигнала, приходящего на входы цифроапалоговых преобразователей 32 и 33 и формирователя 34

10

15

20

25

3D

35

40

45

50

55

сигнала реп ера с выхода формирователя 29 опорного сигнала, входной информацией для которого служит фиксированный параллельный код, поступающий с блока 19 задания кодов через мультиплексор 24. Так как содержимое реверсивного счетчика 26 изменяется с постоянной скоростью и величины сигналов на выходах формирователя 27 сдвига фаз, формирователя 28 уровня амплитуд и формирователя 29 опорного сигнала постоянны, то формируемые сигналы первичного датчика 10 и цифровой аналог кода преобразователя 2 моделируют равномерное вращение входных валов преобразов ателей 2 и 9.

Во втором режиме имитатор 8 сигналов работает следующим образом.

Деленные частоты с выходов делителя 13 частоты поступают на входы генераторов 14-18 псевдослучайных чисел. При этом на выходе генератора 14 псевдослучайных чисел формируется последовательность импульсов, длительность которых изменяется во вре- мени случайным образом Иа выходах генератора 15-18 псевдослучайных чисел формируются параллельные коды, значения которых изменяются во времени также случайным образом. По сигналу установки , поступающему перед началом работы устройства от вычислителя 6 через интерфейс 5 на входы мультиплексоров, 20-24, на их выходы пропускается информация, приходящая на входы мультиплексоров 20- 24 с выходов генера.торов 15-18 псевдослучайных чисел. При этом изменение содержимого реверсивного счетчика 26 происходит со случайными во времени скоростью и направлением счета. Случайным образом изменяется и вносимая формирователем 27 сдвига фаз разница между кодами, поступающими на входы программируемых постоянных запоминающих устройств 30 и 31. Кроме того, случайный характер носят изменения величин на выходах формирователя 28 уровня амплитуд и формирователя 29 опорного сигнала. В результате происходит формирование ци( рового аналога кода преобразователя 2 и сигналов первичного датчика 10 преобразователя 9, имитирующих случайные воздействия на их валы, случайные изменения амплитуд и постоянных составляющих сигналов первичного

датчика 10, а также сдвига фаз между ними „

Предлагаемое устройство обеспечивает повышение достоверности контроля за счет введения в его,состав реализованного с помощью стандартных цифровых и цифроаналоговых схем имитатора 8 сигналов, позволяющего проводить комплексные испытания наиболе ненадежной отсчетной ча сти 11 преобразователя 9 .угла поворота вала в код накапливающего типа путем формирования набора цифровых и аналоговых сигналов, моделирующих как разнооб- разные динамические входные воздействия на валы преобразователей 2 и 9 в наиболее жестком режиме случайного знакопеременного их движения, так и изменения сигналов первичного датчи- ка проверяемого преобразователя (амплитуд, фаз, постоянных составляющих) возникающих в процессе эксплуатации из-за старения электронных компонентов преобразователя, изменения темпе- ратурных режимов, износа его механических узлов и т.п. Кроме того, введение в состав устройства имитатора 8 сигналов позволяет в необходимых случаях проводить такую настрой- ку параметров отсчетной части 11 (например, уровней срабатывания компара- 1 оров, величин задержек цифровых элементов) , которая исключает появление сбоев при работе с реальными сигна-- лами. Наконец, наличие предварительно настроенной с помощью имитатора 8 сигналов отсчетной части 11 позволяет проводить регулировку параметров первичного датчика 10, уменьшая тем самым вероятность возникновения сбойных ситуаций при эксгшуатации преобразователя 9.

Формула изобретения

1. Устройство для контроля преобразователей угла поворота вала в код, содержащее приводной механизм, вал которого соединен с валом образцово- го преобразователя и предназначен для соединения с валом контролируемого преобразователя, интерфейс, первый выход которого соединен с входом вычислителя, первый выход которого.сое-55 динен с первым входом интерфейса, второй выход - с входом блока регистрации и индикации, о т л и ч а ю щ ею5 20 25 зо

35

0

5

5 с я тем, что, с целью повышения достоверности контроля, в него введены имитатор сигналов, цифровой коммутатор и аналоговьш коьпчутатор, первьй вход которого является первым входом устройства, второй вход соединен с вторым выходом интерфейса, а выход предназначен для подключения входа контролируемого преобразователя, второй вход интерфейса является вторым входом устройстваJ третий и четвер- тьш выходы интерфейса соединены с первым- и вторым входами имитатора сигналов, первый выход которого соединен с первым входом цифрового коммутатора, а второй выход - с третьим входом аналогового коммутатора, второй вход цифрового коммутатора соединен с выходом образцового преобразователя, третий вход - с пятым выходом интерфейса, а выход - с третьим входом интерфейса.

2. Устройство по п. 1, о т л и- чающееся тем, что имитатор сигналов содержит тактовый генератор, делитель частоты, первый, второй, третий, четвертьш и пятый генераторы псевдослучайных чисел, блок задания кодов, первьп, второй, третий, четвертый и пятьй мультиплексоры, управляемьШ делитель частоты, реверсивный счетчик, формирователь сдвига фаз, формирователь уровня амплитуд, формирователь опорного сигнала, первое и второе программируемые- постоянные запоминающие устройства, первый и второй цифроаналоговые преобразователи, формирователь сигнала репера и блок выходных усилителей, выход,которого является первым выходом имитатора сигналов, выход тактового генератора соединен с входом делителя частоты, первый выход которого соединен с первым входом управляемого делителя частоты, остальные выходы соединены со входами первого, второго, третьего, четвертого и пятого генераторов псевдослучайных чисел, выходы которых соединены с первыми входами одноименных мультиплексоров, вторые входы которых соединены с выходами блока задания кодов, вход которого является первым входом имитатора сигналов, третьи входы первого, второго, третьего, четвертого и пятого мультиплексоров объединены и являются вторым входом имитатора сигналов, выход первого мультиплексо10

15

a соединен со вторым входом управяемого делителя частоты, выход которого соединен с первым входом реверсивного счетчика, второй вход которого соединен с выходом второго мультиплексора, выход третьего мультиплексора соединен с первым входом формирователя сдвига фаз, второй вход которого соединен с первым выходом реверсивного счетчика и с входом первого программируемого, постоянного запоминающего устройства, выход четвертого мультиплексора соединен через формирователь уровня амплитуд с первыми входами первого и второго цифроаналоговых преобразователей и формирователя сигналов репера, выход пятого мультиплексора соединен через формирователь опорного сигнала с вто- . рым входом первого и второго цифро- аналоговых преобразователей, форми- рователя сигнала репера и первым входом блока выходных усилителей, второй выход реверсивного счетчика является 25

вторым выходом имита.тора сигналов, а третий- выход соединен с третьим входом формирователя сигнала репера, выходы первого и второго программируемых постоянных запоминающих устройств соединены с третьими входами первого и второго цифроаналоговых преобразователей, выходы которых и выход формирователя сигнала репера с остальными входами блока выходных усилителей.

30

10

15

. 5

0

3. Устройство по п. 1, о т л и- чающееся тем, что вычислитель содержит тумблерный пульт, распределитель импульсов, первьш, второй, третий и четвертый регистры, первьш и второй суммматоры, блок , сравнения и блок усилителей, выход которого является вторым выходом вычислителя, первый выход тумблерно- го пульта является :первым выходом вычислителя, а второй выход соединен с входом третьего регистра, выход которого соединен с первым входом блока сравнения, выход которого соединен с первым входом блока усилителей, вход распределителя импульсов соединен с первыми входами первого И: второго регистров и является входом вычислителя, первый выход распределителя импульсов соединен с вторым входом первого регистра, а второй выход соединен с вторым входом второго регистра, выходы первого и второго регистров соединены с соот- :ветствующими входами первого сумматора, выход которого соединен с вторыми входами блока сравнения и блока усилителей и с первыми входами второго сумматора и четвертого регистра, второй вход которого соединен с третьим ВЫХ0ДОМ распределителей импульсов, а выход - с вторым входом второго сумматора, выход которого соединен с третьим входом блока усилите - лей.

| название | год | авторы | номер документа |

|---|---|---|---|

| Спироанализатор | 1986 |

|

SU1391621A1 |

| Устройство автоматизированной подготовки программ для станков с ЧПУ | 1986 |

|

SU1354160A1 |

| УПРАВЛЯЮЩИЙ АППАРАТНО-ПРОГРАММНЫЙ КОМПЛЕКС ДЛЯ ОБРАБОТКИ РАДИОЛОКАЦИОННОЙ ИНФОРМАЦИИ | 2001 |

|

RU2222028C2 |

| ИМИТАТОР УГЛА ПОВОРОТА АНТЕННЫ РЛС | 1987 |

|

SU1841003A1 |

| Преобразователь угла поворота вала в код | 1982 |

|

SU1022202A1 |

| Устройство для контроля канала связи | 1985 |

|

SU1249711A1 |

| СПОСОБ ГЕОЭЛЕКТРОРАЗВЕДКИ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1991 |

|

RU2006886C1 |

| АВТОМАТИЗИРОВАННОЕ РАБОЧЕЕ МЕСТО ОПЕРАТОРА УПРАВЛЕНИЯ ВОЗДУШНЫМ ДВИЖЕНИЕМ | 2001 |

|

RU2219586C2 |

| Фазометр мгновенных значений | 1981 |

|

SU980015A1 |

| Устройство для обработки и отображения видеоинформации | 1988 |

|

SU1748284A1 |

Изобретение относится к автоматике и предназначено для контроля преобразователей угла поворота вала в код накапливающего типа. Целью изобретения является повьшение достоверности контроля преобразователя, для чего в устройство введены имитатор сигналов, цифровой коммутатор, аналоговый коммутатор. Устройство имеет два режима работы. В первом режиме осуществляется -контроль функционирования и, при необходимости, настройка параметров отсчетной части преобразователя. Работа происходит с использованием имитатора сигналов, регистрация сигналов - в блоке регистрации и индикации. Во втором режиме у.стройствр работает с использованием образцового преобразователя. В этом случае блоком регистрации и индикации осуществляется контроль точности преобразователя. 2 з.п. ф-лы. 3 ил. § (Л ьо со О5 о СХ)

| Устройство для контроля преобразователей угла поворота вала в код | 1981 |

|

SU970429A1 |

| Топка с несколькими решетками для твердого топлива | 1918 |

|

SU8A1 |

| Устройство для контроля преобразователей угла поворота вала в код | 1980 |

|

SU903937A1 |

| Топка с несколькими решетками для твердого топлива | 1918 |

|

SU8A1 |

| Разборный с внутренней печью кипятильник | 1922 |

|

SU9A1 |

| Топка с несколькими решетками для твердого топлива | 1918 |

|

SU8A1 |

Авторы

Даты

1986-05-15—Публикация

1983-11-25—Подача