I

Изобретение относится к вычислительной технике, может быть использовано для суммирования и вычитания импульсньох последовательностей.

Известен реверсивный счетчик, содержащий разряды, первый и второй тактовые входы каждого из которых соединены соответственно с шинами сложения и вычитания, а выходы переноса и заема соединены соответственно с входами первой и второй групп входов разрешения счета всех остальных разрядов, а каждый разряд содержит первый, второй, третий и четвертый элементы И-НЕ, инвертор, первый и второй элементы И-ИЛИ-НЕ, первые входы первого и второго элементов PIHE соединены с выходами соответствен но второго и первого элементов И-НЕ, выход первого элемента И-НЕ соединен с первым входом третьего элемента ИНЕ, выход которого соединен с первым входом четвертого элемента И-НЕ,выход которого соединен с выходом переноса разряда, входом инвертора и первыми входами первой и второй групп входов по И первого элемента И-ИЛИНЕ, выход которого соединен с вторым входом четвертого элемента И-НЕ и вторым входом второго элемента И-НЕ,

2

выход инвертора соединен с выходом заема разряда и первыми входами первой и второй групп входов по И второго элемента Д-НЕ, выход которого соединен с вторым входом третьего элемента И-НЕ, и вторыи1 входом первого элемента И-НЕ, вторые входы первых входов по И первого и второго элементов И-ИЛИ-НЕ соединены с первым

10 тактовым входом разряда, вторые входы вторых групп входов по И первого и второго элементов И-ИЛИ-НЕ соединены с вторым тактовым входом разряда, i+2-e входы первых групп входов

15 групп входов по И первого и второго э.лементов И-ИЛИ-НЕ К-го разряда, где J1 1,...K соединены соответственно с входами первой группы входов разрешения счета этого К-го разряда,

20 вторая группа входов разрешения счета которого соединена с -i + 2-ми входами вторых групп входов по И первого и второго элементов И-ИЛИ-НЕ того же разряда i.

25

Недостатком этого реверсивного счетчика являются ограниченные функциональные возможности.

Целью изобретения является расширение функциональных возможностей

30 реверсивного счетчика.

Поставленная цель достигается тем, то в реверсивный счетчик, содержаий разряды, первый и второй тактовые ходы каждого из которых соединены оответственно с шинами сложения и ычитания, а выходы переноса и эаема оединены соответственно с входами ервой и второй групп входов разрешеия счета всех остальных разрядов,а аждый разряд содержит первый, второй, третий и четвертый элементы И-НЕ, инвертор, первый и второй элементы И-ИЛИ-НЕ, первые входы первого и второго элементов И-НЕ соединены с выходами соответственно второго и первого элементов И-НЕ, выход первого элемента соединен с первым входом третьего элемента И-НЕ, выход которого соединен с первым входом четвертого элемента И-НЕ, выход которого соединен с выходом переноса разряда, входом инвертора и первыми входами первой и второй групп входов по И первого элемента И-ИЛИ-НЕ, выход которого соединен с вторым входом четвертого элемента Й-НЕ и вторым входом второго элемента И-НЕ, выход инвертора соединен с выходом заема разряда и первыми входами первой и второй групп входов по И второго элемента И-НЕ, выход которого соединен с вторым входом третьего элемента И-НЕ и вторым входом первого элемента И-НЕ, вторые входы первых групп входов по И первого и второго элементов И-ИЛИ-НЕ соединены с первым тактовым входом разряда, вторые входы групп входов и по И первого и второго элементов И-ИЛИ-НЕ соединены с вторым тактовым входом разряда, i+2-e входы первых групп входов групп по И первого и второго элементов И-ИЛИ-НЕ К-го разряда, где i 1,...К соединены соответственно с входами первой группы входов разрешения счета, этого К-го разряда, вторая группа входов разрешения счета которого соединена с +2-ми входами вторах групп входов по И первого и второго элементов И-ИЛИ-НЕ того же разряда, введены первый и второй дополнительные элементы И-НВ, входы первого дополнительного элемента И-НН соединеHLJ соответственно с выходами переноса второго и третьего разрядов и шиной сложения, а также с управляющей шиной, которая соединена с входом второго дополнительного элемента ИНЕ,,остальные входы которого соединены С входами заема первого, второго и третьего разрядов, выход первого дополнительного элемента И-НЕ соединен с третьими входами второго и четвертого элементов И-НЕ, а также с третьими входами первых групп входов по И первого и второго элементов ИИЛИ-НЕ первого разряда, четвертый вход первой группы входов по И второго элемента И-ИЛИ-НЕ которого соединей с выходом второго дополнительного элемента И-НЕ.

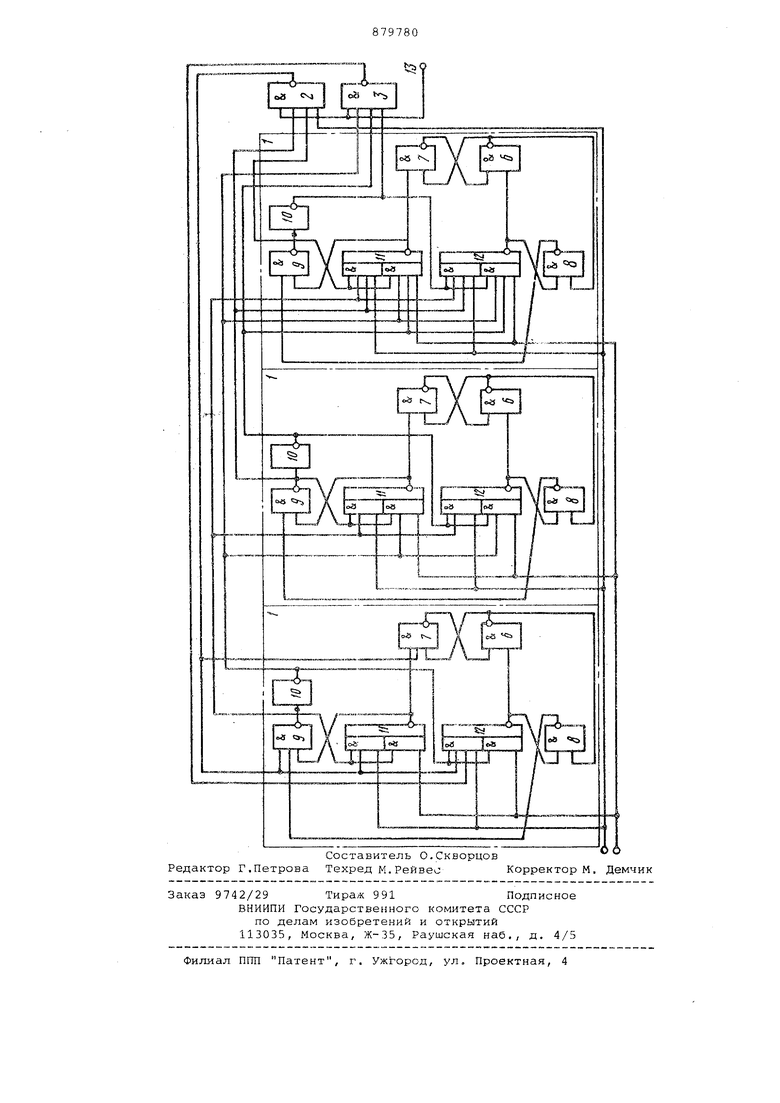

Структурная схема peвepcиБf oгo счетчика показана на чертеже.

Реверсивный счетчик содержит разряды 1 и первый 2 и второй 3 дополнительные элементы И-НЕ, первый и второй тактовые входы каждого разряда 1 из которых соединены соответственно с шинами сложения 4 и вычитания 5, выходы переноса и заема соединены соответственно с входдами первой и второй групп входов разрешения счета всех остальных разрядов, а каждый рязряд 1 содержит первый б, второй 7, третий 8 и четвертый 9 элементы И-НЕ, инвертор -10 и первый 11 и второй 12 элементы И-ИЛИ-НЕ, первые входы первого 6 и второго 7 элементов И-НЕ соединекь с выходами соот-ветственно второго 7 и первого 6 элементов К-НЕ, вихсд элемента И-НЕ 6 соединен с первым входом элемента ИНЕ 8, выход которого соединен с первым входом элемента И-НЕ 9, выход которого соединен с выходом переноса разряда, входом инвертора 10 и первыми входами первой и второй групп входов по И элемента И-ИЛИ-НЕ 11,выход которого соединен с вторым входом элемента И-НЕ 9 и вторым входом элемента И-НЕ 7, выход инвертора 10 соединен с выходом заема разряда и первыми входами первой и второй груп входов по И второго элемента И-НЕ 12 выход которого соединен с вторьи входом элемента И-НЕ 8 и вторым входом элемента И-НЕ 6, вторые входы первых групп входов по И элементов И-ИЛИ-НЕ 11 и 12 соединены с первым тактовым входом разряда, вторые входы вторых групп входов по И элементов И-ИЛИ-НЕ 11 и 12 соединены с вторым тактовым входом разряда, -i входы первых групп входов групп входов по И элементов И-ИЛИ-НЕ 11 и 12 К-го разряда где; -1 1, , „ .К, соответственно с входами первой группы входов разрешения сче;та этого К -го разряда, вторая группа входов разрешения счета которого соединена с i +2-ми входами вторых групп входов по И элементов ИИЛИ НЕ 11 и 12 того же разряда.

Входы элемента И-НЕ 2 соединены соответственно с выходами переноса второго и третьего разрядов 1 и шино 4, а также с управляющей шиной 13, которая соединена с входом элемента И-НЕ 3, остальные входы которого соединены с выходами заема первого,второго и третьего разрядов 1, выход элемента И-НЕ 11 соединен с третьими входами второго 7 и четвертого 9 элементов И-НЕ, а также с третьими входами первых групп входов по И элементов И-ИЛИ-НЕ 11 и 12 первого разряда четвертый вход первой группы входов по И элемента И-ИЛИ-НЕ 12 которого соединен с выходом элемента И-НЕ,

Реверсивный счетчик работает следующим образом.

В режиме обычного двоичного счета на шину 13 подан сигнал, равный логическому нулю, который, поступая на входы элементов И-НЕ 2 и 3, закрывает последние и на выходах этих элементов будет постоянно высокий уровень напряжения. Следовательно, элементы И-НЕ 2 и 3 не влияют на работу реверсивного счетчика, поэтому при поступлении импульсов на шину 4,счетчик работает в режиме суммирования, а при поступлении импульсов на шину 5 счетчик работает в режиме вычитания .

В режиме работы счетчика в качестве реверсивного делителя частоты по модулю 7 на шину 13 подан сигнал,равный логической единице. В этом случае элемент И-НЕ 2 корректирует работу счетчика в режиме суммирования, а элемент И-НЕ 3 - в режиме вычитания.

Действительно, допустим, в начальный момент времени счетчик находится в нулевом состоянии (н.а выходных элементов И-НЕ 6 низкий уровень напряжения) , на шинах 4 и 5 также низкий уровень напряжения.

. При появлении на шине 4 импульсов положительной полярности осуществляется суммирование поступающих импульсов , при этом после прихода шестого импульса первый разряд 1 устанавливается в нулевое состояние, а второй и третий - в единичное состояние. Следовательно, на выходах элементов И-НЕ 9 второго и третьего разрядов устанавливается высокий уровень напряжения, подготавливая элемент И-НЕ 2 к срабатыванию.

С приходом седьмого импульса сложения на выходе элемента И-НЕ 2 появляется сигнал, равный логическому нулю, который закрывает элементы 9 и 12 и устанавливает первый разряд 1 в нулевое состояние. Поскольку на выходе элемента И-НЕ 9 первого разряда 1 появляется сигнал, равный логической единице, то второй и третий разряды устанавливаются в нулевое состояние, и счетчик возвращается в исходное состояние. Таким образом, осуществляется деление входной последовательности импульсов на семь в ( режиме суммирования.

В режиме вычитания, в момент,когда счетчик находится в нулевом состоянии на выходах инверторов 10 всех разрядов-логическая единица, открывается элемент И-НЕ 3 на выходе этого

элемента появляется сигнал, равный логическому нулю, который закрывает первую группу входов по И элемента И-ИЛИ-НЕ 12 первого разряда счетчика. Следовательно, с приходом по шине 5 импульса вычитания второй и третий разряды счетчика устанавливаются в единичное состояние, а первый разряд, останется в нулевом состоянии. Далее с приходом импульсов вычитания осуществляется вычитание содержимого

0 счетчика и с приходом седьмого имп ульса вычитания счетчик устанавливается в исходное состояние.

Так осуществляется деление входной последовательности импульсов на

5 семь в режиме вычитания.

Введение дополнительных элементов и новых связей в счетчике позволяет расширить функциональные возможности устройства, а именно позволяет

0 не только осуществить обычный двоичный счет, но и реверсионный пересчёт, поступающих импульсов по модулю семь, что важно для целого класса устройств дискретной автоматики и вычислительной техники.

5

Формула изобретения

Реверсивный счетчик по авт. св.

0 №799147, отличающийся тем, что, с целью расширения функциональных возможностей, в него введены первый и второй дополнительные элементы И-НЕ, входы первого дополни5тельного элемента И-НЕ соединены соответственно с выходами переноса вто-рого и третьего разрядов и шиной сложения, а также с управляющей шиной, которая соединена с входом второго

0 дополнительного элемента И-НЕ,остальные входы которого соединены с выходаг -i заема первого, второго и третьего разрядов, выход первого дополнительного элемента И-НЕ соединен с

5 третьими входами второго и четвертого элементов И-НЕ, а также с третьими входами первых групп входов по И первого и второго элементов И-ИЛИ-НЕ первого разряда, четвертый вход первой группы входов по И второго эле0мента И-ИЛИ-НЕ которого соединен с выходом второго дополнительного элемента И-НЕ.

Источники информации, принятые во внимание при экспертизе

5

1. Авторское свидетельство СССР № 799147, кл. Н 03 К 23/02, 14.04.75 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Оптоэлектронный счетчик импульсов | 1985 |

|

SU1267606A1 |

| Реверсивный счетчик с групповым переносом | 1980 |

|

SU1005318A2 |

| Устройство для преобразования кодов | 1977 |

|

SU744544A1 |

| Реверсивный счетчик с групповым переносом | 1981 |

|

SU1007200A2 |

| Устройство для формирования импульсов | 1984 |

|

SU1205273A1 |

| Устройство для сложения в двоичной и в двоично-десятичной системе счисления | 1985 |

|

SU1273919A1 |

| Умножитель частоты следования импульсов | 1986 |

|

SU1432754A1 |

| Реверсивный счетчик | 1973 |

|

SU476687A1 |

| Устройство символьной синхронизации | 1990 |

|

SU1775869A1 |

| Разностный счетчик импульсов | 1980 |

|

SU936433A1 |

Авторы

Даты

1981-11-07—Публикация

1980-03-21—Подача