1

Изобретение относится к вычислительной технике и предназначено для суммирования илн вычитания последовательности входных импульсов.

Известен реверсивный счетчик на элементах И - НЕ, каждый разряд которого выполнен на триггере памяти, двух коммутационных триггерах и двух схемах И - НЕ, причем единичный выход триггера памяти соединен с единичным входом первого коммутационного триггера, нулевой выход которого соединен с единичным входом триггера памяти, а единичный выход первого коммутационного триггера соединен с нулевым входом второго коммутационного триггера и со входом первой схемы И - НЕ. Нулевой выход второго коммутационного триггера соединен со входом второй схемы И - НЕ, а единичный выход второго коммутационного триггера соединен с нулевыми входами триггера памяти и первого коммутационного триггера и со входом первой схемы И - НЕ. Шина разрешения сложения соединена со входом первой схемы И - НЕ, шина разрешения вычитания соединена со входом второй схемы И - НЕ, а шина импульса счета соединена с нулевым входом первого коммутационного триггера и с единичным входом второго коммутационного триггера. Выход первой схемы И - НЕ соединен с нулевым входом первого коммутационного триггера следующего разряда, выход второй схемы И - НЕ соединен с нулевым входом первого и с единичным входом второго коммутационных триггеров следующего разряда.

Недостатком известного реверсивного счетчика является большое чнс.Ю межразрядиых связей и сложность. Цель изобретения - упрО1денне устройства.

Ноставленная цель достигается тем, что выход первой схемы И - НН соединен с едиН11ЧНЫМ входом первого коммутационного триггера следующего разряда, выход второй схемы И - НЕ соединен с нулевым входом

второго коммутационного триггера следующего разряда.

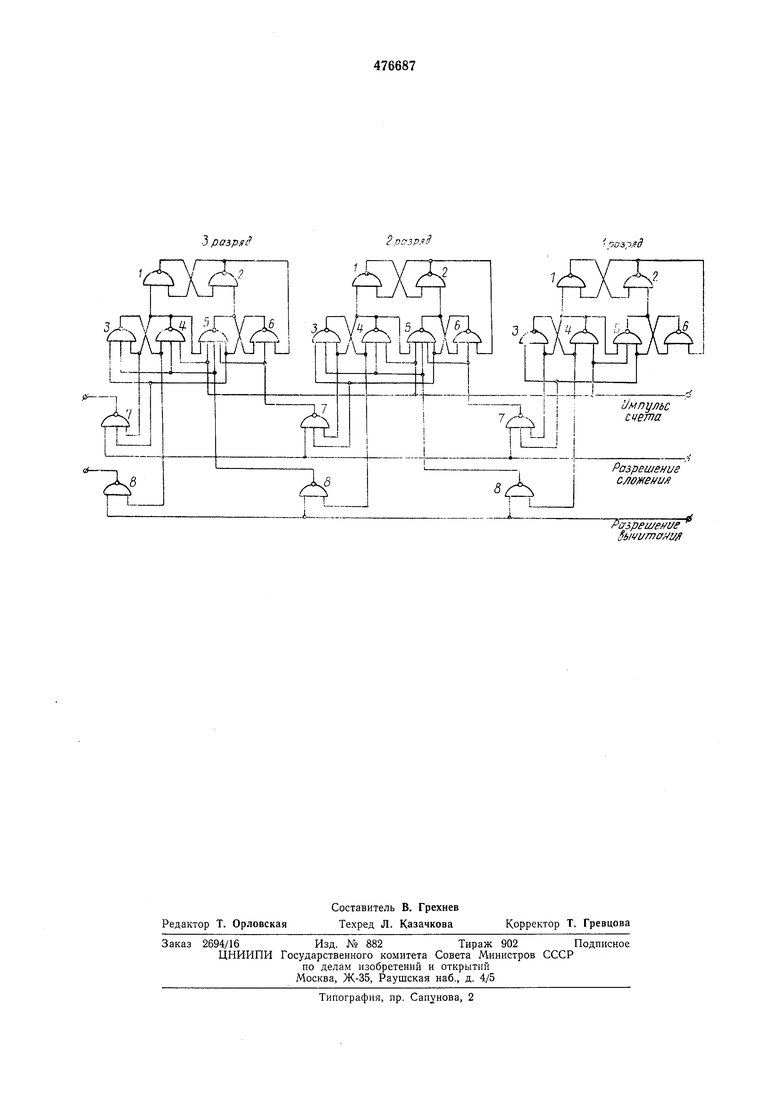

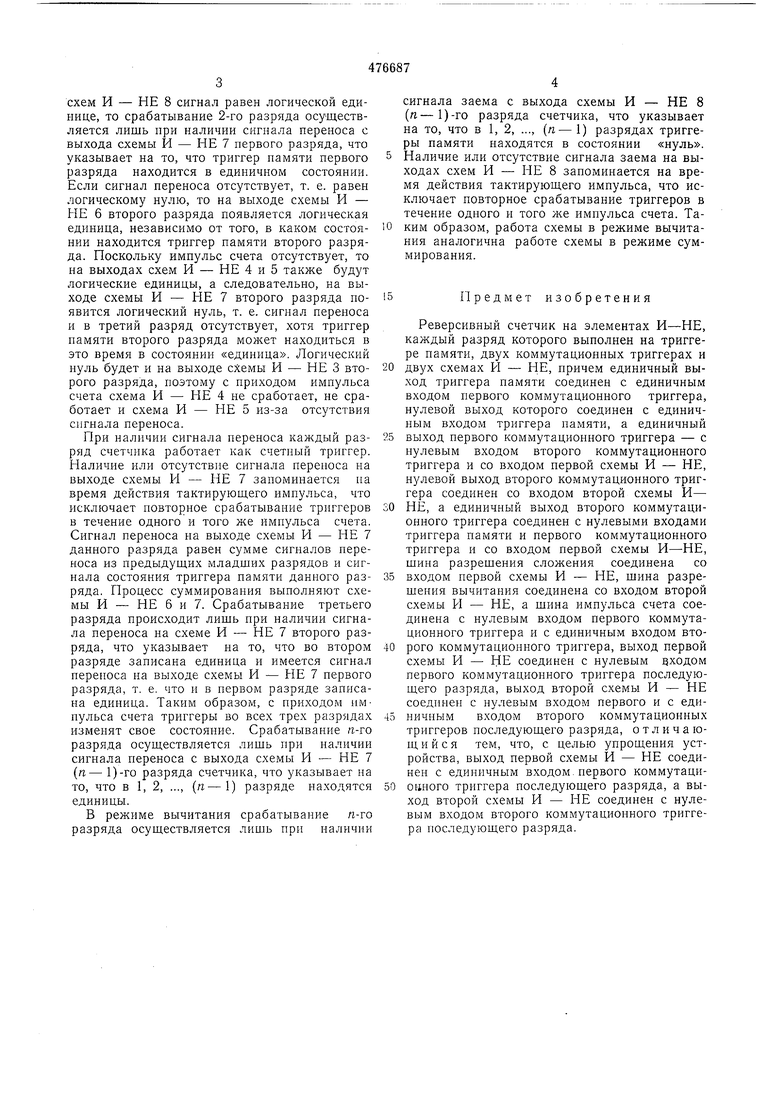

На чертеже показана схема предложенного реверсивного счетчика. Схемы И - НЕ 1 и 2 образуют триггер

памяти, схемы И - НЕ 3 i 4 - второй коммутационный триггер, а схемы И - НЕ 5 и G - первый коммутационный триггер, схемы И - НЕ 7 и 8 выполняют свойственные им логические функции.

В рел-симе суммирования на входы схем И - НЕ 7 подаются сигналы, равные логической единице, а на входы схем И - НЕ 8- сигналы, равные логическому нулю. Первый разряд счетчика работает как обычный триггер со счетным входом. Поскольку на выходах

схем И - НЕ 8 сигнал равен логической единице, то срабатывание 2-го разряда осуществляется лишь нри наличии сигнала переноса с выхода схемы И - НЕ 7 первого разряда, что указывает на то, что триггер памяти первого разряда находится в единичном состоянии. Если сигнал переноса отсутствует, т. е. равен логическому нулю, то на выходе схемы И - НЕ 6 второго разряда появляется логическая единица, независимо от того, в каком состоянии находится триггер памяти второго разряда. Поскольку импульс счета отсутствует, то на выходах схем И - НЕ 4 и 5 также будут логические единицы, а следовательно, на выходе схемы И - НЕ 7 второго разряда появится логический нуль, т. е. сигнал переноса и в третий разряд отсутствует, хотя триггер памяти второго разряда может находиться в это время в состоянии «единица. Логический пуль будет и на выходе схемы И - НЕ 3 второго разряда, поэтому с приходом импульса счета схема И - НЕ 4 не сработает, не сработает и схема И - НЕ 5 из-за отсутствия сигнала переноса.

При наличии сигнала переноса каждый разряд счетчика работает как счетный триггер. Наличие или отсутствие сигнала переноса на выходе схемы Н - НЕ 7 запоминается па время действия тактирующего импульса, что исключает повторное срабатывание триггеров в течение одного и того же импульса счета. Сигнал переноса на выходе схемы Н - НЕ 7 данного разряда равен сумме сигналов переноса из предыдущих младших разрядов и сигпала состояния триггера памяти данного разряда. Процесс суммирования выполняют схемы И - НЕ 6 и 7. Срабатывание третьего разряда происходит лишь при наличии сигнала переноса на схеме И - НЕ 7 второго разряда, что указывает на то, что во втором разряде записана единица и имеется сигнал переноса на выходе схемы И - НЕ 7 первого разряда, т. е. что и в первом разряде записана единица. Таким образом, с приходом импульса счета триггеры во всех трех разрядах изменят свое состояние. Срабатывание п-го разряда осуществляется лишь при наличии сигнала переноса с выхода схемы И - НЕ 7 (п- 1)-го разряда счетчика, что указывает па то, что в 1, 2, ..., (п-1) разряде находятся единицы.

В режиме вычитания срабатывание п-го разряда осушествляется лишь при наличии

сигнала заема с выхода схемы И - НЕ 8 (п-1)-го разряда счетчика, что указывает на то, что в 1, 2, ..., (я-1) разрядах триггеры памяти находятся в состоянии «нуль.

Наличие или отсутствие сигнала заема на выходах схем И - НЕ 8 запоминается на время действия тактирующего импульса, что исключает повторное срабатывание триггеров в течение одного и того же импульса счета. ТаКИМ образом, работа схемы в режиме вычитания аналогична работе схемы в режиме суммирования.

Предмет изобретения

Реверсивный счетчик на элементах И-НЕ, каждый разряд которого выполнен на триггере памяти, двух коммутационных триггерах и

двух схемах И - НЕ, причем единичный выход триггера памяти соединен с единичным входом первого коммутационного триггера, нулевой выход которого соединен с единичным входом триггера памяти, а единичный

выход первого коммутационного триггера - с нулевым входом второго коммутационного триггера и со входом первой схемы И - НЕ, нулевой выход второго коммутационного триггера соединен со входом второй схемы И-

НЕ, а единичный выход второго коммутационного триггера соединен с нулевыми входами триггера памяти и первого коммутационного триггера и со входом первой схемы И-НЕ, шипа разрешения сложения соединена со

входом первой схемы И - НЕ, шипа разрешения вычитания соединена со входом второй схемы И - НЕ, а шина импульса счета соединена с нулевым входом первого коммутационного триггера и с единичным входом второго коммутационного триггера, выход первой схемы И - НЕ соединен с нулевым входом первого коммутационного триггера последующего разряда, выход второй схемы И - НЕ соединен с пулевым входом первого и с едипичным входом второго коммутационных триггеров последующего разряда, отличающ и и с я тем, что, с целью упрощения устройства, выход первой схемы И - НЕ соединен с единичным входом, первого коммутацп01ШОГО триггера последующего разряда, а выход второй схемы И - НЕ соединен с нулевым входом второго коммутационного триггера последующего разряда.

3 разря

2 ОУЗР.Ч

позг.ад

а-,реше/ 1/е Sbwumcf i/fl

| название | год | авторы | номер документа |

|---|---|---|---|

| Реверсивный счетчик | 1980 |

|

SU879780A2 |

| Устройство для преобразования кодов | 1977 |

|

SU744544A1 |

| Реверсивный счетчик с последовательным переносом | 1974 |

|

SU516196A1 |

| Реверсивный счетчик | 1973 |

|

SU458100A1 |

| Реверсивный счетчик | 1981 |

|

SU1003356A1 |

| Параллельный накапливающий сумматор | 1987 |

|

SU1587496A1 |

| Оптоэлектронный десятичный сумматор | 1978 |

|

SU840895A1 |

| Реверсивный счетчик | 1985 |

|

SU1257839A1 |

| Устройство для сложения длительностей импульсов | 1986 |

|

SU1332337A1 |

| Устройство для измерения мгновенного хода часов | 1985 |

|

SU1365044A1 |

Авторы

Даты

1975-07-05—Публикация

1973-07-20—Подача