(54) УСТРОЙСТВО ДЛЯ ПРЕОБРАЧрВАНИЯ КОДОВ

1

Изобретение относится к автоматике и цифровой вычислительной технике и может быть использовано при построении преобразователей из двоичного кода в двоично-десятичныйи для об- 5 ратного преобразования.

Известно устройство для преобразования двоичного кода в двоично-десятичный, содержащее регистр двоичного кода, шифратор, группу двоичных счет-10 чиков, сдвиговый регистр и двоичнодесятичный счетчик, разбитый на тетрады 1 .

Недостатком известного устройства является относительно большая слрж- 5 ность и невозможность обратного преобразования.

Наиболее близким техническим решением данной задачи является устройство для преобразования кодов, 20 содержащее сдвиговый регистр, группу элементов И, первые входы которых соединены с выходами сдвигового регистра, регистр двоичного кода, шифратор двоично-десятичнЬ1х эквивален- 25 тов, первые входы которого соединены с выходами сдвигового регистра, а вторые входы - с вйходами регистра двоичного кода, разрядные входы установки нуля которого соединены с зо

выходами элементов И группы, счетчик, тетрады элементов И, перйые входы KOToV feix соедйнёнь с соответствующими выходами шифратора двоично-десятичных эквивалентов, вторые входы элементов И тетрад соединены с соответствующими выходами счетчика, реверсивный двоично-десятичный счетчик, элементы ИЛИ, вход первой группы каждого из которых соединен с выходом соответствующей тетрады-элементов И, а выходы подключены ко входам соответствующих тетрад реверсивного двоично-десятичного счетчика, выход каждой тетрадам которого через элемент задержки соединен со , ВТОРЫМ: входом элемента ИЛИ послеДую-щей тетрады 2,

Цель изобретения - упрощение устройства и повьпиение его быстродействия.

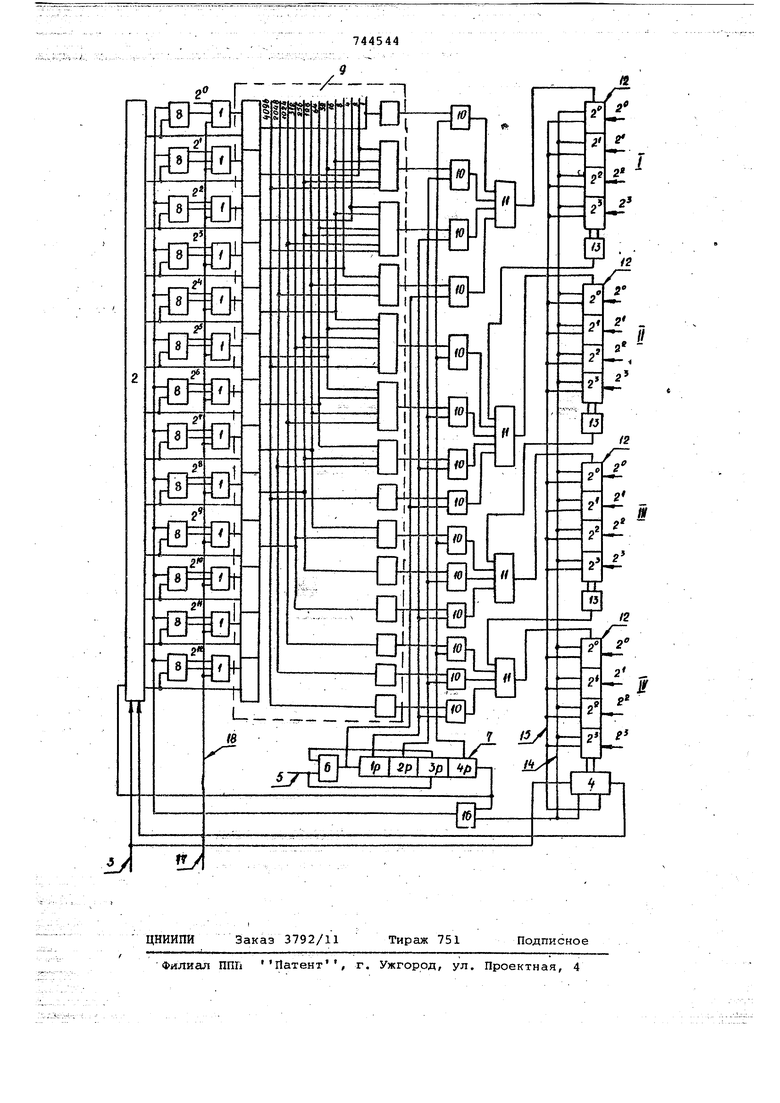

Указанная цель достигается тем, что устройство содержит триггер и дополнительный элемент И, первый вход которого соединен с выходом переполнения счетчика и спервым входом сдвигового регистра, второй вход - с единичным выходом триггера и со входом сложения реверсивного двоично-десятичного счетчика, а выход со вторыми входами элементов И перво группы, нулевой выхдд триггера соеди нен со входом вычитания реверсивного двоично-десятичного счетчика, нулевой и единичный управляющие входы триггера соединены с выходами заём и перенос реверсивного двоично-десятичного счетчика, единичный установочный вход триггера соединен со входом установкиединиц регистра двоичного кодаи со вторым входом сдвигового регистра, а нулевой установочный вход - с третьим входом сдвигового регистра. На чертеже; представлена схема устройства для преобразования кодов Устройство содержит регистр 1 двоичного кода, сдвиговый регистр 2 вход 3. для сигнала Пуск-1, триггер 4, вход 5 для тактовых импульсо .ТИ , элемент б И счетчика, счетчик 7, группу элементов 8 И, шифратор 9 двоично-десятичных эквивалентов, тетрады элементов 10 И, элементы 11 ИЛИ, двоично-десятичный реверсивный счетчик 12, элементы 13 задержки, шину 14 сложения, шину 15 вычитания, элемент 16 И, вход 17 для сигнала Пуск-2, шину 18 установки в 1 . Преобразование двоичного кода в двоично-десятичный начинается с приходом импульсного сигнала Пуск-1 на вход 3 устройства преобразования Перед этим в регистр 1 двоичного кода должно быть исходное двоичное число. Импульсный сигнал Пуск-1 записывает в крайний разряд сдвигового регистра 2 и одновременно через нулевой установоч ный вход триггера 4 устанавливает последний в состояние Преобразование каждого разряда двоичного кодаосуществляется за 9 импульсов тактовой частоты ти поступающей через вход 5 устройствЪ преобразования на вход элемента 6 И счетчика и на вход третьего разряда счетчика 7. Каждый десятый импульс тактовой частоты ТИ с выхода сче чика 7 (сигнал Сдвиг) поступает на вход сдвигового регистра 2, элемент 16 И и осуществляет сдвиг записанной в сдвиговом регистре 2. Сдвиговый регистр 2 последовательно формирует сигналы опроса, которые опргиаивают, начиная со старшего разряда, разряды регистра 1 двоичного кода. Выходы шифратора двоично-десятичных эквивалентов подключены ко входам тетрад , элементов 10 И. Веса тетрад сЬответствуют весам декад двоично-десятичного счетчика 12, соответственно, единиц I, десятков II сотен III, тысяч IV и т.д. . . Шифратор 9 двоично-десятичных эквивалентов представляет опрашиваемый разряд регистра 1 двоичного кода эквивалентным ему двоично-десятичным кодом, который поступает параллельно на первые входы тетрад элементов 10 И, на вторые входы которых поступают серии импульсов 8-4-2-1, форм:1руемые на выходе элемента б И и, соответственно, выхоах первого, второго и четвертого разрядов счетчика 7 за цикл работы в десять тактовых импульсов. Элементы 10 И тетрад преобразуют потетрадно двоично-десятичный код в параллельные унитарные (число-импульсные) коды этих тетрад, которые элементами 11 ИЛИ совместно с сигналами переносов, поступающими с выходов элементов 13 задержки, преобразуются в полные последовательные коды этих тетрад, поступающие на входы реверсивного двоично-десятичного счетчика 12, единиц I, десятков II, сотен III, тысяч IV и т.д. Так как триггер 4 находится в состоянии О , то со своего логического выхода О он выдает потенциальньгй сигнал с уровнем , который поступает на шину 14 сложения и тем самым разрешает работу ревер- сивного двоично-десятичного счетчика 12 в прямом счете, то есть суммирование импульсов, поступающих на. его входы. В то же время с логического выхода 1 триггера 4 на шину 15 вычитания поступает потенциальный уровень и тем самым запрещает работу двоично-десятичного счетчика 12 на вычитание. Таким образом при последовательном опросе разрядов регистра 1 двоичного кода происходит накопление двоичных эквивалентов в двоично-десятичном счетчике 12 единиц I, десятков II, сотен III, тысяч IV и т.д. Процесс преобразования исходного двоичного числа оканчивается опросом всех разрядов регистра 1 двоичного кода, причем в этом регистре остается нулевая комбинация двоичного кода (исходная информация сотрется), так как сигналы с выхода счетчика 7 через элемент 16 И, на первом входе которого, соединенном с нулевым выходом триггера 4, находится потенциал с уровнем , и далее через элементы 8 И группы устанавливают опрашиваег оле разряды ретистра 1 двоичного кода в состояние О . При обратном преобразовании двоично-десятичного кода в двоичный исходная двоично-десятичная информация помещается в соответствующие разряды реверсивного двоично-десятичного счётчика 12, единиц I, десятков II, сотен III, тысяч IV и т.д. Преобразование начинается с приходом импульсного сигнала Пуск-2 на вход 17 устройства; Этот сигнал записывает i в крайний разряд сдвигового регистра 2, а также через шину 18 устанавливает каждый разряд регистра 1 двоичного кода в состояние 1 и одновременно через единичный установочный вход триггера 4 устанавливает последний в состояние . Опрос разрядов регистра 1 двоичного кода, а также их весовое представление шифратором двоично-десятичных эквивалентов тетрадами элементов 10 И, элементами 11 ИЛИ происходит также, как и при преобразовании двоичного кода в двоичнодесятичный. Но здесь первоначально происходит вычитание импульсов, поступающих с выходов элементов 11 ИЛИ на входы двоично-десятичного счетчика 12 единиц I, десятков II, сотен III, тысяч IV и т.д. Первоначально вычитание происходит вследствие т,ого, что по сигналу Пуск-2 триггер 4 переведен в со стояние , и поэтому с его нул вых и единичных выходов поступают сигналы соответственно с уровнем О на шину.14 сложения (запрещает сложение) и с уровнем i на шину 15 вычитания (разрешает вычита ние) Таким образом, состояние О триггера 4 соответствует сложению. а его состояние 1 соответствует вычитанию импульсов, поступающих на вход реверсивного двоично-десятичного счетчика 12, При преобразовании двоично-десятичного кода в двоичный триггер 4 может также управляться (в отличие от преобразователя двоичного кода в двоично-десятичный, где он должен постоянно находиться в состо нии О), поступающими на его пер ключательные входы импульсами переноса. - При реверсивной работе счетчика 12 возникают два типа сигналов: при сложении - переносы, при вычитании сигналы заема, которые соответствен поступают на первые и вторые входы элементов 13 задержки и далее через элементы 11 ИЛИ на входы двоичнодесятичного счетчика 12, за исключе нием переносов, формируемых на выхо де старшей декады двоично-десятичного счетчика 12 (тысяч IV). Сигнал переноса старшей декады двоично-дес тичного счетчика 12 (тысяч IV) пост пает на единичный переключательный вход триггера 4 и тем cajvCjM переводит его в состояние , а сигн заема поступает на нулевой переключ тельный вход триггера 4 и тем самым переводит е.го в состояние О. Рассмотрим работу триггера 4 при преоб 1азо;вании двоично-десятичного кода в -двоичный (исходное состояние 1). Очевидно, если весовое значение опреиаиваемого разряда регистра 1 двоичного кода меньше исходного двоично-десятичного числа или очередного его остатка, то сигналов заема нет и триггер 4 находится в состоянии (режим вычитания). При этом на первом входе элемента 16 И находится нулевой.потенциал и поэтому сигналы с выхода счетчика7 не проходят на выход элемента 16 И, и тем самым опршииваеьий разряд регистра 1 двоичного кода остается в состоянии . Однако, если весовое значение опрашиваемого разряда регистра 1 двоичного кода больше исходного двоичнодесятичного числа или его очередного остатка, то на выходе старшей декады счетчика 12 (тысяч IV) появляется сигнал заема, который переводит триггер 4 в состояние О. При этом реверсивный двоично-десятичный счетчик 12 переводится в режим сложения, а опрашиваемый разряд регистра 1 двоичного кода сигналом, поступившим с выхода счетчика 7, через элемент 16 И, первый вход которого находится теперь в единичном состоянии, и далее через элементы И 8 группы, на первый вход которой поступает сигнал разрешения с соответствующего разряда регистра 2,устанавливается в состояние О. Информация на выходе триггера обновляется через, период работы счетчика 7, первый и второй выходы которого являются : парафазными, Реверсивный двоично-десятичный счетчик 12 производит сложение эквивалентов опрашиваемых разрядов регистра 1 двоичного кода до тех пор, пока на выходе старшей декады счетчика 12 не возникнет сигнал переполнения, которым триггер 4 переводится в единичное состояние. Причем предыдущие (до сигнала переполнения) опрашиваемые разряды регистра 1 двоичного кода устанавливаются в состояние О сигналами, поступающими с выхода счетчика 7 через элемент 16 И и элементы 8 И группы. Пример преобразования двоичнодесятичного кода 0111.0011.0110.0101 в двоичный приведен в таблице.

n 12 4096 1. -7365

409б

n 11 2048 1. 3269

2048

n 10 1024 1.

1024

n 9 -512 lo 0197

12

256 0. 9685

n 256

n 7 128 p. 9941

128 ,

n 6 64 1. 0069

64

i, 0005 П p и M e ч a H и Процесс преобразования двоичнодесятичного кода в двоичный заканчи вается опросом .всех разрядов регистра 1 двоичного кода. При этом в регистре 1 двоичного кода находится эквивалентный исходному двоично-десятичному коду 0111.0011.0110.0101 двоичный код 1110011000101. Элементы 13 задержки предотвращают совпадение импульсов унитарного кода с импульсами переносов. Предложенная конструкция позволя исключить из устройства элемент ИЛИ регистр числа с входящими в негр элементами разрешения записи, элементы разрешения перезаписи реверси ных декадных счетчиков, упростить схему управления, что значительно упрощает и повышает надежность устройства преобразования кодов. Формула изобретения Устройство для преобразования ко дов, содержащее сдвиговый регйстр, группу элементов И, первые входы ко торых соединены с выходами сдвигово

n 5

1. 0005 32

32

n 4

0. .9973 16

16

0. 8

1 n 3

1 n 2

1. 0001 2

0 n 1

0.9999

0 n 0

1. 0000 e.B таблице двоично-десятичный код представлен егоэквивалентными значениями в десятичной системе; цифра О или 1 пеоед точкой отмечает состояние 1 триггера 4. го регистра, регистр двоичного кода, шифратор двоично-десятичных эквивалентов, первые входы которого со- единены с выходами сдвигового регистра, а вторые входы - с выходами регистра двоичного кода, разрядные входы установки нуля которого соединены с выходами элементов И группы, счетчик, тетрады элементов И, первые входы которых соединены с . соответствующими выходами шифратора двоично-десятичных эквивалентов, вторые входы элементов И тетрад соединены с соответствующими выходами счетчика, реверсивный двоично-десятичный счетчик, элементы ИЛИ, вход первой группы каждого из которых соединен с выходом соответствующей тетрады элементов И, а выходы подключены ко входам соответствук)щих тетрад реверсивного двоично-десятичного счетчика, выход каждой тетрады которого через элемент задержки соединен со вторым входом элемента ИЛИ последующей тетрады, о т л и ч а к щ е ес я тем, что, с целью упрощения устройства и повышения его быстродействия , он содержит триггер и дополнительный элемент И, первый вход кото рого соединен с выходом переполнения счетчика и с первьм входом сдвигового регистра, второй вход - с единичным выходом триггера и с входом сложения реверсивного двоично-десятичного счетчика, а выход со вторыми входами элементов И первой группы, нулевой выход триггера соединен с входом вычитания реверсивного двоично-десятичного счетчика, нулевой и единичный управляющие входы триггера соединены с выходами заем и перенос реверсивного двоично-десятичного счетчика, единичный установочный вход триггера соединен с входом установки единиц регистра двоичного кода и со. рторым входом сдвигового регистра, а нулевой установочный вход - с третьим входом сдвигового регистра. Источники информации, принятые во внимание при экспертизе 1; Авторское свидетельство СССР 525944, кл.С 06 Р 5/02, 1974. 2. Авторское свидетельство СССР по заявке 2443060/18-24, кл. G 06 F 5/02, 10.01,77.

- /.

л

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для преобразования двоичного кода в двоично-десятичный | 1977 |

|

SU898417A2 |

| Реверсивный преобразователь двоичного кода в двоично-десятичный | 1974 |

|

SU620975A1 |

| Реверсивный десятичный счетчик | 1979 |

|

SU822381A1 |

| Преобразователь двоичного кода в двоично-десятичный и обратно | 1975 |

|

SU708344A1 |

| Преобразователь двоично-десятичных чисел в двоичные | 1982 |

|

SU1048469A1 |

| Устройство для преобразования двоичного кода в двоично-десятичный | 1976 |

|

SU641441A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1977 |

|

SU691843A1 |

| Преобразователь двоичного кода в двоично-десятичный масштабированный код | 1978 |

|

SU767750A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1983 |

|

SU1130858A1 |

| Преобразователь двоичных кодов в двоично-десятичные | 1984 |

|

SU1200428A1 |

Авторы

Даты

1980-06-30—Публикация

1977-03-29—Подача