Изобретение относится к импульс- ной технике и может быть использовано для построения синтезаторов час- тот средств связи, а также для генераторного оборудования многоканальных систем передачи.

Цель изобретения - повышение надежности работы за счет уменьшения времени вхождения в синхронизм путем автоматического перехода в режим поиска при нарушении синхронизма.

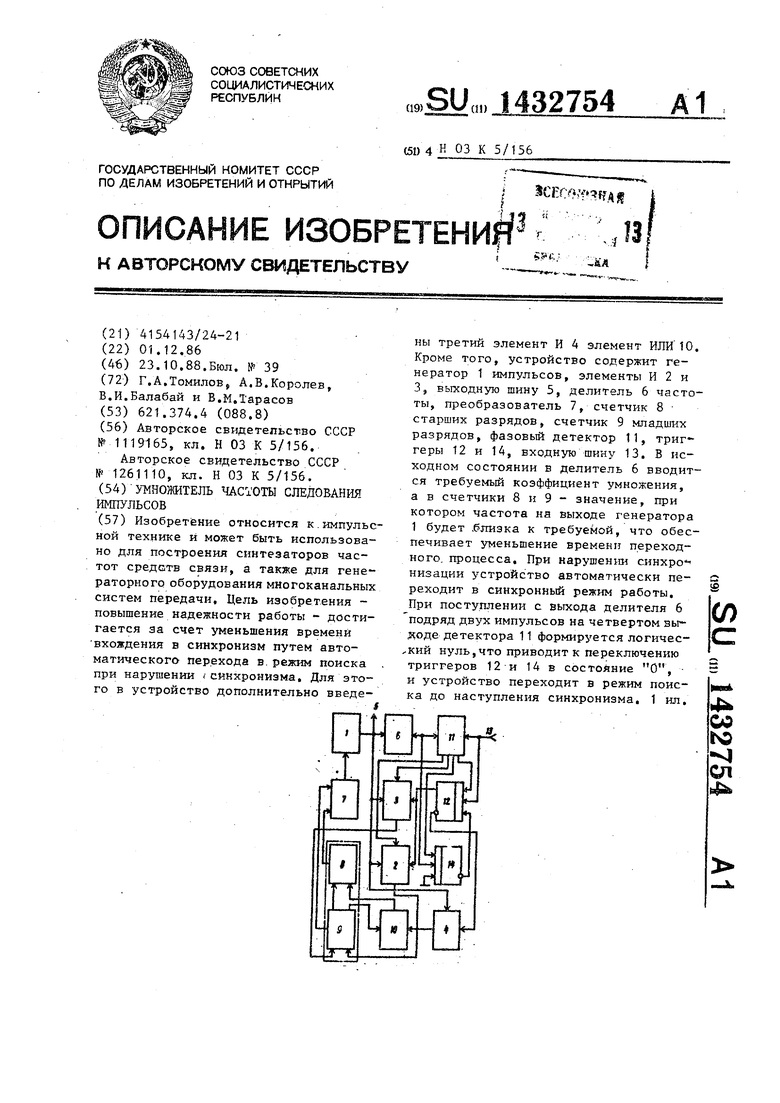

На чертеже приведена электрическая структурная схема умножителя частоты следования импульсов.

Умножитель частоты содержит генератор 1 импульсов, выход которого соединен с первыми входами первого 2, второго 3 и третьего 4 элементов И, с выходной шиной 5 и входом делителя 6 частоты. Вход генератора 1 импульсов соединен с выходом преобразователя 7 кода в напряжение, входы которого соединены с соответствующими вьгходами реверсивного счетчика импульсов, состоящего из счетчика 8 старших разрядов и счетчика 9 младших разрядов. Вход вычитания счетчика 8 младших разрядов соединен непосредственно с выходом заема счетчика. 9 младших.разрядов, а вход суммирования через элемент ИЛИ 10 с выходом переноса счет чика 9 младших разрядов. Входы суммирования и вычитания счетчика 9 млад- ших разрядов реверсивного счетчика импульсов соединены с выходами соответственно первого 2 и второго 3 элементов Hj, вторые входы которых соединены соответственно с первыми и вто- рыми выходами фазового детектора 11. Тактовьй вход первого триггера 12 соединен с входной шиной 13 и первым входом фазового детектора 11, третий выход которого соединен с информа- ционным входом первого триггера 12. Тактовый вход второго триггера 14 соединен с выходом делителя 6 частоты и вторым входом фазового детектора 1 1 , четвертый выход которого соединен с информационным входом второг триггера 14, вход сброса которого соединен с общей шиной, инверсньш. выход - с входом сброса первого триггера 12. Третьи входы первого 2 и . вторцго 3 элементов И соединены с прямым выходом первого триггера 12, инверсный выход которого соединен с вторым входом третьего элемента И 4,

Q

j

0 О Q

0

выход которого соединен с вторым входом элемента ИЛИ 10.

Фазовый детектор содержит первый и второй триггеры, прямой и инверсный выходы первого из которых соединены с первыми входами соответственно первого и второго элементов И, выходы второго - с вторыми их входами, выход второго элемента И соединен с первым входом третьего элемента И, второй вход и выход которого соединены соответственно с выходом и первым входом четвертого элемента И, второй вход которого соединен с выходом первого элемента И,выход - с R-входами первого и второго триггеров, информационные входы которых соединены с шиной логической 1, тактовые входы - соответственно с вторым и первым входами фазового детектора, инверсные выходы - соответственно с первым и вторым его выходами, а прямые выходы - соответственно с третьим и четвертым выходами фазового детектора.

Умножитель работает следующим об- зом.

В исходном состоянии в делитель 6 вводится требуемьй, коэфициет умножения, а в счетчики 8 и 9 - значение, при котором частота на выходе генератора 1 близка к требуемой.Последнее обеспечивает уменьшение времени переходного процесса, но не является обязательным.

Рассмотрим работу устройства в синхронном режиме, т.е. когда импульсы на входы детектора 11 поступают поочередно и сдвиг фаз между ними не превышает 360 , При этом условии на третьем и четвертом выходах детектора 11 формируется логическая 1. Пусть на втором входе детектора 11 появг ляется импульс с выхода делителя 6, тогда на втором выходе детектора 11 появляется импульс,длительность которого определяется временем запаздывания импульса на шине 13. Таким образом, триггреры 12 и 14 на прямых выходах формируют логическую 1, что обеспечивает прохождение импульсов с выхода генератора 1 через элемент И 3 на вход вычитания счетчика 9 (а затем и счетчике 8), Сигналы с выходов счетчиков 8 и 9 поступают на входы преобразователя- 7, его выходное напряжение у -5еньшается, что приводит к уменьшению частоты сЛедованпя импульсов на выходе генератора I и шине 5, Следующий импульс с выхода делителя 6 появляется позже, чем в предыдущем случае, что приводит к уменьшению разности фаз сравниваемых частот. Этот процесс продолжается до тех пор, пока разность фаз сравниваемых частот не станет равна нулю.

Если импульс на шине 13 появляется раньше, чем импульс на выходе делителя 6, детектор 11 формирует им- пульс на своем первом выходе, дли™ тельность которого определяется временем запаздывания импульса, поступающего с выхода делителя 6. Триггеры 12 и 14 при синхронном режиме формируют на своих прямых выходах логическую) 1, что обеспечивает прохождение импульсов с выхода генератора 1 через элемент И 2 на вход сложения счетчика 9, при переполнении которого сигнал переноса чер.ез элемент ИЛИ 10 поступает на вход сложения счетчика 8. Сигналы с выходов счетчиков 8 и 9 поступают на входы преобразователя 7, его выходное напряжение увеличивается, что приводит к увеличению частоты следования импульсов на выходе генератора 1, Указанные циклы повторяются до тех пор, пока разность фаз сравниваемых частот не станет равна нулю,

При нарушении синхронизации, например на шину 13 поступает подряд - два импульса, на третьем выходе де- тектора 11 формируется логический О и триггер 12 переключается в состояние О, Тогда на третьих входах элементов И 2 и 3 будет логический

О и подсчет импульсов счетчиков 9 прекращается независимо от состояния первого и второго выходов детектора 11, При этом по является логическая 1 на втором входе элемента И 4,что обеспечивает прохождение импульсов с выхода генератора 1 на вход суммирования счетчика 8 через элемет ИЛИ 10, При достижении максимального значения кода на выходах счетчика 8 происходит его обнуление, за счет этого на выходе преобразователя 7 м формируется пилообразное напряжение, которое управляет частотой генератора 1, При определенном значении кода в счетчике 8 частота генератора 1 попадает, в полосу захвата кольца ФАПЧ, при этом импульсы на первый и второй

0

5

0

5

0

5

0

5

0

5

входы детектора 11 поступают поочередно; на его третьем выходе формируется логическая 1, что обеспечивает переключение триггера 12 в состояние 1. Устройство переходит в синхронный режим работы рассмотренный ранее).

При поступлении с выхода делителя 6 подряд двух импульсов на четвертом выходе детектора 11 формируется логический О, что приводит к переключению триггеров 12 и 14 в состояние О. Устройство переходит к режим поиска до наступления синхронизма, Формула изобретения

Умножитель частоты следования импульсов, содержащий генератор импульсов, выход которого соединен с входом делителя частоты и с первыми входами первого и второго элементов И, вторые входы которых подключены соответственно к первому и второму выходам фазового детектора, выходы соединены с входами соответственно суммирования и вычитания счетчика младщих разрядов реверсивного счетчика импульсов, вход вычитания старших разрядов которого соединен с выходом заема младших разрядов, ды - с соответствующими входами преобразователя кода в напряжения, выход которого соединен с входом генератора импульсов, выходную шину, входную шину, которая соединена с первым входом фазового детектора и с тактовым одом первого триггера, информационный вход которого соединен с третьим выходом фазового детектора, четвертый выход которого соединен с информационным входом второго триггера, инверсньш выход которого соединен с входом сброса первого триггера, вход сброса - с общей шиной, тактовый вход - с вторым входом фазового детектора и с выходом делителя частоты,о тличающий- с я тем, что, с цел1 :о повышения надежности работы за счет уменьшения времени вхождения в синхронизм, в него введены третий элемент И и элемент ИЛИ, первый вход и выход которого, соединены соответственно с выходом переноса младших разрядов и с вхо- дсм суммирования старших разрядов реверсивного счетчика имгтульсов, второй вход - с выходом третьего элемента И, первый вход которого сое5 .14327546

динен с выходом генератора импульсов прямой выход которого соединен с и с выходной шиной, второй вход - с третьими входами первого и второго инверсным выходом первого триггера, элементов И.

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой синтезатор частот | 1991 |

|

SU1803977A1 |

| Умножитель частоты следования импульсов | 1986 |

|

SU1403356A1 |

| УПРАВЛЯЕМЫЙ ГЕНЕРАТОР С ПРЕДУСТАНОВКОЙ ЧАСТОТЫ | 1997 |

|

RU2121749C1 |

| Устройство цифровой фазовой автоподстройки частоты | 1982 |

|

SU1125748A1 |

| Способ измерения рассогласования между углами поворота,один из которых задан кодом | 1985 |

|

SU1285595A1 |

| Умножитель частоты | 1990 |

|

SU1797113A1 |

| УСТРОЙСТВО ФАЗОВОЙ СИНХРОНИЗАЦИИ | 1997 |

|

RU2119717C1 |

| УСТРОЙСТВО СИНХРОНИЗАЦИИ | 2000 |

|

RU2167493C1 |

| Цифровой фазометр | 1982 |

|

SU1061062A1 |

| Устройство автоматической подстройки частоты | 1989 |

|

SU1698987A1 |

Изобретение относится к.импульсной технике и может быть использовано для построения синтезаторов частот средств связи, а также для генераторного оборудования многоканальных систем передачи. Цель изобретения - повышение надежности работы - достигается за счет уменьшения времени вхождения в синхронизм путем автоматического перехода в. режим поиска , при нарушении синхронизма. Для этого в устройство дополнительно введены третий элемент И 4 элемент ИЛИ 10. Кроме того, устройство содержит генератор 1 импульсов, элементы И 2 и 3, выходную шину 5, делитель 6 частоты, преобразователь 7, счетчик 8 старших разрядов, счетчик 9 младших разрядов, фазовьй детектор 11, триггеры 12 и 14, входную шину 13. В исходном состоянии в делитель 6 вводится требуемый коэффициент умножения, а в счетчики 8 и 9 - значение, при котором частота на выходе генератора 1 будет .близка к требуемой, что обеспечивает уменьшение времени переходного, процесса. При нарушении синхро- низации устройство автоматически переходит в синхронный режим работы. При поступлении с выхода делителя 6 подряд двух импульсов на четвертом вьг- доде детектора 11 формируется логичес кий нуль,что приводит к переключению триггеров 12 и 14 в состояние О, и устройство переходит в режим поиска до наступления синхронизма. 1 ил. 1C (Л 4ia Од ч (У1

| Умножитель частоты следования импульсов | 1983 |

|

SU1119165A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Умножитель частоты следования импульсов | 1984 |

|

SU1261110A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1988-10-23—Публикация

1986-12-01—Подача