(54) УСТРОЙСТВО ЗАЩИТЫ ОТ ПОМЕХ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство защиты от помех | 1979 |

|

SU879797A2 |

| Устройство защиты от помех | 1977 |

|

SU680188A1 |

| Устройство для выделения сигналов | 1981 |

|

SU966873A1 |

| Устройство для выделения сигнала | 1980 |

|

SU890548A2 |

| Устройство для выделения сигнала | 1979 |

|

SU813758A1 |

| Формирователь адреса | 1978 |

|

SU911502A1 |

| СПОСОБ ДЛЯ ЦИФРОВОЙ СУБСТРАКЦИОННОЙ АНГИОГРАФИИ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1992 |

|

RU2043073C1 |

| Устройство для регистрации ритма сердечной деятельности и характера его изменений | 1978 |

|

SU784867A1 |

| УПРАВЛЯЮЩИЙ АППАРАТНО-ПРОГРАММНЫЙ КОМПЛЕКС ДЛЯ ОБРАБОТКИ РАДИОЛОКАЦИОННОЙ ИНФОРМАЦИИ | 2001 |

|

RU2222028C2 |

| Устройство для контроля видеосигнала | 1982 |

|

SU1069190A1 |

I

Изобретение относится к радиотехйикеи может использоваться при защите от мех, в частности, при наличии периодических фоиовых помех оТ. источников питания

По основному авт. св. № 680188 известно устройство защиты от помех, содержащее последовательно соединенные преобразователь код-на1 ряжение и блок сравнения, а также блок управления и квантователь во времени, между выходом квантователя во времени, подключенного к выходу блока сравнения, и входом, преобразователя код-напряжение включены последовательно соединенные первый коммутатор, сумматор, оператив ный запоминакйцнй блок и второй комму-, татор, а между выходом блока управления и адресным входом оперативного запоминающего блока включены последовательно соединенные делитель частоты и формирователь адреса, причем входы управления преобразователя код-напряжение, второго коммутатора, сумматора и формирователя адреса подключеиь к соответствующим выходам .блока управления, при этом входом «Внешине константы являются вторые входы обо-, их коммутаторов и установочный вход делителя частрты, второй выход которого сое.динен с в-ходом считывания оперативного запоминающего блока, а третий - с управляющим входом первого коммутатора, при-: чем второй сумматор соединен с выходом второго коммутатора 1.

Однако известное устройство обладает низкой помехозащищенностью при наличии помех, начальная фаза которых изменяется, так как пороги, вычисляемые при развертке одинаковых участков двух соседних строк, будут существенно отличаться друг от друга, а это приведет к до олиительным погрец 10ностям при установке порога, а следовательно, и к снижению помехозащищенности.

Целью изобретения является повышение помехозащищенности. Для этого в устройстве защиты от помех, содержащем последовательно соединенные преобразователь

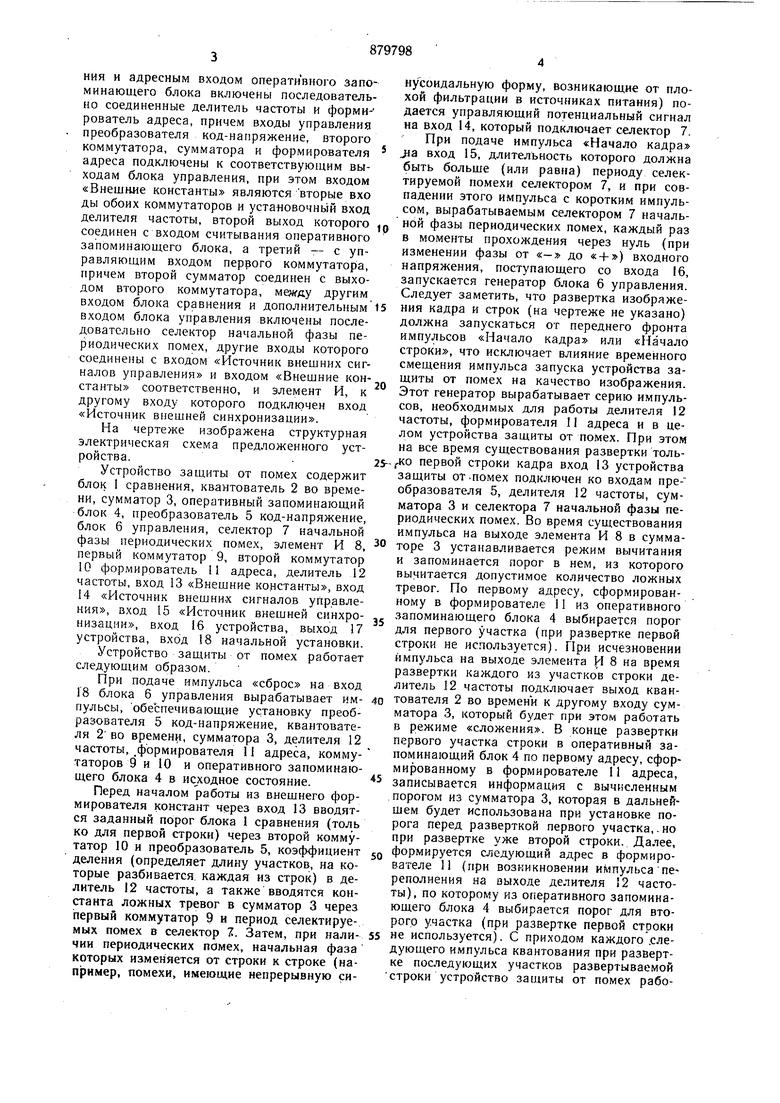

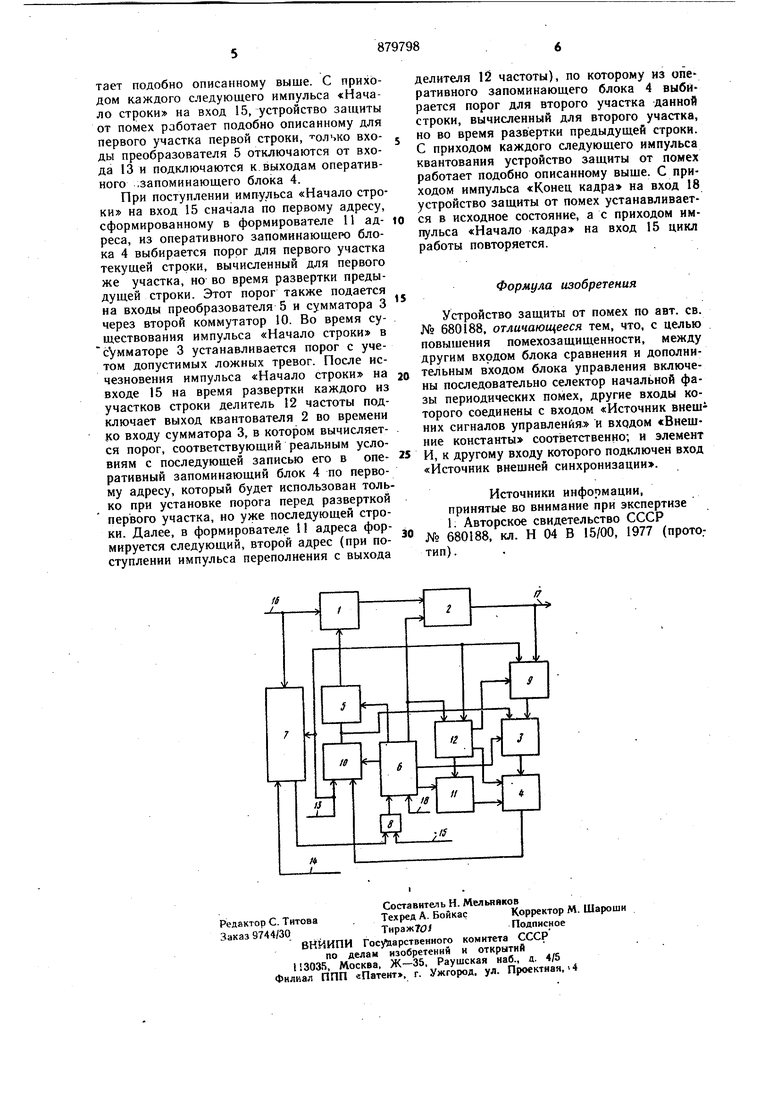

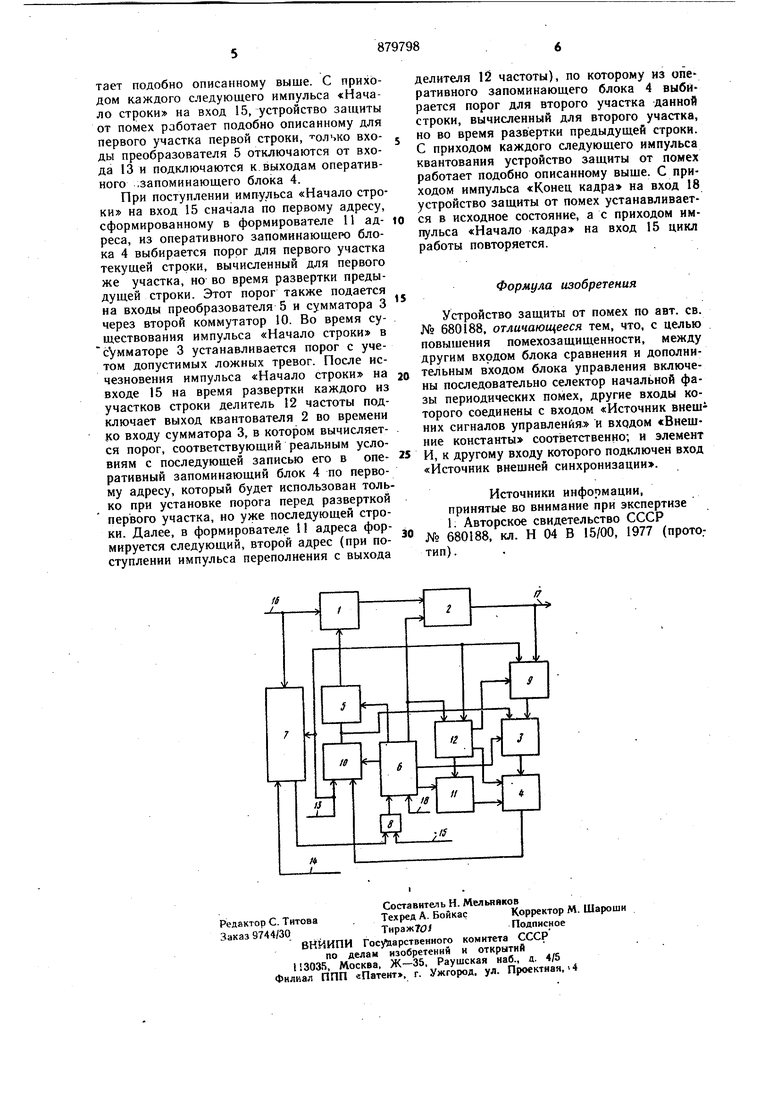

15 код-напряжение и блок сравнения, а также блок управления и квантователь во времени, между виходом квантователя во времени, подключенного к выходу блока сравнения, и входом преобразователя код-напряжение включены последовательно соединен20ные первый коммутатор, сумматор, оперативный запоминающий блок и второй коммутатор, а между выходом блока управле- НИИ и адресным входом оперативного запоминающего блока включены последовательно соединенные делитель частоты и формирователь адреса, причем входы управления преобразователя код-напряжение, второго коммутатора, сумматора и формирователя адреса подключены к соответствующим выходам блока управления, при этом входом «Внешние константы являются вторые вхо ды обоих коммутаторов и установочный вход делителя частоты, второй выход которого соединен с входом считывания оперативного запоминающего блока, а третий - с управляющим входом первого коммутатора, причем второй сумматор соединен с выходом второго коммутатора, между другим входом блока сравнения и дополнительным входом блока управления включены последовательно селектор начальной фазы периодических помех, другие входы которого соединены с входом «Источник внещних сигналов управления и входом «Внещние константы соответственно, и элемент И, к другому входу которого подключен вход «Источник внешней синхронизации. На чертеже изображена структурная электрическая схема предложенного устройства. Устройство защиты от помех содержит блок I сравнения, квантователь 2 во времени, сумматор 3, оперативный запоминающий блок 4, преобразователь 5 код-напряжение, блок 6 управления, селектор 7 начальной фазы периодических помех, элемент И 8, первый коммутатор 9, второй коммутатор 10 формирователь 11 адреса, делитель 12 частоты, вход 13 «Внешние константы, вход 14 «Источник внещних сигналов управления, вход 15 «Источник внещней синхронизации, вход 16 устройства, выход 17 устройства, вход 18 начальной установки. Устройство защиты от помех работает следующим образом. При подаче импульса «сброс на вход 18 блока 6 управления вырабатывает импульсы, обеспечивающие установку преобразователя 5 код-напряжение, квантователя 2 во времени, сумматора 3, делителя 12 частоты, формирователя 11 адреса, коммутаторов 9 и 10 и оперативного запоминающего блока 4 в несходное состояние. Перед началом работы из внещнего формирователя констант через вход 13 вводятся заданный порог блока 1 сравнения (толь ко для первой строки) через второй коммутатор 10 и преобразователь 5, коэффициент деления (определяет длину участков, на которые разбивается, каждая из строк) в делитель 12 частоты, а также вводятся константа ложных тревог в сумматор 3 через первый коммутатор 9 и период селектируемых помех в селектор Z. Затем, при наличии периодических помех, начальная фаза которых изменяется от строки к строке (например, помехи, имеющие непрерывную синусоидальную форму, возникающие от плохой фильтрации в источниках питания) подается управляющий потенциальный сигнал на вход 14, который подключает селектор 7. При подаче импульса «Начало кадра ia вход 15, длительность которого должна быть больше (или равна) периоду селектируемой помехи селектором 7, и при совпадении этого импульса с коротким импульсом, вырабатываемым селектором 7 начальной фазы периодических помех, каждый раз в моменты прохол дения через нуль (при изменении фазы от «- до « + ) входного напряжения, поступающего со входа 16, запускается генератор блока 6 управления. Следует заметить, что развертка изображения кадра и строк (на чертеже не указано) должна запускаться от переднего фронта импульсов «Начало кадра или «Начало строки, что исключает влияние временного смещения импульса запуска устройства защиты от помех на качество изображения. Этот генератор вырабатывает серию импульсов, необходимых для работы делителя 12 частоты, формирователя 11 адреса и в целом устройства защиты от помех. При этом на все время существования развертки тольKO первой строки кадра вход 13 устройства защиты от.помех подключен ко входам преобразователя 5, делителя 12 частоты, сумматора 3 и селектора 7 начальной фазы периодических помех. Во время существования импульса на выходе элемента И 8 в сумматоре 3 устанавливается режим вычитания и запоминается порог в нем, из которого вычитается допустимое количество ложных тревог. По первому адресу, сформированному в формирователе 11 из оперативного запоминающего блока 4 выбирается порог для первого участка (при развертке первой строки не используется). При исчезновении импульса на выходе элемента И 8 на время развертки каждого кз участков строки делитель 12 частоты подключает выход квантователя 2 во времени к другому входу сумматора 3, который будет при этом работать в режиме «сложения. В конце развертки первого участка строки в оперативный запоминающий блок 4 по первому адресу, сформированному в формирователе 11 адреса, записывается информация с вычисленным порогом из сумматора 3, которая в дальнейщем будет использована при установке порога перед разверткой первого участка,. но при развертке уже второй строки. Далее, формируется следующий адрес в формирователе 11 (при возникновении импульсапереполнения на выходе делителя 12 частоты), по которому из оперативного запоминающего блока 4 выбирается порог для второго участка (при развертке первой строки не используется). С приходом каждого .следующего импульса квантования при развертке последующих участков развертываемой строки устройство защиты от помех работает подобно описанному выше. С приходом каждого следующего импульса «Начало строки на вход 15, устройство защиты от помех работает подобно описанному для первого участка первой строки, - олько входы преобразователя 5 отключаются от входа 13 и подключаются к выходам оперативного .запоминающего блока 4. При поступлении импульса «Начало строки на вход 15 сначала по первому адресу, сформированному в формирователе 11 адреса, из оперативного запоминающего блока 4 выбирается порог для первого участка текущей строки, вычисленный для первого же участка, но во время развертки предыдущей строки. Этот порог также подается на входы преобразователя 5 и сумматора 3 через второй коммутатор 10. Во время су ществования импульса «Начало строки в сумматоре 3 устанавливается порог с учетом допустимых ложных тревог. После исчезновения импульса «Начало строки на входе 15 на время развертки каждого из участков строки делитель 12 частоты подключает выход квантователя 2 во времени ко входу сумматора 3, в котором вычисляется порог, соответствующий реальным условиям с последующей записью его в оперативный запоминающий блок 4 по первому адресу, который будет использован только при установке порога перед разверткой первого участка, но уже последующей строки. Далее, в формирователе 11 адреса формируется следующий, второй адрес (при поступлении импульса переполнения с выхода делителя 12 частоты), по которому из oneративного запоминающего блока 4 выбирается порог для второго участка данной строки, вычисленный для второго участка, но во время развертки предыдущей строки. С приходом каждого следующего импульса квантования устройство защиты от помех работает подобно описанному выще. С приходом импульса «Конец кадра на вход 18 устройство защиты от помех устанавливается в исходное состояние, а с приходом импульса «Начало кадра на вход 15 цикл работы повторяется. Формула изобретения Устройство защиты от помех по авт. св. N° 680188, отличающееся тем, что, с целью повышения помехозащищ,енности, между другим входом блока сравнения и дополнительным входом блока управления включены последовательно селектор начальной фазы периодических помех, другие входы которого соединены с входом «Источник внешних сигналов управления и входом «Внешние константы соответственно; и элемент И, к другому входу которого подключен вход «Источник внешней синхронизации. Источники информации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР № 680188, кл. И 04 В 15/00, 1977 (прото.

Авторы

Даты

1981-11-07—Публикация

1979-05-23—Подача