(54) УСТРОЙСТВО ПРИЕМА ФАЗОМАНИПУЛЙРОВАННЫХ ПСЕВДОС1БЧАЙНЫХ СИГНАЛОВ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство тактовой синхронизации псевдослучайных последовательностей | 1983 |

|

SU1092744A1 |

| УСТРОЙСТВО ПОИСКА И СЛЕЖЕНИЯ ЗА ШИРОКОПОЛОСНЫМ СИГНАЛОМ | 1983 |

|

SU1840276A1 |

| УСТРОЙСТВО ПОИСКА И СОПРОВОЖДЕНИЯ СИГНАЛА СИНХРОНИЗАЦИИ В СПУТНИКОВЫХ СИСТЕМАХ СВЯЗИ ПО ПРИЕМУ | 1995 |

|

RU2093964C1 |

| ПРИЕМОПЕРЕДАЮЩАЯ АППАРАТУРА ШИРОКОПОЛОСНЫХ ПСЕВДОСЛУЧАЙНЫХ СИГНАЛОВ | 1979 |

|

SU1840119A1 |

| УСТРОЙСТВО ПОИСКА ШУМОПОДОБНЫХ СИГНАЛОВ | 1985 |

|

SU1840080A1 |

| УСТРОЙСТВО ПЕРЕДАЧИ И ПРИЕМА ДЛЯ ШИРОКОПОЛОСНОЙ РАДИОСВЯЗИ | 1980 |

|

SU1840131A1 |

| МНОГОКАНАЛЬНЫЙ ПРИЕМОИНДИКАТОР СПУТНИКОВЫХ РАДИОНАВИГАЦИОННЫХ СИСТЕМ | 2001 |

|

RU2205417C2 |

| УСТРОЙСТВО ПОИСКА ШУМОПОДОБНОГО СИГНАЛА | 1985 |

|

SU1840167A1 |

| УСТРОЙСТВО ПОИСКА СИГНАЛА СИНХРОНИЗАЦИИ СПУТНИКОВОЙ СИСТЕМЫ СВЯЗИ | 1995 |

|

RU2093963C1 |

| Система связи с временным уплотнением шумоподобных сигналов | 1977 |

|

SU683029A1 |

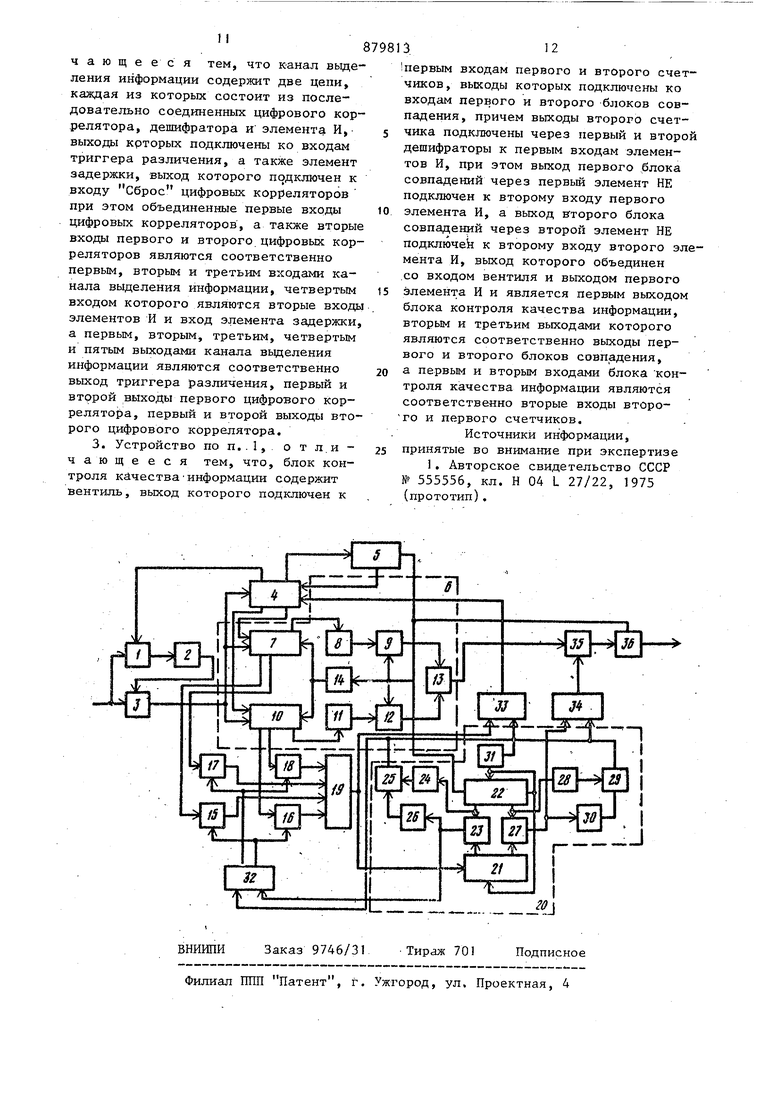

Изобретение относится к радиосйЯ зи и может использоваться для приема дискретной информации, передаваемой псевдослучайными сигналами с относительной фазовой манипуляцией. Известно устройство приема фазома нипулированных псевдослучайных сигналов, содержащее последовательно соединенные перемножитель, блок фазовой автоподстройки частоты и cHiix- ронный детектор, .выход которого подключен к первым входам канала тащцеления информации и блока слежения за задержкой, ко второму входу которого подключен первый выход синхронизатора, ко входу которого подключе первьй выход блока слежения за: задержкой, при этом второй вход синхронного детектора объединен с первым входом перемножителя, ко второму входу которого подключен второй выход блока слежения за задержской, тр тий и четвертый выходы которого .п,одключены ко второму .и третьему входа:м канала вьщеления информацииflj . Однако известное устройство обладает низкой помехоустойчивостью и не обеспечивает контроль качества принимаемой информации. Цель изобретения - повышение помехоустойчивости и обеспечение контроля качества принимаемой информации. Для отого в известное устройство приема.фазоманипулированных псевдослучайных сигналов , содержащее последовательно соединенные перемножитель, блок фазовой автоподстройки частоты и синхронный детектор, выход которого подключен к первым входам канала выделения информации и блока слежения за задержкой, ко второму входу которого подключен первый выход синхронизатора, ко входу которого подключен перый выход блока слежения за задержк.ой, при этом второй вход синхронного детектора объединен с первым входом перемножителя, ко вто .3 рому входу которого подключен второй выход блока слежения за задержкой третий и -четвертый выходы которого подключены ко второму и третьему входам канала вьщеления информации,введены четыре дешифратора, элемент ИЛИ, триггер переключения порогов, блок контроля качества информации, триггер поиска и последовательно соединенные триггер включения информации, элемент И и перекодирующий блок ко второму входу которого, а также к четвертому входу канала выделения информации и первому входу блока контроля качества информации подключен второй выход синхронизатора, а ко второму входу элемента И подключен первый выход канала выделения информации, второй, третий, четвертый и пятый выходы которого .подключены соответственно к первым входам перво го j второго, третьего и четвертого дешифраторов, выходы которых подключены ко входам элемента ИЛИ, а ко вторым входам первого и второго дешифраторов подключен первый выход триггера переключения порогов, второ выход которого подключен ко вторым входам третьего и четвертого дешифра торов, а к первым входам триггера подключения порогов, триггера поиска и триггера включения информации подключен первый выход блока контрол качества информации, второй и третий выходы которого подключены соответственно ко вторым входам триггера переключения порогов и триггера вклю чения информации, при этом выход эле мента ИЛИ подключен ко второму входу блока контроля качества информации И второму входу триггера поиска, выход .которого подключен к третьему входу блока слежения за задержкой, Канал выделения информации содержит две цепи, каждая из которых сост , ит из последовательно соединенных цифровых коррелятора, дешифратора и элемента И, выходы которых подключен Ко входам триггера различения, а также элемент задержки, выход которо го подключен к ) входу Сброс цифровых корреляторов, при этом объединенные первые входы хщфровых корреляторов, а также вторые входы первого и второго цифровых корреляторов являются соответственно, первым, вто рым и третьим входами канала вьщеления информации, четвертым входом которого являются вторые входы элемен4тов и и вход элемента задержки, а первым, вторым, третьим, четвертым и пятым выходами канала вьщеления информации являются соответствено выход триггера различения, первый и второй выходы первого цифрового коррелятора, перрый .и второй выходы второго цифрового коррелятора. Блок контроля качества информации содержит вентиль,выход которого подключен к первым входам первого и второго счетчиков, выходы которых подключены ко входам первого и второго блоков совпадения, причем выходы второго счетчика подключены через первый и второй дешифраторы к первым входам элементов И, при этом выход первого блока совпадений через первый элемент НЕ подключен к,второму входу первого элемента И, а выход второго блока совпадений через второй элемент-НЕ подключён ко второму входу второго элемента И, выход ко- торого объединен со входом вентиля и выходом первого элемента И и является первым выходом блока контроля качества информации, вторым и третьим выходами которого являются соответственно выходы первого и второ- го блоков совпадения, а первым и вторым входами блока контроля качества информации являются соответственно вторые входы второго и первого счетчиков. На чертеже представлена структурная электрическая схема устройства. Устройство содержит перемножитель 1, блок 2 фазовой автоподстройки частоты (ФАПЧ), синхронщ 1й детектор 3, блок 4 слежения за задержкой, синхронизатор 5, канал 6 выделения информации, содержащий две цепи: первая цепь содержит цифровой коррелятор .7, дешифратор 8, элемент И 9, вторая Цепь содержит цифровой коррелятор .10, дешифратор 11, элемент И 12 и триггер 13 различения, элемент задержки 14, первый дешифратор 15, второй дешифратор 16, третий дешифратор 17, четвертый дешифратор 18 элемент ИЛИ 19, блок 20 контроля качества-информахщи, содержащий первый счетчик 21, второй счетчик 22, первый блок 23 совпадений, первый дешифратор 24, первый элемент И 25, первый элемент НЕ 26, второй блок 27 совпадений, йторой дешифратор 28, второй элемент И 29, второй элемент НЕ 30, вентиль 31, триггер 32 переключения порогов. 5 триггер 33 поиска, триггер 34 включе ния информации, элемент И 35, перекодирующий блок 36. Устройство работает следуодим образом. В режиме синхронизации входной фазоманипулированный сигнал инверснымк псевдослучайными последовательностями, чередукнцимися по закону бинарной информации, поступает на вход устройства и в перемножителе 1 преобразуется в гармонический сигнал из-за перемножения с опорным бинарным псевдослучайным сигналом, поступакицим с выхода блока 4 слежения за задержкой, и фильтруется блоком 2 фазовой автоподстройки частоты. Этот же входной сигнал в синхронном детек торе 3 преобразуется в бинарную последовательность, так как на второй вход его поступает гармонический сигнал с выхода блока 2 ФАПЧ. Сигнал с выхода синхронного детектора 3 поступает на первый вход блока 4 слежения за задержкой и на первые входы перемножителей цифровых корреляторов 7 и 10 канала 6 вьщеления информации. Блок 4 слежения за завцержкой следит за временным положени ем сигнала, поступающего с выхода синхронного детектора 3, путем корре ляции его с двумя опорными инверсными псевдослучайными последовательностями. Канал 6 выделения информаци путем корреляции опорных последовательностей с принимаемыми осуществля ет вьщеление информационных импульсов , которые поступают на первый вход элемента И 35. Вьщелеиие информации осуществляется следующим образом. Последовательности с выхода синхронного детектора 3 поступают на пер вые входы перемножителей цифровых . корреляторов ,7 и 10, на вторые входы которых поступают опорные инверсные бинарные последовательности. Импульсы, образующиеся на выходах пере.множителей, накапливаются в суммирующих счетчиках цифровых корреляторов Если на входы цифровых корреляторов 7 и 10 поступает прямая псевдослучайная последовательность (ПСП) и на цифровой коррелятор 7 подается пряма опорная ПСП , а на цифровой коррелятор 10 подается инверсная опорная ПСП, то на счетчик цифрового коррелятора 7 за время информационной посьшки поступает большее число им13пульсов сигнала чем на счетчик цифрового коррелятора 10. При этом на выходе дешифратора 8 - появляется сигнал, который через элемент И 9 поступает:на один вход триггера 13 разли чения, на выходе которого появляется перепад напряжения, соответствукщий 1 импульсу инфбрмации. При поступлении на входы цифровых корреляторов 7 и 10 инверсной ПСП на счетчик цифрового коррелятора 10 поступает большее количество импульсов, чем на счетчик цифрового коррелятора 7. На выходе дешифратора 11 появляется сигнал, который через элемент И 12 поступает на другой вход триггера 13 различения, на выходе которого появляется перепад напряжения, соответствунщий О импульсу информации. Это происходит по окончании информационной посьтки на выходе синхронного детектора 3 при переходе на вторые входы элементов И 9 и 12 тактового импульса с синхронизатора 5. После задержки этого импульса в элементе задержки 14 им осуществляется сброс счетчиков цифровых корреляторов 7 и 10, подготавливая таким образом счетчики к приему следующей информационной посылки. Для вхождения в синхронизм блока 4 слежения за задегжкой необходимо произвести обнаружение сигнала. До обнаружения сигнала блок 4 слежения за задержкой осуп(ествляет сл&пой поиск. Обнаружение сигнала осуществляется следующим образом. Состояние счетчиков цифровых корреляторов 7 и 10 проверяется дешифраторами 15-18. которые выполняют роль пороговых устройств. Третий и четвертый дешифраторы 17 и 18 срабатывают на одно состояние счетчиков цифровых корреляторов 7 и 10, что соответствует превь шению сигналом первого порога (порог в данном случае задается местом -подключения третьего и четвертого дешифраторов 17 и 18 к выходам ячеек соответствуютщх счетчиков), а первый и второй дешифраторы 15 и 16 срабатывают на другое состояние счетчиков цифровых корреляторов 7 и 10, что соответствует превышению сигналом второго порога (порог в данном случае также задается местом подключения первого и второго дешифраторов 15 и 16 к выходам ячеек счетчиков) . В любой данный момент к счетчикам цифровых корреляторов 7 и 10 . /8 подключены соответственно дешифраторы 15, 16 или 17, 18 в зависимости от состояния триггера 32 переключения порогов, который управляется блоком 20контроля качества информации.. При срабатьгеании любого дешифратора 15, 16 или 17, 18 сигнал его вы хода поступает через элемецт ИЛИ 19на вход первого счетчика 21 и на оди вход триггера 33 поиска, в результате чего сигнал с выхода триггера 3 поиска подается -на третий вход блока 4 слежения за задержкой, по которому прекращается слепой поиск сигнала. Рассогласование входной ПСП и опорной ПСП находится в пределах длитель ности элементарного импульса ПСП. Более точное вхождение в синхронизм осуществляе;гся блоком 4 слежения за задержкой.. При поступлении следующей информа ционной посылки и срабатывания дешифраторов 15, 16 и 17, 18 на вход первого счетчика 21 поступает следующий импульс и т.д. Первый счетчик 21заполняется, его состояние характеризуется 11ислом импульсов, которые соответствуют ЧИСЛУ ср абатьгоаНИИ дешифраторов 15, 16 или 17, 18; т.е. характеризует качество принимаемой информации. На вход второго счетчика 22 поступают тактовые импульсы со второго выхода синхронизатора, заполняя его. При заполнении первого и второго счетчиков 21 и 22 наступят такие их состояния, когда первый блок 23совпадений сработает и сигнал с ее выхода поступает на другой вход триггера 32 переключения порогов и устанавливает его в положение, соответствующее подключению первого и второ го дешифраторов 15 и 16 к счетчикам цифровых корреляторов 7, 10, что соо ветствует установлению второго более высокого порога. Если первый блок 23 совпадений не сработает, а состояние второго счетчика 22 таково, что сработает первый дешифратор 24, то сигт нал с его выхода поступает на первый элемент И 25, -на второй вход которой поступает сигнал такой же полярности с выхода первого элемента НЕ 26, так как первый блок 23 совпадений не сра ботал. Сигнал с вь;рсода элемента И 23 подается на один вход триггера 32 переключения порогов, который под ключает третий и четвертый дешифраторы 17 и 18 к счетчику цифровых кор 8 реляторов 7 и 10, устанавливая таким образом более низкие пороги. Сигнал с выхода первого элемента И 25 поступает также на другой вход триггера 33 поиска, который изменяет свое состояние, и сигнал с его выхода поступает на третий вход блока 4 слежения за задержкой, приводя к поиску псевдослучайного сигнала этим блоком. Сигнал с выхода первого элемента И 25 проступает также через вентиль 31 в цепь Сброс - первого и второго счетчиков 2 и 22, приводя их в исходное состояние, и непосредственно на другой вход триггера 34 включения информации, сигнал с выхода которого закрывает элемент И 35, прекращая, таким образом, прохождение информации с выхода триггера 13 различия через элемент И 35 на вход перекодирующего блока 36 импульсов информации из относительной формы в абсолютную и на выход устройства. При срабатываНИИ первого блока 23 совпадений заполнение счетчиков 21 и 22 продолжается и наступает момент, когда второй блок 27 совпадений сработает. Тогда сигнал с ее выхода поступает на один вход триггера 34 включения информации, приводя его в такое состояние, при котором сигнал с его выхода открывает элемент И 35 по второму входу. При этом сигнал с выхода канала 6 выделения информации через элемент И 35 поступает на вход перекодирующего блока 36 и после перевГодировки - на выход устройства. На второй вход перекодирующего блока 36 поступают тактовые импульсы с частотой следования импульсов информации, необходимые для правильной работы перекодирующего блока. Если второй блок 27 совладений не срабатывает, а состояние второго счетчика 22 тактово, что.срабатывает второй дешифратор 28, то сигнал на его выходе и отсутствие сигнала на выходе второго блока 27 совпадений через элемент НЕ 30 приводят к срабатыванию второго элемента И 29, с выхода которого сигнал поступает на другой , вход триггера 34 включения информации, приводя к изменению состояния этого триггера, при котором элемент И 35 закрывается, прерывая путь прохождению Информации на выход устрой- ства. Кроме этого, сигнал с выхода второго элемента И 29 подается через вентиль 31 в цепь Сброс первого и второго счетчиков 21 и 22, приводя их в исходное состояние, на друг вход триггера 33 поиска, приводя к поиску сигнала блоком 4 слежения за задержкой, и на один вход триггера 32переключения порогов, приводя к подключению третьего и четвертого дешифраторов 17 и 18 соответственно к счетчикам : цифровых корреляторов 7 и 10. Таким образом, если качество информации не хзгже требуемого, то сна чала сработают первый блок 23 совпа дений, первый дешифратор 24, первый элемент И 25, первый элементНЕ 26 и первый и второй дешифраторы 15 и 16 подключаются к счетчикам цифровы корреляторов 7 и 10, устанавливая таким образом более высокий порог. Затем сработают второй блок 27 совпадений, второй дешифратор 28, втор элемент И 29, второй элемент НЕ 30 и выход устройства подключается чер перекодирую ций блок 36, элемент И 35 к выходу триггера 13 различения канала 6 выделения информации. Если качество информации хуже требу емого , то Первый и второй блоки 23 Э 27 совпадений, первый и второй де шифраторы 24 и 28, первый и второй элементы И 25 и 29, первый и второй элементы НЕ 26 и 30 подключают с помощью триггера 32 переключения по рогов первый и второй дешифраторы 15 и 16 к счетчикам цифровых корреляторов 7 и 10, сбрасывают первый и второй счетчики 21 и 22 через вен тиль 31, выдают с помощью триггера 33поиска команду на поиск сигнала в блок 4 слежения за задержкой и от ключают выход канала 6 выделения ин формации (выход триггера 13 различения) от выхода устройства с помо щью триггера 34 включения информации и элемента И 35. образом, устройство приема фазоманипулированных псевдослучайных сигналов обеспечивает пойьшге ние помехоустойчивости и контроль качества принимаемой информации. Формула изобретения 1. Устройство приема фазоманипули рованных псевдослучайных сигналов, содержащее последовательно соединен перемножитель, блок фазовой автопод стройки частоты и синхронный детект ВЫХОД которого подключен к первым входам канала вьщеления информации и блока слежения за задержкой, ко второму входу которого подключен первый выход синхронизатора, ко входу которого подключен первый выход синхронизатора, ко входу которого подключен первый выход ёлока слежения за задержкой, при этом второй вход синхронного детектора.объединен с первым входом перемножителя, ко второму входу которого подключен второй выход блока слежения за задержкой, третий и четвертый выходы которого подключены ко второму и третьему входам канала выделения информации, отличающеес я тем, что, с целью повышения помехоустойчивости и обеспечения контроля качества принимаемой информации, введены четыре дешифратора, элемент ИЛИ, триггер переключения порогов, блок контроля качества информации, триггер поиска и последовательно соединенные триггер включения информации, элемент И и перекодирующий блок, ко второму входу которого, а также к четвертому входу канала выделения информации и первому входу блока контроля качества информации подключен второй выход синхронизатора, а ко второму входу элемента- И подключен первый выход канала.выделения, информадии, второй, третий, четвертый, и пятый j выходы которого подключены соответственно к первым входам первого, второго,, третьего и четвертого дешифраторов, выходы которых подключены ко входам элемента ИЛИ, а ко вторым входам первого и второго дешифраторов подключен первый выход триггера переключения порогов, второй выход которого подключен ко вторым входам третьего и четвертого дешифраторов, а к первьм входам триггера переключения порогов, триггера поиска и триггера включения информации подключен первый выход блока контроля качества информации, второй и третий выходы которого подключены соответственно ко вторым входам триггера переключения порогов и триггера включения информации, при этом выход элемента ШШ подключен ко второму входу блока контроля качества информации и второму .входу триггера поиска, выход которого подключен к третьему входу блока слежения за задержкой, 2. Устройство по п. 1, о т л и чающееся тем, что к-анал выделения информации содержит две цепи, каждая из которых состоит из последовательно соединенных цифрового коррелятора, дешифратора и элемента И, выходы крторых подключены ко входам триггера различения, а также элемент задержки, выход которого подключен к входу Сброс цифровых корреляторов при этом объединенные первые входы цифровых корреляторов, а также вторые входы первого и второго цифровых корреляторов являются соответственно первым, вторым и третьим входами канала выделения информации, четвертым входом которого являются вторые входы элементов И и вход элемента задержки, а первым, вторым, третьим, четвертым и пятым выходами канала выделения информации являются соответственно выход триггера различения, первый и втррой выходы первого цифрового коррелято |а, первый и второй выходы второго цифрового коррелятора.

.первым входам первого и второго счетчиков, выходы которых подключены ко входам первого и второго блоков совпадения, причем выходы второго счетчика подключены через первый и второ дешифраторы к первым входам элементов И, при этом выход первого .блока совпадений через первый элемент НЕ подключен к второму входу первого элемента И, а выход нторого блока совпадений через второй элемент НЕ пoдключek к второму входу второго элмента И, выход которого объединен .со входом вентиля и выходом первого элемента И и является первым выходом блока контроля качества информации, вторым и третьим выходами которого являются соответственно выходы первого и второго блоков совпадения, а первым и вторым входами блока контроля качества информации являются соответственно вторые входы второго и первого счетчиков.

Источники информации, принятые во внимание при экспертизе

Авторы

Даты

1981-11-07—Публикация

1980-03-07—Подача