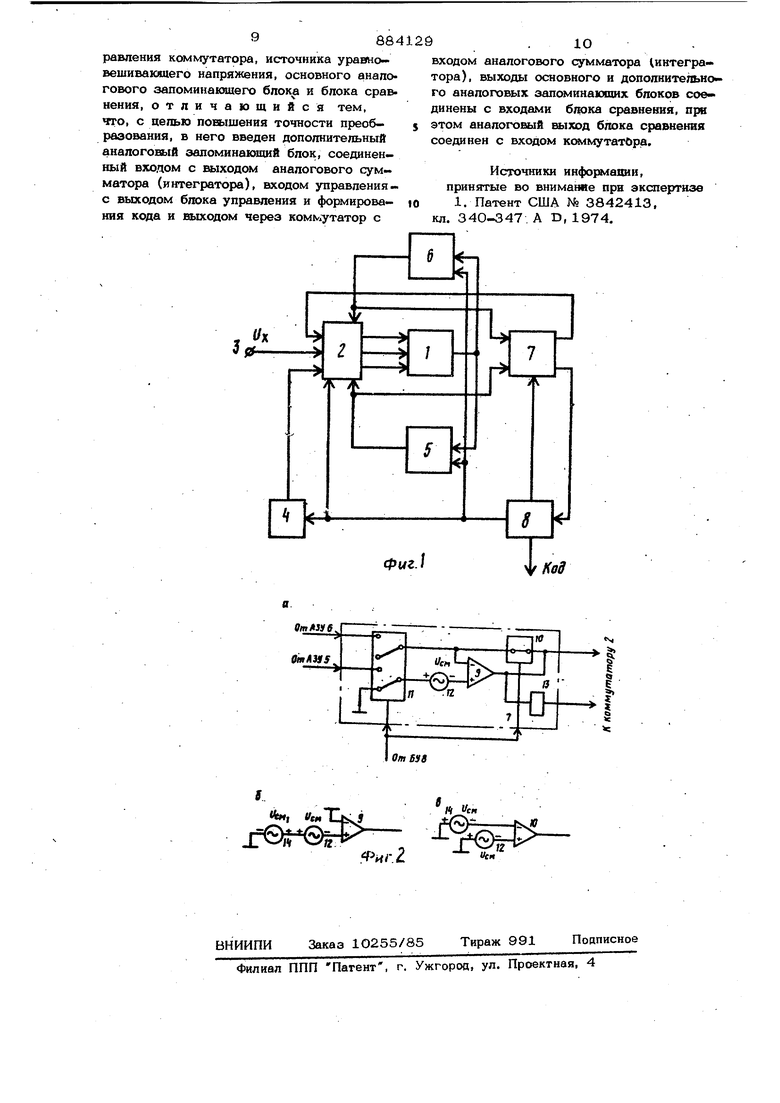

минающего блока и блока сравнения, введен дополнительный аналоговый запоминающий блок, соединенный входом с выходом аналогового сумматора (интегратора) входом управления - с выходом блока управления и формирования кода и выходом через коммутатор - с входом аналогового сумматора (интегратора), выходь основного и дополнительного аналоговых запоминающих блоков соединены с входами блока сравнения, причем аналоговый выход блока сравнения соединен с входом коммутатора. На фиг. 1 представлена блок-схема ус тройства; на фиг. 2 - структурная электрическая схема. Рециркуляционный преобразователь напряжения в код двойного уравновешивания, содержит аналоговый сумматор (интегратор) 1, коммутатор 2, входную шину 3 устройства, источник 4 уравновешивающего напряжения, аналоговые запоминающие блоки 5 и 6, блок 7 сравнения, блок 8 управления и формирования кода. Входы аналогового сумматора (интегра тора) 1 через коммутатор 2 соединены с входной шиной 3 устройства, выходами источника 4 уравновешивающего напряжения и аналоговых запоминающих блоков 5 и 6. Выход аналогового сумматора (ин тегратора) 1 соединен с входами аналоговых запоминающих блоков 3 и 6, выходы которых соединены с входами блока 7 сравнения, цифровой выход которого соединен с входом блока 8 управления и формирования кода, выходы которого соединены с входами управления коммутатора 2, источника 4 уравновешивающего напряжения, аналоговых запоминающих блоков 5 и 6 и блока 7 сравнения, аналоговый выход которого соединен с входом коммутатора 2. Устройство работает следующим образом. В устройстве реализуется алгоритм двойного уравновешивания, в котором по результату сравнения преобразуемого напряжения и у и с эталонным напряжением U эталонные напряжения одного знака 11, , . -.,,, II. --т (ИР Ivi суммируются либо С прео vifc л / - tf разуемым напряжением либо с эталонным напряжением. Цепи рециркуляции напряжений для преобразуемого напряжения и эталонным напряжениемвыполнены раздельными. Преобразуемое напряжение (J подается на первый вход блока 7 сравне ния путем рециркуляции по цепн аналогоВЫЙ сумматор (интегратор) 1 - аналоговое запоминающее устройство 5 - комму- атор 2, Эталонные напряжения передаются на второй вход блока 7 сравнения после рециркуляции по цепи аналоговый сумматор (интегратор) 1 - аналоговое запоминающее устройство 6 - коммутатор 2. Напряжения U0x-( и ®Р вом и втором входах блока 7 сравнения изменяются при применении положительных эталонных напряжений и разрядности преобразования Y по тактам уравновешивания I (о/2) следующим образом вхлГЧ(ДиГ-.Л ВУ.2,Г. (н N-1. -/ ® -1 л-i прямой и инверсный коды результата сравнения на вь1ходе блока 7 сравнения, множитель (-1) учитывает изменение знака на выходе аналогового сумматора (интегратора) 1. Тожде- сгг енный результат преобразования может быть получен при применении отрицательных эталонных напряжений - . Каждый такт преобразования состоит из двух полутактов, которые выполняются по сигналам блока 8 управления и формирования кода. В первом полутакте преобразуемое напряжение (J присутствующее на входной шине 3 устройства, через коммутатор 2 и аналоговый сумматор (интегратор) 1 вводится в аналоговый запоминающий блок 5. Во втором полутакте эталонное напряжение U старшего разряда кода с выхода источника 4, уравновешивающего напряжения, также через коммутатор 2, аналоговый сумматор (интегратор) 1 передается в аналоговый запоминающий блок 6. Напряжения с ходов аналоговых запоминаклдих блоков 5 и 6 поступают в блок 7 сравнения, где происходит их сравнение. По сигналу управления блок 7 сравнения вырабатывает сигнал результата сра& нения, который сохраняется в течейие следующего такта преобразования и ис пользуется для управления преобрйзовани- iiujlbOY е iv: MU jiiраодспил iiucvu oovoanr « ем в следующем такте. Если -U)(U2,TO в первом полутакте второго такта преобразования одновременно с напряжением- Ux с выхода аналогового запоминающего блока 5 и выхода источника 4 уравцовешивакмцего напряжения кс 4мутатором 2 на в;сод аналогового сумматора (интегратора) 5,1 подается эталонное напряжение следующего разряда f 2 - Т выходе

58

аналогового сумматора (интегратора) 1 формируется напряжение U - (Jg, которое сравнивается в следующем полутакте с эталонным напряжением (i. При-U 7-U в первом полутакте преобразуемое напряжение рециркулирует без изменения, во втором полутакте аналоговый сумматор (интегратор) 1 суммирует эталонное напряжение - и с выхода аналогового запоминающего блока 6 и эталонное напря- жение U,ji. Далее выполняется новое сравнение напряжений на выходах аналоговых запоминающих блоков 5 и 6 и вырабатывается сигнал результата сравнения Хд. По нему в следующем такте преобразования эталонное напряжение U - - суммируется с напряжением с выхода аналогового запоминающего устройства 5 или 6. Аналогично выполняются такты уравновешивания с использованием эталонных напряжений следующих разрядов. По результатам сравнения X; блок В управления и формирования кода вырабатывает код преобразуемого напрял ения

.

N 9 + Т Г -У Т v.A

При преобразовании знакопеременных напр яжений вместо эталонного напряжения и в первом такте преобразования на вход аналогового сумматора (интегратора) 1 коммутатором 2 подается нулевое напряжение. Работа устройства не меняется, если выполняется интегро- суммирование- преобразуемых и эталонных напряжений в аналоговом сумматоре (интеграторе) 1. На выходе последнего в этом случае присутствуют линейно изменяющиеся напряжения. Преобрзазованне с интегро-суммированием обеспечивает по-. давление шумов и помех в устройстве.

В оое цепи рециркуляции напряжений входит аналоговый сумматор (интегратор) 1, который вносит равные аддитивные погрешности в цепи рециркуляции напряжеНИИ. Блок 7 сравнения реагирует на разностный сигнал напряжения, поэтому аддитивная погрешность аналогового сумматора (интегратора) 1 не влияет на ре- дультат преобразования. Аналоговый сум- матор (интегратор) 1 выполняется на основе суммирующего (интегрирующего) операционного усилия, который меняет знак входных напряжений. В смежных тактах рециркуляции напряжений соста&ляющие погрешности входят в результирующие сигналы с противоположными знаками и в значительной степени (до 10- 1ОО раз) компенсируются.

29«

Так как цепи рециркуляции напряжени при изготовлении в едином технологическом процессе и близком расположении элементов на кристалле или подложке вследствие корреляции имеют бш1зкие по значениям параметры, на результат преобразования влияют не абсолютные значения погрешностей, а разности одноименных погрешностей близких по параметрам элементов, Вр еменные и температурные дрейфы параметров элементов из-за малой длительности цикла преобразования У} тактов преобразования, дгштельность такта преобразования 0,5-5 мкс и рециркуляции напряжений с изменяющимися знаками в смежных тактах-уравновешивания оказывают малое влияние на результат преобразования.

Рециркуляция напряжения по первой рециркуляции вызывает появление в каждом такте преобразования аддитивной сГо и мультипгог итивной (. составляющих погрешностей, по второй цепи рециркуляции - аддитивной ( мультипликативной d) +л(Гцл составляющих погрешностей. В конце цикла преобразования на входах блока сравнения присутствуют напряжения

%хГ-ик - м.

((,-.,U)/ ьхГ- /И-сГ.-лсГ).

С- - . -ДсГ) X (ш ЧчиЧ-ЯБлок 7 сравнения реагирует на разностный сигнал uk . для оценки Д получают, пренебрегая составляющими погрешности выше первого порядка малоега

((и -ц}иН)..|с«м-и)(иГ(Х-.-Х..;а(,иИ). |(..i..XH)-x,,U,.)(

Ч(v- i} - 4 C-D -cXi-Xi-HJ -jy

где Су- погрешность квантования;

-V 0,001-rOpOOl.

. Ои,л

ДАЧ

Алч

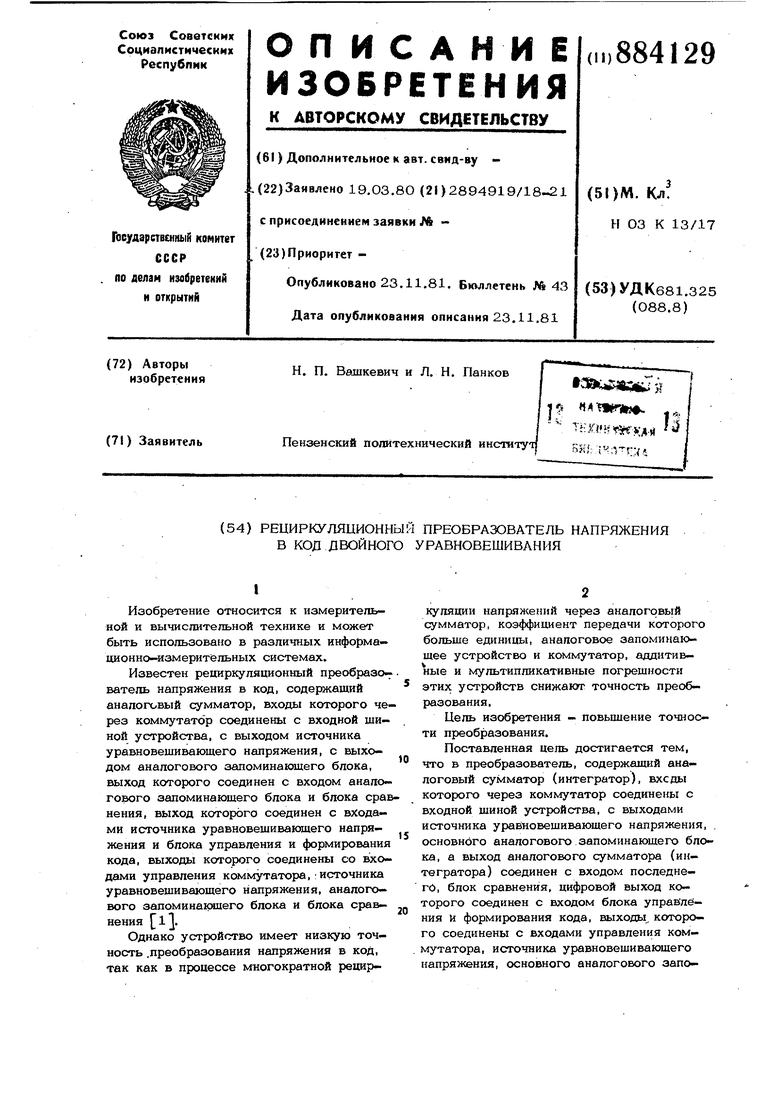

При близких значениях аддитивной погрешности в смежных тактах преобразования она практически не влияет на резупъДС -О) На тат преобразования 2 (-1 пичие мупьтиппикативной погрешности в малой степени влияет на результат преобразования, так как эта составляющая погрешности вызывает пропорциональные изменения преобразуемого напряжения U и эталонных напряжений , В основном на результат преобразования влияет составляющая погрешности Л сГ, обусловленная неидентичностью цепей рециркуляции Напряжений. Однако современная технология изготовления элементов позволяет по- лучить 0,001-0,0001. Вследствие этого составляющие погрешностей преобра зования, вызванные цепями рециркуляции напряжений, в предлагаемом устройстве могут быть уменьшены не менее чем в 10 раз. При выполнении блока 7 сравнения, на пример, на основе операционного усилителя 9, (фиг. 2) Q помощью коррекции погреш ностей можно дополнительно повысить точность преобразования. Для проведения коррекции по сигналам блока 8 управления и формирования кода, переключате - лем Ю замыкается цепь обратной связи операционного усилителя 9, вход oneрационного усилителя 9 переключателем 11 соединяется с обшей шиной устройств Операционный усилитель 9 во время коррекции работает в режиме повторителя входного напряжения и выдает на аналого вый выход блока 7 сравнения напряжение равное напряжению смещения нуля операционного усилителя 9. Наличие этого напряжения показано источником 12 напряжения смещения U ,ч... Во время коррекции аналоговый выход блока 7 сравнения через коммутатор 2 подключается к входу аналогового сумматора (интегратора) 1. Напряжение суммируется с рециркулирующими напряжениями. В зависимости от номера такта преобразования напряжение суммируется либо с напряжением с напряжением конце второго полутакта рециркуляции напряжений блок 7 сравнения переводится в режим сравне ния напряжений, Перекшочателем 10 размыкается цепь обратной связи операционного усилителя 9, переключателем 11 ег входы соединяются с выходами аналоговых запоминающих блоков 5 и 6. Сигнал результата сравнения V формируется элементом 13 и передается в блок 8 уп равления и формирования кода. 8 98 В процессе очередного сравнения источ- ник 12 напряжения смешения (J присущего операционному усилителю 9, и источник 14 напряжения и эквивалентный зафиксированному в аналоговом запоминающем устройстве 5 или 6 напряжению (J., включены таким образом, что на входы операционного усилителя 9 воздействует разностный сигнал погрешности (фиг. 2). Так как значения напряжения Uj-. равны значениям напряжения смещения U(- операционного усилителя 9 в MOvieHT времени, непосредственно предшествующий сравнению, разностный сигнал погрешности Л составляет 0,010,1-ю долю первоначального сигнала. Для выполнения коррекции не требуется дополнительное время, так как блок 7 сравнения находится в режиме коррекции в те- чение ботхьшей части такта преобразования и переводится в режим сравнения только в конце его. Коррекция выполняется непрерывно в течение всех тактов уравновешивания, поэтому в указанных выше пределах ослабляется влияние на результат преобразования и временных и температурных дрейфов напряжения смещения )(-1л операционного усилителя 9. Таким образом, применение в устрой- стве алгоритма двойного уравновешивания с раздельными цепями рециркуляции пре образуемого и эталонных напряжений по вышает точность преобразования не менее, чем в 10 раз по сравне ™ю с точностью преобразования известного устройства. Коррекция погрешностей блока 7 сравнеНИЯ дополнительно повьппает точность пре образования. В устройстве используются эталонные напряжения одного знака, что упрощает построение источника 4 уравновешивающего напряжения и повышает его точность. Формула изобретения Рециркуляционный преобразователь напряжения в код двойного уравновешивания, содержащий аналоговый сумматор (интегратор), входы КОТОРОГО через коммута- тор соединены с входной шиной устройства, с выходами источника уравновехиива ющего напряжения, основного аналогового запоминающего блока, а выход аналогового сумматора (интегратора) соединен с входом последнего, блок сравнения, цифрозой выход которого соединен с входом блок управтюния и формирования кода, выходы которого соединены с входами управления коммутатора, источника уравновешивакшего напряжения, основного аналогового запоминакяиего блока и блока сравнения, отличающийся тем, что, с целью повышения точности преобразования, в него введен дополнительный аналоговый заломинаюший блок, соединенный входом с Еыходом аналогового сумматора (интегратора), входом управленияс выходом блока управления и формирования кода и выходом через коммутатор с

входом аналогового сумматора интегратора), выходы основного и дополнительного аналоговых запоминающих блоков соединены с входами блока сравнения, при этом аналоговый Ш9|ход блока сравнения соединен с входом коммутатора.

Источники информации, принятые во внимание при экспертизе

1. Патент США № 3842413, кл. 340-347. А D, 1974.

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь постоянного напряжения в последовательный код | 1975 |

|

SU606206A1 |

| Функциональный преобразователь напряжения в код | 1979 |

|

SU928634A2 |

| Преобразователь напряжения в код | 1975 |

|

SU729839A1 |

| Функциональный преобразовательНАпРяжЕНия B КОд | 1979 |

|

SU818004A1 |

| Аналого-цифровой преобразователь | 1985 |

|

SU1277396A1 |

| Источник калиброванных напряжений | 1986 |

|

SU1345179A1 |

| Аналого-цифровой преобразователь интегральных характеристик электрических величин | 1981 |

|

SU1035790A1 |

| Способ измерения действующего значения переменного напряжения | 1983 |

|

SU1140054A2 |

| Вычислительный преобразовательНАпРяжЕНия B КОд | 1979 |

|

SU822347A1 |

| Аналого-цифровой преобразователь | 1984 |

|

SU1197079A1 |

Авторы

Даты

1981-11-23—Публикация

1980-03-19—Подача