га, где п - количество разрядов преобразователя, являются выходным информационными шинами устройстваj а первый, второй и третий выходы подключены соответственно к первом второму и третьему входам блока контроля, выход которого является первой вьпсодной контрольной шиной и подключен к третьему входу блока управления, девятый и десятый выходы которого подключены соответст венно к первому и второму входам счетчика, выход которого является второй выходной контрольной шиной устройства и подключен к четвертому входу блока управления, одиннад цатьш вьрсод которого является шиной Конец преобразования. Г - . 2. Преобразователь по п. 1, от личающийся тем, что блок управления выполнен на постоянном запоминающем устройстве, регистре, генераторе тактовых импульсов, ком мутаторе, дешифраторе, первом и втором счетчиках, мультиплексоре, первый, второй, третий и четвертый информационные входы которого являются соответственно первым, вторым, третьим и четвертым входами блока управления, пятьй информадаонный вход подключен к выходу первого счетчика, шестой и седьмой информационные входы подключены соответственно к первому и второму выходам второго счетчика, выход подключен к управляющему входу ком татора, первый, второй и третий управляющие входы подключены соот79ветственно к первому, второму и третьему выходам реги.стра, выходы с четвертого по четырнадцатый которого подключены к соответствующим информационным входам дешифратора выходы с пятнадцатого по девятнадцатый подкл|очены к соответствующим первым информационным входам коммутатора, выходы с двадцатого по двадцать четвертый подключены к соответствующим вторым информационным входам коммутатору, выходы которого подключены к соответствующим-входам постоянного запоминающего устройства, выходы которого подключены к соответствующим информационным входам регистра, управляющий вход которого подключен к выходу генератора тактовых импульсов, при этом первый и второй управляющие входы дешифратора подключены к шине нулевого потенциала, первый, второй, третий и четвертый выходы подключены соответственно к первому, второму, третьему и четвертому входам первого счетчика, пятый и шестой выходы подключены соответственно к первому и второму входам второго счетчика, седьмой, восьмой, девятый, десятый, одиннадцатый, двенадцатый, тринадцатый, четырнадцатый, пятнадцатый, шестнадцатый и семнадцатый выходы являются соответственно третьим, четвёртым, пятым, шестым, первым, вторым,, седьмым, восьмым, девятым, десятым и .одиннадцатым выходами блока управления, приче|4 пятый вход первого счетчика объединен с четвертым входом мультиплексора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналого-цифровой преобразователь | 1985 |

|

SU1277396A1 |

| Дифференциальный цифроаналоговый преобразователь | 1983 |

|

SU1138949A1 |

| Аналого-цифровой преобразователь | 1984 |

|

SU1226664A1 |

| Цифроаналоговый преобразователь | 1981 |

|

SU1005298A1 |

| Цифроаналоговый преобразователь | 1982 |

|

SU1051701A1 |

| Цифро-аналоговый преобразователь | 1981 |

|

SU953721A2 |

| Аналого-цифровой преобразователь | 1985 |

|

SU1297224A1 |

| Параллельно-последовательный аналого-цифровой преобразователь | 1985 |

|

SU1305851A1 |

| Цифроаналоговый преобразователь | 1979 |

|

SU864548A1 |

| Устройство цифроаналогового преобразования | 1984 |

|

SU1221755A1 |

1. АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ, содержащий первый, второй и третий запоминающие конденсаторы, усилитель, первый и второй блоки ключевых элементов, источник опорного напряжения, ключевой элемент,, блок сравнения, блок управления, первый вход которого явлЯ- етс-я шиной .Запуск, первый выход подключен к управляиицему входу ключевого элемента, информационный вход которого подключен к первому выходу источника опорного напряжения, второй выход которого подключен к первому информационному входу первого блока ключевых элементов и первому выводу второго запомина(о1цего конденсатора, второй вывод которого подключен к выходу ключевого элемента и объединен с вторым информационным входом первого блока ключевых элементов, управляющий вход которого подключен к второму выходу блока управления, первый выход подключен к первому информационному входу второго блока ключевых элементов и первому выводу третьего запоминающего конденсатора, вто рой вывод которого подключен к второму выходу первого блока ключевых элементов и объединен с вторым информационным входом второго блока ключевых элементов, выход подключен к входу усилителя, который через первый запоминающий конденсатор подключен к -общей шине, выход усилит теля подключен к третьему информационному входу второго блока ключевых элементов и к входу блока срав(Л нения, о тличающийся тем, что, с целью повышения достоверности преобразования, введены регистр сдвига, блок контроля, счет-чик, аналоговый коммутатор, первый информационный вход которого является .аналоговой входной тиной устройства, второй информационный вход ф подключен к общей шине, выход подключен к входу усилителя, первый и второй управляющие входы подключены соответственно к третьему и четвертому выходам блока управления, пятый и шестой выходы которого подключены соответственно к первому и второму управляющим входам второго блока ключевых элементов, седьмой и восьмой выходы подключены соответственно к первому и второму управлякицим входам регистра сдвига, информационный вход которого объединен с вторым входом блока управления и подключен к выходу блока сравнения, п выходов регистра одни

Изобретение относится к вычислительной и цифровой измерительной технике и может быть использовано для преобразования аналоговых вели-чин в цифровые.

Цель изобретения - повьш1ение достоверности аналого-цифрового преобразования.

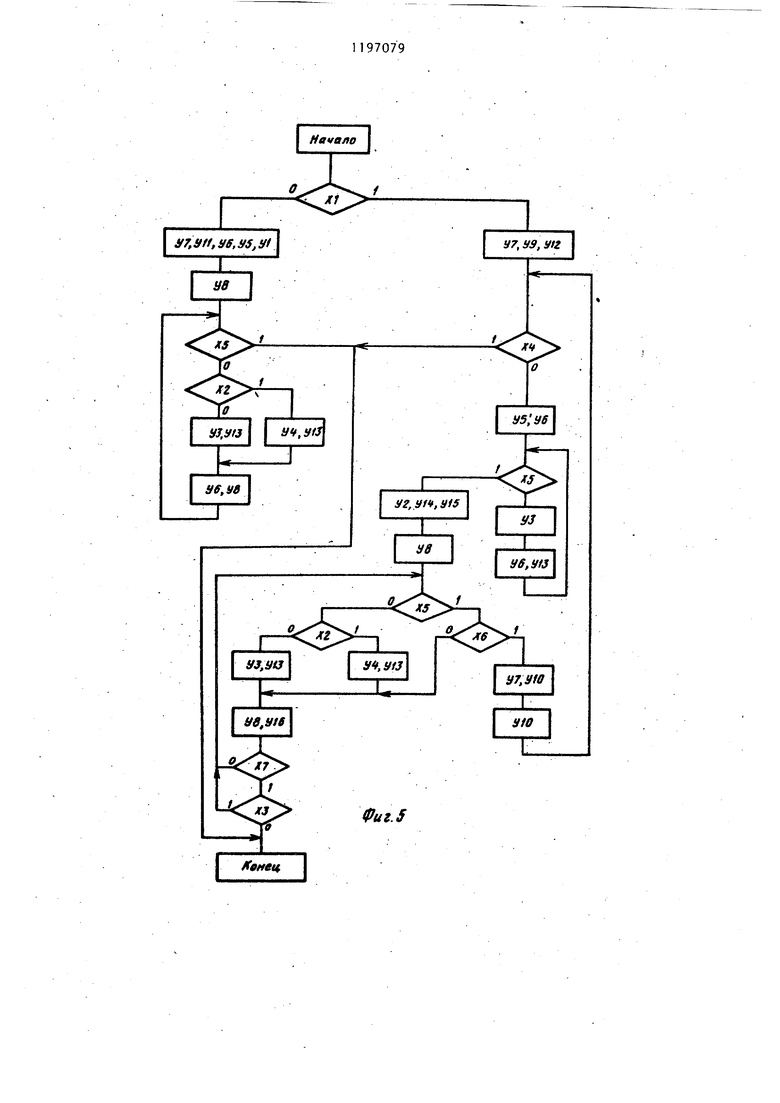

На фиг. 1 представлена структурная схема аналого-цифрового преобразователя i на фиг. 2 - функциональная схемаблока контроля; на фиг. 3 и 4 - алгоритм работы аналогоцифрового преобразователяi на фиг.5закодированный граф микропрограмм

работы устройства; на фиг. 6 - функциональная схема блока управления; на фиг. 7 и 8 - функциональные схемы первого и второго блоков ключевых злементов.

Аналого-цифровой преобразователь (фиг. 1) содержит аналоговую входную 7 : ет суммированию эталонного уровня и,. и преобразуемого напряжения и в следующем такте преобразования а значение сх.| 1 - вычитанию этало ного уровня и преобразуемого напряжения-иI. Полученное; значение разрядного коэффициента а, заносится в регистр 12 сдвига. На этом первьй такт преобразования заканчива ется. На втором такте в соответствии с соотношением (2) формируется напряж ние U2 на первом запоминающем конденсаторе 3 с помощью усилителя 4, запоминающего конденсатора 10, второго блока 11 кл1р.чевь1х элементов и блока 18 yпpaв ;I,e|Hия. По команде блока 18 управлен 1Я конденсатор 10 включается через второй блок 11 клю вьк элементов в цепь обратной связи усилителя 4 таким образом, чтобы , обеспечивалась подача напряжения и, обратной полярности на конденсатор 3, В результате на конденсато ре 3 сформируется напряжение U - U - а,и,. . Напряжение Ug с выхода усилителя 4 поступает на вход блока 5 сравнения. На выходе блока 5 в соответствии с условием (2) формируется значение второго разрядного коэффициента а, которое записывается в .регистр 12 сдвига. Затем с помощью блока 18 управления запоминающих конденсаторов 8 и 10, первого блока 9 ключевых элементов - формируется второй эталонный урове Uon По команде блока 18 управления первый блок 9 ключевых эл ментов включает запоминающие конден саторы 8. и 10 параллельно. В резул тате происходит перераспределение заряда между конденсаторами 8 и 10 таким образом, что на них у становит ся напряжение второго эталонного .Uo уровня и, На этом второй такт преобразования заканчивается. В остальных (п - 2) тактах устройство работает аналогичным образом. Лри этом для правильной работы устройства необходимо выполнение условия ГСЗ С10 ею С8 (cip - 1) . Пример преобразования входной аналоговой величины А 10 в 679разрядный код золотой 1 пропорции приведен в табл. 1. Погрешность линейности устройства зависит от смещения нуля усилителя 4 и блока 5 сравнения, точности выполнения условия (4). Указанные составляющие меняют-ся с течением времени и под воздействием условий внешней среды, что приводит к увеличению погрещности линейности. Последнее обстоятельство эквивалентно формированию эталонных уровней Одт.ц с некоторьми отклонениями. При этом значения абсолютных погрешностей для старших разрядов будет большими,а для младпшх малыми. В процессе метрологического контроля определяется граница между точными и неточными разрядами. Метрологический контроль линейности выходной характеристики проводится начиная, с (р +-2)-го разряда. Разряды с номерами меньшими р + 2 считаются точными. Процедура контроля заключается в (п - р - 1)-кратном кодировании эталонного вспомогательного сигнала А,т значение которого равно 0. В процессе любого f-ro кодирования вспомогательный сигнал Agy О преобра зуется в (р + 1 +D-разрядный код путем последовательного сравнения и алгебраического суммирования его с набором из р +1 + t эталонных уровней. Признаком наличия откло-. нений весов разрядов преобразователя является нарушение соотношения (1), что приводит к появлению в процессе кодирования запрещенных кодовых комбинаций. Разрешенными, например, для кода золотой 1 пропорции , являютс д кодовые комбинации, состоящие из триад разрядов вида Tl1 или 111. Невыполнение указанного условия в процессе {.-то кодирования является признаком того, что погрешность преобразования превысила заданную величину. В каждом следующем кодировании число эталонных уровней, участвующих в преобразовании, увеличивается на единицу. В режиме метрологического контроля устройствоработает следуюв м образом. По команде блока .18 управления запоминающий конденсатор В заряжается через ключевой элемент 7 от источника 6 опорного напряжения до 9 . напряжения оп Затем с помощью блоков 9 и 11 ключевых элемен тов, усилителя 4, запоминающих конденсаторов 8, 10 и 3 и блока 18 управления формируется (п-р-2)-й эталонный уровень U -V Процес-с формирования эталонного уровня Ug|. п-р-г заключается в следующем. По команде блока 18 управления первый блок 9 ключевых элемен тов включает конденсаторы 8 и 10 параллельно. В результате, на них 11 и on установится напряжение и -.,- . Затем второй блок .11 ключевых элементов . включает конденсатор 10 в цепь обратной связи усилителя 4. За ряд конденсатора 10 полностью передается на запоминающий конденсатор 3.После этого первый блок 9 ключевых элементов снова - включает конден саторы 8 и 10 параллельно. В резуль тате, на них установится напряжение Uon -. Указанная процедура пов теряется (п-р-3) раз, пока на запоминающем конденсаторе 10 не установится напряжение (п-р-2)-го эталонного уровня Ujf „. р,2 ., . ЗаIтем по команде блока 18 управления на запоминающий конденсатор 3 через второй вход аналогового коммутатора 2 подается эталонный вспомогательный сигнал А 0. В результате, конденсатор 3 заряжается до напряжения и 0. Блок 18 управления генерирует набор команд, обесйечивающих преобразование иJ в (р+2)-ра рядный код способом, описанным вьше Полученный в результате преобразования код анализируется блоком 14 контроля, который реализует логичес кую функцию fp(а;). При параметре кода золотой пропорции р 1 указанная функция имеет вид f,(a,-) а,-.а;,-а..+ а-, -а,-. а,Функция f.(aj) принимает значение 1 только на разрешенных наборах аргументов вида 1 Т Т или Til Блок 14 контроля по мере формирования разрядов выходного кода в сдвиговом регистре 12 каждые три такта опрашивается блоком 18 управления, выходной сигнал блока 14 f, () # 1 соответствует сигналу расстройка 79 (преобразования. Так как аргумента|ми функции f, (а) являются три переменных., то число п, контролируемых разрядов выходного кода, формируемого в режиме.контроля, должно быть кратно трем п | 31. Погрешность квантования данного класса аналого-цифровых преобразователей составляет +1 младшего разряда, что позволяет проводить метрологический контроль с точностью +1 младший квант. Поэтому, если число тактов преобразования соответствует разрядности выходного кода п 31 + 1, то сигнал контроля формируется в результате анализа п 31 старших разрядов кода без учета значения младшего разряда. Если число тактов преобразования соответствует разрядности выходного кода п,( 31 + 3, то сигнал контроля формируется в результате анализа п 31 3 разрядов кода, значение младшего ( 31 + 3)-го разряда которой повторяет значение (31 + 2)-го разряда, полученного на последнем такте кодирования. На этом процедура контроля (р + 2)-го разряда заканчиваетсй. Контроль (р 4- 3)-го разряда преобразователя начинается с формирования (п-р.+3)-го эталонного уровня IT Uon Затем вспомогательЭТп-р- , . ный аналоговый сигнал Л . О преобразуется в (р + 3)-разрядный код, который анализируется блоком 14 контроля. Контроль остальных разрядов преобразователя производится аналогичным образом. Номер контролируемого разряда фиксируется счетчиком 16. Если в процессе контроля f-ro разряда блок 14 контроля сформирует сигнал Расстройка преобразователя, на выходе счетчика 16 зафиксируется число п« С - 1 достоверных разрядов.аналого-цифрового преобразователя, обеспечивающих в процессе кодирования заданную погрешность линейности. Пример контроля 6-го разряда аналого-цифрового преобразователя в кодах золотой I пропорции при условии, что вес 6-го разряда имеет значение 9,4 вместо 11,0, блок 14 логических элементов анализирует триаду разрядов блока 12 с номерами 1, 2 ,3, приведен в табл. 2. Результат опроса блока 14 конт:роля на шестом такте преобразования показал, что в регистре 12 сдвига сформировалась запрещенная кодовая комбинация. Достоверными являются п, 5 младшихразрядов преобразовател Блок 18 управления реализован в виде управляющего автомата с програ мируемой логикой. Алгоритм работы управляющего автомата приведен на фиг. 3 и 4, где: CTj - счетчик пересчета на три состояния (блок 52 на фиг. 6), СТ - счетчик тактов, разрядность которого равна m logjП (блок 51 на фин. 6) положение ключа Ki: П1 соответствует замкнутому состоянию ключа.j положение АК. П1 соответствует 1 коммутации на выходе аналогового коммутатора 2 входной преобразуемой величины, положение А : П2 соответствует коммутации на выход анало гового коммутатора 2 нулевого вспомогательного сигнала; 1- условие, определяющее режим работы устройства: преобразование (0) или контроль (1), 2- установка в начальное состоя ние регистра сдвига Pj. 12 и счетчик 51 тактов СТ, заряд запоминающих конденсаторов 8 и 10 от источника опорного напряжения 6 черезключево элемент 7 и ключи К1.1 и К1.2 первого блока 9 кл1очевых элементов, коммутация на выход аналогового . коммутатора 2 входного преобразуемо го сигналаi 3- запись в регистр 12 сдвига значения старшего разряда выходного кода, 4- проверка условия Конец преобразования ;5- условие, определяющее полярность преобразуемого напряжения; 6,7 - счетчик 51 тактов СТ-,- увеличивает свое состояние на единицу в зависимости от условия 5 запоминающий конденсатор 10 соответствующими обкладками включается через ключи К2.1, К2.2, или КЗ.1, КЗ.2 блока 11 ключевых элементов в цепь обратной связи усилителя 4; 8- запись в регистр 12 сдвига значения i-ro разряда выходного кода, формирование i-ro эталонного уровня Ugr;; 9- установка в начальное состо ние регистров 12 сдвига, счетчика 79. 12 51 тактов СТ-г и счетчика 16 достовернык разрядов преобразователяj 10- условие окончания контроля; 11- формирование первого эталонного уровня , 12- условие формирования i-ro эталонного уровня , соответствующего i-му контролируемому разряду, 13- разряд запоминающего конденсатора 10; 14- счетчик 51 тактов СТ увеличивает свое состояние на единицу, формирование следующего эталонного уровня; 15 - счетчик 51 тактов СТ принимает значение счетчика 16, установка в начальное состояние счетчика 52 пересчета на три СТ,, коммутация на вькод аналогового коммутатора 2 нулевого вспомогательного сигналаJ 16 - запись в регистр 12 сдвига значения старшего разряда выходного кода; 17 - проверка условия Конец преобразования i 18 - условие, определяющее полярность преобразуемого напряжения 19-20 - счетчик 51 тактов СТ увеличивает свое состояние на единицу в зависимости от условия 18 запоминающий конденсатор 10 соответствующими обкладками включается в цепь обратной связи усилителя 4 21- записьВ регистр 12 сдвига значения i-ro разряда выходного к.ода, счетчик 52 пересчета на три СТз увеличивает свое состояние на единицуi 22- если в регистре 12 сдвига сформировалисъ очередные три разряда выходногокода,то анализируетсявыходной сигнал блока 14 контроля-, 23- условие правильного преобразования, 24 - если число разрядов выходного кода равно 3i + 2, то формируется (3i + 3)-й разряд путем сдвиг.а на один разряд кода в регистре 12; 25- установка регистра 12 сдвигл в нулевое состояние, счетчик 16 достоверных разрядов преобразователя увеличивает свое состояние на единицу, 26- счетчик 51- тактов СТ принимает значение счетчика 1б-процедура контроля продолжается, пока не будут проконтролированы все разряы преобразователя.

О 1 9,4 0-9,,41

-9,4 Т 6,8 -9,4+6, 1

-2,6

-2,6 7 4,2 -2,6+4, Т

-1,6

1,6 1 2,6 1,6-2,,0 1 Т

-1,0 1 1,6 -1,0+1, 1

0,6

6 0,6 1 1,0 0,6-1,,4 1 т 111 1 2,0

Т а б л и ц. а 2

1,0

о о

X X 0,6

о

1

1,0

о о

X X

1 1 0,6

ft (

ut.i

Рг/:/.. CTrCt mJ: / Kt, , /ff.Z: rtf, / AK: n1

.,

СТгП.,

CTf1.

i)

I конец I

С7т , /f2.t-nf f ffZ.2--tif

фиг.З

CTr , ,К3.,К3.2:п1

Рг-KIPrt

Ki,1:-n1, Kl.

/Г/.Л--/7/, K1.2: 1 Н3:-п1

CTrCt.mJ-CTff.mJ,

CT3ft.JJ:--l,

15

(2.t-ftf, ff2.

CTr-CTr t, ftt.f-fjf,iff.Z:-af

Т

tTT-CTr- t

tff

,/rj./.,/rj:/.-.

26 CTr С1,

Ъ

ФигЛ

Pr::Rtpf.

21 Crj.-acr,/

I KOH9t П

IPut.6

фиг 8

| Швёцкий Б.И | |||

| Электронные цифровые приборы | |||

| Киев, Техника, 1981, | |||

| с | |||

| Устройство для устранения мешающего действия зажигательной электрической системы двигателей внутреннего сгорания на радиоприем | 1922 |

|

SU52A1 |

| Шляндин В.М | |||

| Цифровые, электроизмерительные приборы | |||

| М.: Энергия, | |||

| Контрольный висячий замок в разъемном футляре | 1922 |

|

SU1972A1 |

| Питательный кран для вагонных резервуаров воздушных тормозов | 1921 |

|

SU189A1 |

| , | |||

Авторы

Даты

1985-12-07—Публикация

1984-04-18—Подача