(54) ПРЕОБРАЗОВАТЕЛЬ НАПРЯЖЕНИЯ В КОД

| название | год | авторы | номер документа |

|---|---|---|---|

| Функциональный преобразовательНАпРяжЕНия B КОд | 1979 |

|

SU818004A1 |

| Функциональный преобразователь напряжения в код | 1979 |

|

SU928634A2 |

| Преобразователь кода в импульсы ступенчатой формы | 1981 |

|

SU974569A1 |

| Аналого-цифровой преобразователь | 1987 |

|

SU1462479A1 |

| Преобразователь напряжения в код | 1974 |

|

SU503362A1 |

| Преобразователь напряжения в код | 1977 |

|

SU705671A1 |

| Цифроаналоговый преобразователь | 1980 |

|

SU942258A1 |

| ПРЕОБРАЗОВАТЕЛЬ УГЛА ПОВОРОТА ВАЛА В КОД | 2003 |

|

RU2240651C1 |

| Преобразователь напряжения в код | 1976 |

|

SU599349A1 |

| Вычислительный преобразовательНАпРяжЕНия B КОд | 1979 |

|

SU822347A1 |

I

Изобретение относится к измерительгюй и вычислительной технике и может быть использовано в различных информационно-измерительных системах.

Для разгрузки ЭЦВМ, работающих в составе систем управления объектами, от несложных, но требующих значительного количества мащинного времени вычислений, последние выполняют непосредственно в преобразователях напряжения в код, при этом преобразователи в процессе определения цифрового эквивалента преобразуемого напряжения выполняют некоторые математические операции и футщиальные преобразования.

Однако приобретение дополнительных функций в таких преобразователях достигнуто применением специальной схемотехники, с утратой возможности линейного преобразования напряжения в код, вследстиве чего они обладают ограниченными функциональными возможностями.

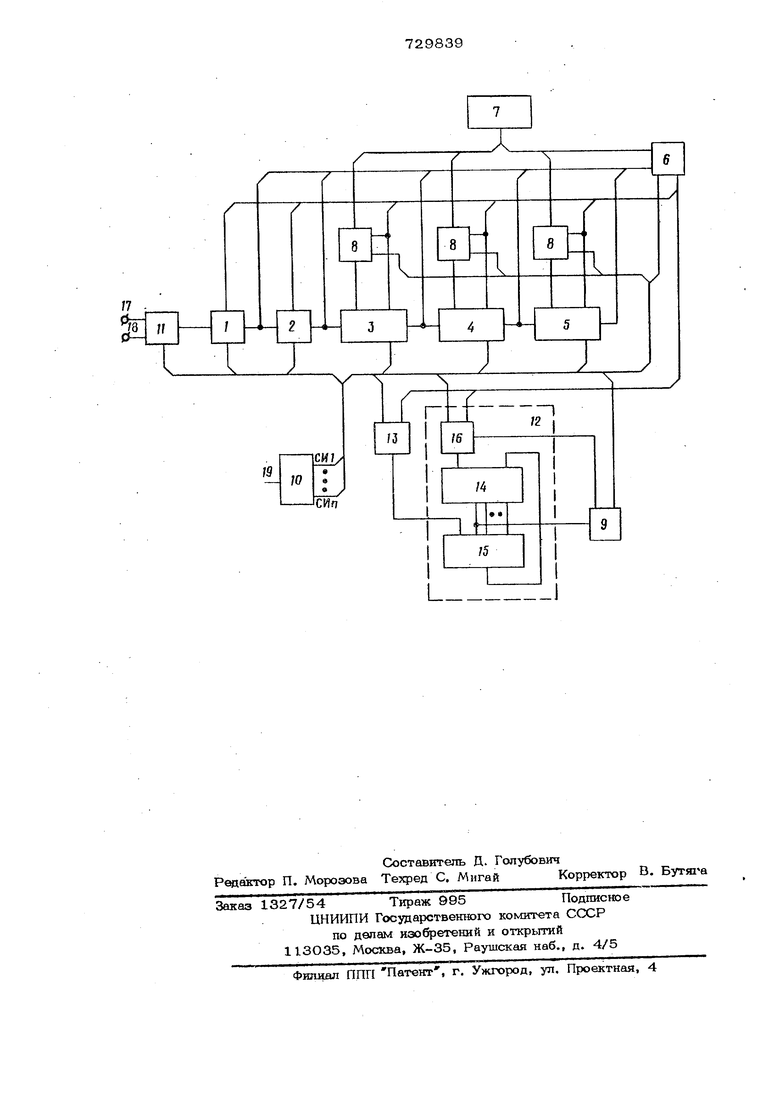

Известен тфеобразователь напряжения в код по методу поразрядного уравновешивания с умножением нескомпенсированных остатков, содержащий вычиfaюшиe усилители, блок сравнения, источник эталонного напряжения (токов), ключи, регистрнрующее устройство и распределитель сигналов. Вычитающие усилители соединены последовательно, первый вход первого усилителя соединен с входной клеммой устройства. Блок сравнения соединен первой группой входов с выходами вычитаюипсх усилителей, вторым входом с выходами источника эталонного напояжения (токов), треьим входом - с вЬгходом распределителя сигналов, выходы блока сравнения соединены с входами регистрирующего устройства и с первыми входами ключей, вторые входы которых соединены с выходами распределителя сигналов, вторые входы вычитающих усилителей через ключи соединены с выходами источшша эталонного напряжения (токов), регистр1фующее устройство соедине1ю с распределителем сигналов fl. Известный преобразователь имеет ограниченные функииональтгые возмож,fracTH, так как преобразует напряжения только в код, линейно зависящий от преобразуемого напряжения. Известен наиболее близкий но технической сущности и достигаемому результату к изобретению преобразователь аналог-цифра. Преобразователь аналог-цифра содержит усилители, блок сравнения, источнику эталонного напряжения (токов), ключи, регистрирующее устройство и распределитель сигналов. Усилители соединены последовательно, первый вход пер.вого усилителя соединен с входной клем мой устройства. Вход и выход предшествующего усилителя через соответствующий 1СЛЮЧ соединены с входом последующего усилителя. Блок сравнения соединен первой группой входов с выходами усилителей, вторым входом - с выходом источтшка этало1шого натфяже1шя (токов третьим входом - с выходом распределит ля сигналов, выходы блока сравнения соединены с входа1 Ш регистр фующего уст ройства и с первыми входами ключей, вторые входы которых соединены с выхо дами распределителя сигналов, регистрирующее устройство соединегаэ с распреде лителем сигналов. Преобразователь аналог-цифра форм1фует код, cooTBeTCTByTO щий логарифму по основанию с преобразуемого напряжения 21. Существенный недостаток известного преобразователя напряжения в код заключается в том, что он обладает orpaic чегшыми функциональными возможностями, так как ориентирован на образов ние одной функциональной зависимости кода от преобразуемого напряжения. Целью изобрете шя является расщирение функциональных возможностей преоб разователя напряжения в код путем применения единого алгоритма уравновешивания для вьшолнения ряда функциональных преобразований и формирования код по алгоритму упрощенного умножения. Это достигается тем, что в преобразователь 6 напряжения в код, содержащем соед1П1еш1ые последовательно усилители, блок сравнения, источник эталонного напряжения (токов), тшючи, регистр1фующее устройство и распредешггель сигналов, блок сравнения соединен первой группой входов с выходами усилителей, вторым входом - с выходом источника эталонного натфяжения 94 (токов), третьим входом - с выходом аспределителя сигналов, выходы блока сравнения соединены с первыми входами усилителей и ключей, вторые входы которьгх соединены с выходами распределителя сигналов, регистрирующее устройство соед1шено с распределителем сигналов, введены коммутатор, блок умножения, вьшолне1шый из регистра-сдвигателя, сумматора и узла управления, и запоминающее устройство,при чем входы коммутатора соединены с входными клеммами устройства и с выходом .распределителя сигналов, выход коммутатора соединен с вторым входом первого усилителя, третьи входы последних усилителей через ключи соединены с выходами источника эталонного напряжения (токов), первые входы узла управления и запоминающего устройства соединены с выходом блока сравнения, вторые входы узла управления и запоминающего устройства соед1ше п 1 с распределителем сигналов, входы регистрасдвигателя соединены с выходами узла управления и выходами суЛ матора, входы которого соединены с выходами регист.-. ра-сдвигателя и запоминающегх) устройства, входы регистрирующего устройства соединены с выходами узла управления и регистра-сдвигателя, вход распределителя сигналов соединен с щиной цифрового входа преобразователя напряжения в код, Зто позволяет наряду с образованием кода N преобразуемого напряжения формировать коды N ; ( 6 1,5 , фукционально связанные с преобразуемыми напряжешшми . W,,-NfU,,. .N - . Kl JL% ЧГ U I I - W -eqg u,. 1 U. 5 «-(x XПреобразователь напряжения в код (см. чертеж) содержит усилители 1,2, 3,4,5, блок сравнения 6, источник эталонного напряжения (токов) 7, ключи 8, регистрирующее устройство 9, рас- пределитеяь сигналов 10, коммутатор 11, блок умпоже1шя 12, запоминающее устройство 13. Блок умножения 12 вьшолнен из регистра-сдвигателя 14; сумматора 15 и узла управле1тя 16. Усилители 1, 2, 3, 4, 5 соединены последовательно. Блок сравнения 6 соединен первой группой входов и выходами усилителей 1, 2, 3, 4, 5 вторым входом С ВЫХОДОМ источника эталонного напряжения (токов) 7, третьим входом - с выходом распределителя сигналов 10. Выходы блока сравнения 6 соединены с первыми входакчи усилителей 1, 2, 3 4, 5 и ключей 8, вторые входы которы соед1гаены с выходами расгфеделителя сигналов. Регистр1фующее устройство 9 соединено с распределителем С1п: налов 1 Коммутатор 11 соединен с входнык1и клеммами 17,18 устройства и с выходом распределителя сигналов 1О. Выход коммутатора 11 с вторым вхо усилителя 1. Вторые входы последних усилителей 3, 4, 5 через ключи 8 соединены с выходами источника эталонног напряжения (токов) 7. Первые входы узла управления 16 и запоминающего устройства 13 соединены с выходом блока сравнения 6. Вторые входы узла управления 16 и запоминающего устрой ства 13 соединены с распределителем сигналов Ю, Входы регистра сдвигател 14 соединены с выходами узла управления 16 и выхода.ти сумматора 15, входы которого соединены с выходами регистра-сдвигателя 14 и запоминающего устройства 13. Входы регистрирующего устройства 9 соединены с выходами узла управления 16 и регистра-сдвигателя 14. Вход распределителя сигналов 1 соединен с шиной 19 цифрового входа преобразуемого напряжения в код. В основу работы преобразователя напряжения в код при вьтолнении функционалыИз1Х преобразований положен сходящийся итерационный процесс, известны как методвычислений цифра за цифрой Процесс вьфаботки кодов Ni , связанных функциональной завис1шос тью с преобразуемым напряжением, разбиваетс на 2 этана: а) уравновешивание преобразуемого напряжения Uj( путем его умножения (усиления) на убывающую иоследователь 1юсть констант, приближающих Uy к элалонному напряжению U О. и„П Cl.oc-S U Где VI - разрядность преобразования; - номер шага (ступени) преобразова1шя; - основание системы счисления; X; - кодированный результат сравнения преобразуемого напряжения со шкалой эталонных напряжений на шаге уравновешивания 396 (при о(5ра.-;ювпнни кода в смвценной системе счисления Х.(- положительно, в сил метричной системе счислетшя )«. положительно илл отрицательно); двоичные величины,;для уравновешивания со знакогюстояшсымк шагами ) €: 0,1 для уравновешизащ1я со знaкoпepe Ieнными шагами t - 1,1 $ 1; I - коэффициент, отражающий число шагов (ступеией) уравновешивания . ( С - 1 «ли t -2. ); б) 4ОР 1ФО ™ в щсфровом виде но значениям определенных на первом этапе $; xi кодов N вычислением произведения N-.n С )для всех функций, кроме логарифмической, для этой функпии код образуется суммированием предварительно вьгчисленнных константN. -Z x.tcg . Г Uo л « гакопостоянные константы $, находят из соотношения f ie --sign u fi (i -tKoc ) --Uj(2) при знаке мггаус в соотношении $,О. Знакопеременные ютнстанты определяют из cooTHomeKjcH , -lHvl uj :з) $i -Svgr, . Для дост5гжения необходимой точности преобразуемое напряжение Uy должно находиться в диапазоне 0,5 в первом случае и в диапазоне 0,250 и 4 1,5 UQ во втором случае. Для приведения преобразуемого напряжения U к указанным пиапа- зонам оно предварительно подвергается ормирован1ро путем усиления с дискрето изменяемым коэффициентом усиления« де показатель х устанавливают на сновании сравнения усиленного напряжеия Uj(pC°-(J эталонным напряжеиол UQ . Так как по пpeдлaгae юмy лгоритму уратювешивания преобразованию одвергают норм1фованное напряжение езультат преобразования коррект1фуют в цифровой форме. Далее в формулах 7 присутствует нормированное напряжеюш . При значительном f в выражении ( 1 знак стремится к можно заменить знаком равенства, так как умноженное на сходящуюся последовательность напр жение и мало отличается от эталонкого напряжения UQ Тогда, беря откю шение Uj K-UpH рассматривая его как код, соответствующий прямому преобраз ванию напряжения в код, получают X t1 , 1гпа 1ы-Ь -1 - . . . -ЧА ил Тождество (4) соблюдается, если (1..р, Тогда вычислением в цифровой форме ., X -1 „ произведения ,П ( находят ко величины, обратно пропорциональной преобразуемому напряжешпо, Выполнение двойных шагов (6. -2 умножения преобразуемого напряжения позволяет вычислить, как видно из раз новидности тождества (4), н;па с Ь 1 код величины, обратно пропорштонально корню квадратному из преобразуемохх) . напряжения а 1/ н-дан{с ъ л. При отрицательных х получают и% ( . При этом вычислегще в нифроёой ± ; формепроизведения ,,П ( И аед«п- к образованюо кода- Nпреоб

зуемого напряжения U , так как

-К.к

п1 .. Ifl

N П С1 МГ 1пН П .

Двойные шаги уравновешивания тфи отрицательных Х{, позволяют сформироКод логарифма напряжения U на а дится каж сумма констант

,)

wnw ( . 7298398 преобразуемое вать код Nj корня квадратного из преобразуемого иапряжетшя U .и N. ,n Процесс нахождения кода N отношеия двух напряжений tj, и Uo сводится к rtr14 йхождению прямого кода напряже1Л1я U умножению его на код, обрат1го пропорионалып тй преобразуемому напряжению Lf ««-d ,н .,н ...-, Код Nj, корня квадратного из преобрауемого напряжения может быть сформиован при уравновеишва ши с использовагем положительных у,, на основе тожества Гн t котором Ы J. ).Y.f пределяют на-основе традишюнных метоов линейного преобразования, а корень - из тождества ( X Ъ у, ;J, ) Та1шм образом, вычисление рассмотренных функций сводится к вычислению и: , произведениям П ISe NQ, siЫДЛЯ ОДНОЙ группы функций и, для другой группы функций. Вычисление пронаведения такого вида может быть заменено операциями сдвига и сложения реализуется в простых устройствах, например, использующих регистр-сдви гатель и сумматор. Логар.ифмирование тождества (4) -- яает, ,, для первоначального напряжения О 5 % N -x Qo ;X-iyi.e«g(4. 4оС-). 9 Число констант первого вида не превосходят (м + 1), число констант второ го вида - Хс,+ (), . Номер шага уравновешивания и результаты сравнени , , х; используются квк признаки адреса я чейки запоминающего устройств для хранения таблицы констант. Наличие в составе любого типового блока умножения сумматора позволяет осуществить суммирование констант при вьтчислении логарифма. Преобразователь напряжения в код работает в следующих режимах: 1) преобразование напряжения в код 2)образование кода, соответствующего обратным значениям преобразуемо напряжения и корня квадратного из него 3)образование кода -.отношения преобразуемых напряжений; 4)образование коца корня квадратно из преобразуемого напряжения; 5)образование кода логарифма преобразуемого напряжения. Перевод схемы преобразователя напряжения в код в один из режимов осуществляется по сигналам, поступающим на щину 19 цифрового входа преобразоЬателя напряжения в код. Этим режимам соответствуют управляющие сигналы СИ 1 - СИ на выходах распределителя сигналов 10, задающие последовательность работы во времени различн схем преобразователя. Операциям по уравновещивашпо преобразуемого напряжения предшествует нормирование, которое заключается в усилении напряжения U. так, чтобы обеспечить его нахождение в заданном диапазоне. По сигналу СИ1 ра спределителя сигналов 1О преобразуемое напряжение DX передается коммутатором на вход усилителей 1, 2 нормирования. Коэффициент усиления усилителей- 1,2 нормирования меняется как , где показатель х определяется по результатам сравнения усиленного преобразуемого напряжения . 2 ° , а эталонным напряжением UQ в блоке сравнения. Выбор оснований степени, равным 2, позволяет совместить этап нормирования с уравновешиванием для . так как для первого шага уравновешивания преобразуемое напряжение должно усиливат ся в 2 раз и сравниваться с эталонным напряжением. Кроме того, при тако основании упрощается определение кода для первоначального напряжения. Далее напряжение Uy преобразуется по известному алгоритму преобразования напряж;еш1я в код с умножением нескомпенс1фованного остатка напряжения в 2 раза. Если , то по сигналу, с выхода блока сравнешм 6 в момент прихода сигнала от распределителя сигналов 1О ключ ем 8 компенсирующее напряжение и (или ток Лц ) передается на вычитающий вход усилителя 3. Так как на его другом входе присутствует напряжение Uy , на выходе усилителя 3 образуется разность (W,-Uц ) 2. Ех:ли Uj( U(- , компенсирующее напряже- ime (или ток 3 не подается на вычитающий вход усилителя 3, в этом случае на его выходе присутствует удвоенное напряжение U . Напряжение с выхода усилителя 3 также поступает в блок сравнения 6 и по результату сравнения уравновешивается с использованием усилителя 4 и ключа 8 (в следующем . такте уравновешивания) усиллстеля 5 и соответствующего ключа 8. Результаты сравнения через узел управления 16 фиксируются в регистресдвигателе 14 блока ул ножения 12 и далее передаются в регистрирующее устройство 9 для представления по величине коэффихшента усиления усилителей 1,2 кода напряжения в требуемой форме. Образование код, соответствующего обратному значению преобразуемого напряжения, также начинается с операции нормироваьшя, которая вьтолняется в последовательности, описашюй выше. Коэффициенты усиления усилителей 3,4,5 устанавя}гваются по сигналам распределителя сигналов Ю соответственно (,(.(). Одновремеш1о в качестве исходной величины в регистр-сдвигатель 14 блока умножения 12 заносится едишша. с выхода усилителя 3 посту- . пает в блок сравнешм 6, где сравнивается с эталонным напряжешсем U. Если U (1+2)UQ,TO сигналу с выхода блока сравнения 6 в момент прихода очередного сигнала от распредетштеля сигналов 10 коэффициент у-силения усияитеяя 3 уменьшается до единицы. В ipOTHBHOM случае ( х 1), он со фаняется равным (1+2 ). Аналогично сравниваются с эталонным {апряжением напряжения с выходом усиштелей 4,5 и по результатам сравне 117X j(. корректируются их коэффициенты усиления. Одновременно с началом процесса кор рекции коэффициента усиления усилителя 3 сигиал Xj 1 с выхода блока сравHeifflH б поступает в блок умноже шя 12 В нем единица, зафиксированная в регистре сдвигателя 14, умножается на величину (1+2 ). Операция умножения выполняется как сложение содержимого регистра-сдвигателя 14 и его уменьшенногхэ в 2 раз значетшя. Содержимое регистра -сдвигателя 14 и его уменьшенное сдви)гутое вправо на один разряд значшия передаются на входы сумматора-15, который вьфабатьгоает их сумму. Полученный результат; по цепи с выхода . сумматора 15 на вход регистра-сдвигателя 14 фиксируется в нем и использует ся в качестве исходной величины для следующего вычисления кода. Еели результат сравнения х -О, содержимое регистра-сдвигателя 14 сохраняется неизменньпу. Аналогично выполняется вычислещ1е произведения на втором и третьем тактах уравновешивания. Так как шаги вычисления кода, выполняются одновременно с шагами уравновешивания формирование кода завершаетс с задержкой не превышающей длительности ОД1ЮГО шага вычисления кода после выполнения последнего шага уравновешивания. Образование кода обратной величины корня квадратного из преобразуемого напряже1шя вьшолняется по типу (jOpMHрования кода, соотве1ствующего обратной вели1ине преобразуемого напряжения нос использованием двойных шагов уси ления норм1фованного преобразуемого напряжения, Для этого коэффициента ус ления уси.пителей 3, 4, 5 устанавливаю ся (1-2-V (1+2); (1+2) ( 1+f); (Д.+2 )-(1+2), соответственно. Сравнение усиленного преобразуемого напряже ния с эталонным напряжением UQ и корректировка коэффициента усиления по результатам сравнения X. , х ъ полняется в той же последовательности которая была описана выше. Образовани кода в этом случае также вьшолняется вычкспением произведения .П. (1+2 ) в блоке 12 формироваъшя результата. Образование кода отношения двух напряжений U и U вьшолняется за два цикла уравновешивания - цикл обра зования прямого кода напряжения 1) и цикл образования кода обратного ве9ичине напряже1шя и , которые выполяются как было описано выше. После бразования кода напряжения U он иксируется в регистре-сдвигателя 14 и спользуется в качестве исходной велиины для следующего цикла. При уравноешивании напряжения U по типу образоания кода обратной величины преобразуеого напряжения в блоке y 1нoжe шя 12 о результатам сравнения , Q , уу силен1-юго напряжения UfJ и эталонного апряжения UQ вычисляется произведение -ЧУ.(.У .-) которое соответствует коду отношения апряжений и%и ч V образование кода корня квадратного из преобразуемого напряжения U выполняется за 2 шпша уравновешивания. Сначала находится код М , который сохраняется к началу следующего цикла в регистре-сдвигателе 14 блока умножения 12. Далее производится уравновешивание напряжения U по типу образова1шя кода, соответствующего величине обратно пропорциональной корню квадратному из преобразуемого напряжения с использова шем двойных шагов усиления преобразуемого напряжения U . При образовании кода логарифма преобразуемого напряже1шя одновремешю с нормированием и уравновешиванием по типу образования кода обратной величины напряжения по сигналам распределителя сигналов 10 происходит обращение к ячейкам запоминающего устройства 13, из которого последовательно извлекаются и передаются на входы сумматора 15 константы Xj,-6ogQ2 и 1+2. ), где они складываются для образования кода логарифма преобразуемого напряжения. Адреса запоминающего устройства 13 формируются по результатам сравне-. ния Xj и номеру такта уравновешиванияКоды. результатов функциональных преобразований также фиксируются в регистрирующем устройстве 9. При незначительном усложнении схемы усилителей 3, 4, 5 полная совокупность функциональных зависимостей может быть получена без использования пребеГразования напряжения в код по алгорут,у с умножением нескомпенсирован13кого остатка, натфимер, при роализацин усилителей 3, 4, 5 иа основе операщ offflbix усилителей с переметпгым коэффи циентом усиления. Для дво1лной систем счисления коэффициент усиления усилите лей ) обеспечивается соо ветствующим заданием номиналов резисторов Р во входной цепи ни. в цеп обратной связи усилителя. При ft R -9. ex ос Длях,-± 1 номиналы резисторов должны удовлетворять соотношению . R () .., Тогда при xNi .-) пРичЬЧ e,(. При уравновешивании напряжения по типу образования кода обратной величин преобразуемого напряжения по результатам сравнения 6 , х коммутир то ся резисторы с различными номиналал1И в цепи обратной связи операционного усилителя. При уравновешивании напряжения по Timy образования кода пропорционального преобразуемому напряжению коммутируются резисторы ко входно цепи операционного усилителя. При применении симметричной системы счислени на этапе уравновешивания (х, 1-1) двойные шаги уравновешивания позволяют сформировать код корня квадратного из преобразуемого напряжения за один цикл уравновешивания. Уравновешиваете преобразуемого напряжения со знакопеременными . обе печивается установлением коэффициентов усиления по результатам сравнения {1+2 ) или ( 1-2). В остальном работа преобразователя напряжения в код вьтолняется -в последовательности, рассмотренной выше. Быстродействие преобразователя напряже1шя в код повышается при примене нии систем счисления с ocHOBaHHOvi оС 2 с параллельно-последовательным уравновешиванием преобразуемого напряжения. Усилители 3,4,5 в этом случае могу быть вьтолнены, например, в виде групп усилителей с одинаковыми в пределах групп данного разряда коэффициентами усиления. Усилители в пределах группы ОС , 3914 датюго разряда соединяются гюследовательтю, выходы усилителей соединены с входами блока сравнещгя 6, а входы управления усилителей соединяются с выхода ч и блока сравнения 6. Преобразователь напряжения в код при о 4 работает следующим образом. Нормированное преобразуемое напряжение Uy передается в группу из трех усилителей первого разряда, входящих в состав усилителя 3, коэффициенты усиления которых одинаковы и равны (1- 4 ). Сигналы с выходов усилителей группы одновременно сравниваются в блоке сравнения О с эталонным напряжением Up . По результату сравнения {Х|/Х 0,1,2,3) корректируется коэф(1)ициент услчешся группы усилителей первого разряда, и усилешюе напряжение UQ , не превышаюшее эталонное нащэяжение, передается сначала в группу силителей след тошего разряда, а затем в группу усилителей младшего разряда, входяших в состав усилителей 4,5. Коэффишгент усиления усилителей в пределах этих групп составляет () и ( 174 ), соотвотстветю. Далее вьтолняется сравнение усиленного прсюбразуемого напряжешш с выходов усилителей группы с эталонным напр5гже1шем UQ в блоке сравнения 6 и коррекция по результатам сравнения X , X,, коэффициентов усиления усилителей групп. Одновремеггао с уравновеш1шанием преобразуемого напряжения в блоке умножения 12 происходит образование кода, связанного определенной функциональной зависимостью с преобразуемым напряжением. Образование кода в блоке умножения 12 происходит аналогично как в рассмотрешюм варианте вьшолнения преобразователя напряжения в код, но с числом одинаковых шагов вычисления кода на каждом шага X , Таким образом, предлагаемый преоб- разователь напряжения в код наряду с образованиек кода преобразуемого напряжения вырабатывает коды, связанные значительньЛ числом функциональных ависимостей с преобразуемым напряжеием. В отличие от известных логарифических преобразователей напряжения код-Б предлагаемом устройстве логаифм напряже1шя образуется по произвольому основашпо, пр1гчем смена основания ьтолняется просто - записи в апоминающее устройство нового набора 15 констант. Это дополнительно расширяет его футпощональные возможности. Указанный эффект получен при незна чительном увеличении схемных затрат вследствие использования единого алгоритма уравновешивания при образовании всех функциональ11ых зависимостей, упрощенного алгоритма формирования кода и небольшой емкости запоминающего устройства. При применении систем счисления с укрупненным ocHOBainravt преобразовател напряжения в код имеет более высокое быстродействие при вьшолнении функцио нальных преобразований, чем известные преобразователи напрян ения в код. Формула изобретени Преобразователь напряже шя в код, содержащий соединенные поеледовательно усилители, блок сравнения, источник эталонного напряжения (токов), ключи, регистрирующее устройство и распределитель сигналов, блок сравнения соединен первой группой входов с вьпоэдами усилителей, вторым входом - с выходом источника эталонного напряжения (токов), третьим входом - с выходом распределителя сигналов, выходы блока сравнения соединены с первь1ми входами усилителей и ключей, вторые входы которых соединены с выходами распределителя сигналов,регистрируют е устройство соединено с распределителем сигналов, отличающийся тем 916 что, с целью расиофения функциональных возможностей, в него введены коммутатор, блок умножения, вьтолненньтй из регистра-сдвигателя, сумматора и узла управления, и запоминающее устройство, причем входы коммутатора соеди.нены с входными клеммами устройства и с выходом распределителя сигнала, вызоэд коммутатора соединен с вторым входом первого усилителя, третьи входы последних усилителей через ключи соединены с выходами источника эталотгаого напряжения (токов), первые входы узла управления и запоминающего устройства обединень с выходом блока сравнения, вторые входы узла управления и запоминающего устройства соединены с распределителем сигналов, входы регистра сдвигателя соединены с вы.ходами узла управления и выходами сумматора, вяоды которого соединены с выходами регистра-сдвигателя и запоминающего устройства, входы регистрирующего устройства соединены с выходами узла управления и регистра-сдвигателя, вход распределителя сигналов соединен с щ.шгой цифрового входа преобразователя напряжения в код. Источники п фЬрмаш1и, принятые во внимание при экспертизе 1.ПолупрОЕюдниковые кодирующие и декодируюцие преобразователи под ред. IB. Б. Смолов а. Л., Энергия, 1967, с. 14,1. 2.Патент Австрии № 251319, кл. 42 , 14.03.71 (прототип).

IZZZli

Авторы

Даты

1980-04-25—Публикация

1975-08-18—Подача