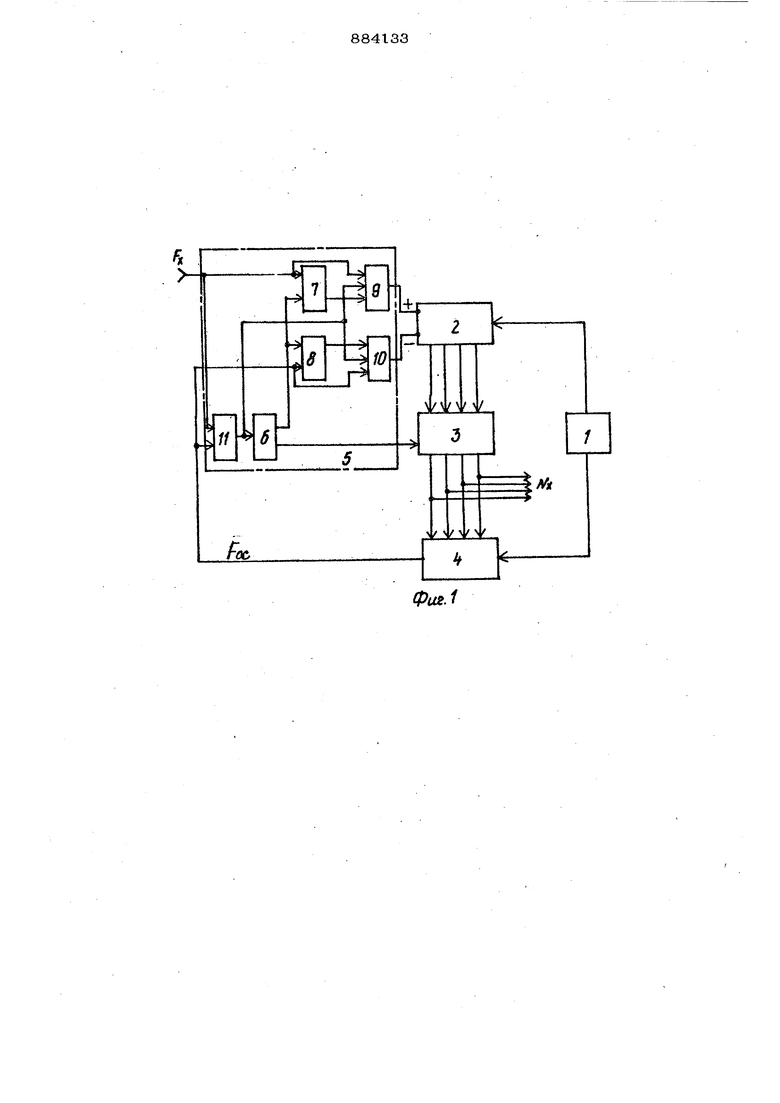

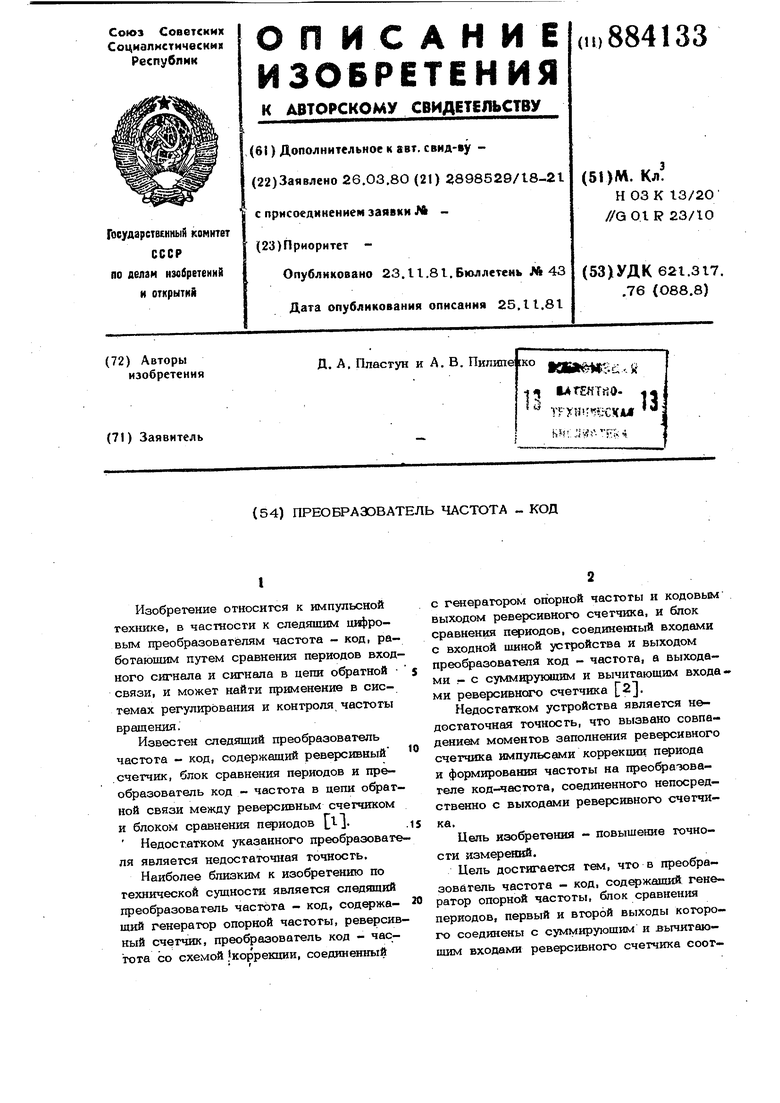

Изобретение относится к импульсной , в частности к следящим цифровым преобразователям частота - код, ра ботающим путем сравнения периодов вход ного сигнала и сигнала в цепи обратной связи, и может найти применение в системах регулирования и контроля частоты вращения. Известен следящий преобразователь частота - код, содержащий реверсивный счетчик, блок сравнения периодов и преобразователь код - частота в цепи обрат ной связи между реверсивным счетчиком и блоком сравнения периодов Недостатком указанного преобразовате ля является недостаточная точность. Наиболее близким к изобретению по технической сущности является следящий преобразователь частота - код, содержащий генератор опорной частоты, реверсив ный счетчик, преобразователь код - частота со схемой коррекции, соединенный с генератором опорной частоты и кодовым выходом реверсивного счетчика, и блок сравнения периодов, соединенный входами с входной шиной устройства и выходом преобразователя код - частота, а выходами .- с суммирующим и вычитающим входами реверсивного счетчика 2. Недостатком устройства является н достаточная точность, что вызвано совпадением моментов заполнения реверсивного счетчика импульсами коррекции периода и формирования частоты на преобразователе код-частота, соединенного непосредственно с выходами реверсивного счетчика. Цель изобретения - повышение точности измерений. Цель достигается тем, что в преобразователь частота - код, содержащий генератор опорной частоты, блок сравнения периодов, первый и второй выходы котороо соединены с суммирующим и вычитающим входами реверсивного счетчика соот3. 8 ветственно, преобразователь кода в часгогу, выход которого совпадает с первьлм входом блока сравнения периодов, второй вход которого подключен к входной шине устройства, введей регистр памяти, кодовые входы которого соединены с выходами разрядов реверсивного счетчика, васод записи регистра памяти подключен к третьему выходу блока сравнения периодов, первый и второй выходы которого соединены со счетным входом реверсивного счетчика и входом преобразователя кода в частоту, кодовые входы которого соединены с выходами разрядов регистра памяти и выходными шинами устройства, а кроме того, блок сравнения периодов содержит формирователь импульсов, элемент И-НЕ, два триг гера и два элемента И, причем первым входом блока сравнения периодов является первый вход элемента И-НЕ, соединенный с первыми входами первого триггера и первого элемента И, выхоц которого является вторым выходом блока сравнения периодов, вторым входом которого является второй вход элемента ИНЕ, соединенный с первыми входами второго триггера и второго элемента И, выход которого подключен к первому выходу блока сравнения периодов, выход элемента И-НЕ соединен со вторыми входами элементов И и со входом формирователя импульсов, первый выход которого является третьим выходом блока сравнения периодов, а второй выход подключен к вторым входам триггеров, выход каждого из которых подключен к третьему входу соответствукидего элеменга И. На фиг. I представлена блок-схема преофазователя; на фиг. 2 - временные диаграммы работы устройства. Устройство содержит I опо ной частоты, реверсивный счетчик 2, сое диненный счетным входом с выходом генератора, регистр 3 памяти, соединенный кодовыми входами с выходами разрядов счетчика 2, преобразователь 4 кода в частоту, соединенный с регистром 3 и выходными шинами устройства, а импуль ным входом - с генератором t, блок 5 срешнения периодов, включающий в себя формирователь 6 импульсов, RS-rpurre ры 7 и 8 и трехвходовые элементы 9 и Ю И, соединенные входами с входной шиной устройства и выходом преобразо3вателя 4 кода в частоту, а выходами с шинами сложения и вычитания счетчика 2, элемент 11 И-НЕ. Работа устройства заключается в следующем. Входная И1 а1ульсная последовательность полупериоДных импульсов частоты FX/ которую необходимо преобразовать в код, поступает на первые входы элемента 11 и триггера 7 блока 5 сравнения периодов. На второй вход элемента 11 и тригг а 8 поступают полупериодные импульсы Р QC с преобразователя 4, Указанные импульсные последовательности с частотами F)( и РОС представлены на фиг. 2 б, в. На фиг. 2, г представлены импульсы, сформированные на выходе зпемента 11. По переднему и заднему фронтам этих импульсов формирователем 6 формируется коротких импульсов (фиг. 2д, е). Импульсы, сформ1фованные по переднему фронту на втором выходе формирователя устанавливают триггеры 7 и 8 в исходное состояние, а сформированные по заднему фронту - производят перепись кода со счетчика 2 в регистр 3, Состояния триггеров 7 и 8 показаны на фиг. 2 ж, 3. Исходные положения триг;геров заштрихованы. Переключение триггеров 7 и 8 производится задними фронтами импульсов соответствующих последовательностей Pj и РОС На входах элементов 9 и 10, таким образом, присутствуют сигналы с выхода элемента II, входных сигналов FC и FOC и сигналы с выходов триггеров 7 и 8. В зависимости от соотношения частот Р X и Р Q на входах счетчика 2 происходит пфиодическое суммирование и вычитание импульсов представленных на фиг. 2 и, к. При равенстве входных частот F ;( и f Q(. , соответствующих установлению кода частоты, количество импульсов накопленных по шинам сумм1фования и вычитания счетчика 2 равны между собой.. Код, зафикс1фованный в конце суммирования регистром памяти 3, записан вторыми импульсами (фиг. 2д, е) со счетчика 2 (фиг. 2л). При рав«1стве частот код на выходе регистра памяти 3 изменяться не будет. Нарушение равенства входных частот РХ и FOC вызывает неравенство числа импульсов накапливаемых за период входной частхзты на входах счегчика 2 (фиг. 2 л). При этом измекяегся результирующий код на выходе регистра 3 (фиг. 2г). Код, неизменный в течение периода входного сигнала, с выхода регистра 3 поступает на преофазователь 4 кода в частоту в цепи обратной связи и на выход устройства., Таким образом, буфферное включение регистра памяти между реверсивным сче чиком и преофазоватепем код частота с управлении его записи с блока сравнения периодов в моменты отсутствия накопления импульсов на реверсивном счетчике повышает точность формирования кода - частоты, такое выполнение блока сравнения гюзволяет устранить несимметричность характеристик устройства при разном соотношении частот (при РОС)- fo позволяет повысить частоту фо{Му«1ровашга сиг налов коррекшш блоком сравнения периодов при превышении частоты входнохчз сигнала F-y по сравнению с частотой цепи обратной связи FOC и тем самым повысить динамическую точность устройства. Формула изобретения I. Преобразователь частота- код, содержащий г ератор опорной частоты, бло сравнения периодов, первый и второй выходы которого соединены с суммирующим и вычитающим входами реверсивного сче чика соответственно, преобразовагет кода в частоту, выход которого соединен с первым входом блока сравнения периодов, второй вход которого подключен к входной шине устройства, о т п и ч а юш и и с я . тем, что, с цепью повышения точности измерений в него введен регистр памяти, кодовые входы которого соединены с выходами разрядов реверсивного счетчика, вход записи регистра памяти подключен к третьему выходу блока сравнения периодов, первый и второй выходы которого соединены со счетным входом реверсивного счетчика и входом преобразователя кода в частоту, кодовые входы которого соединены с выходами разрядов p mcipa памяти и выходными шинами устройства, 2. Преобразователь частота - код по п. 1, отличающийся тем, что блок сравнения периодов содержит формирователь импульсов, эпемент И-НЕ, два триггера и два элемента И, фичем первым входом блока сравнения периодов является первый вход элемента И-НЕ, соединенный с первыми входами первого триггера и первого элемента И, выход которого является вторым выходом блока сравнения периодов, вторым входом которого является второй вход элемента И-НЕ, соединенный с первыми входами второго триггера и второго элемента И, выход которого подключен к первому выходу блока сравнения периодов, выход элемента И-НЕ соединен со вторыми входами элементов И и со входом формирователя импульсов, первый выход которого является третьим выходом блока сравнения периодов, а второй выход подключен к вторым входам тригг ов, выход KaifQioro из которых подключен к третьему входу соответствующего элемента И. Источ11вки инфсфмашш, пр1гаятые во внимание при экспертизе .1- Авторское свидетельство СССР № 443482, кл. Н ОЗ К 13/20, 1974. 2. Авторское свидетельство СССР № 445148, кл. Н ОЗ К 13/2О, 1972 (прототип).

Фаг.1

4J %J « 14 -tj ,

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для определения знакапЕРВОй пРОизВОдНОй | 1979 |

|

SU834713A1 |

| Следящий преобразователь периода следования импульсов в код | 1978 |

|

SU871095A1 |

| Устройство для измерения среднеквадратического значения сигнала | 1989 |

|

SU1728808A1 |

| Устройство для телеизмерения давления скважинных штанговых насосов | 1990 |

|

SU1711218A1 |

| Устройство для анализа логических состояний | 1980 |

|

SU1096648A1 |

| Преобразователь угла поворота вала в код | 1986 |

|

SU1387198A1 |

| Устройство для программного счета изделий | 1983 |

|

SU1113824A1 |

| Устройство для коррекции нелинейности | 1982 |

|

SU1056228A1 |

| Устройство для измерения искажения длительности импульсов | 1988 |

|

SU1559327A1 |

| Частотный детектор | 1982 |

|

SU1137563A1 |

4 « e;

H a X

Авторы

Даты

1981-11-23—Публикация

1980-03-26—Подача