СО

С

| название | год | авторы | номер документа |

|---|---|---|---|

| Измерительный прибор | 1989 |

|

SU1661653A1 |

| Цифровой измеритель центра тяжести видеосигналов | 1990 |

|

SU1723559A1 |

| Устройство для ретрансляции речевых сигналов | 1990 |

|

SU1830627A1 |

| Устройство для измерения среднеквадратического значения сигнала | 1990 |

|

SU1781625A1 |

| МНОГОКАНАЛЬНАЯ СИСТЕМА ДЛЯ РЕГИСТРАЦИИ ФИЗИЧЕСКИХ ВЕЛИЧИН | 1991 |

|

RU2037190C1 |

| ЛОГИЧЕСКИЙ ПРОБНИК | 1991 |

|

RU2041473C1 |

| Способ измерения среднеквадратических значений переменных сигналов | 1990 |

|

SU1798705A1 |

| СПОСОБ И УСТРОЙСТВО РАСПОЗНАВАНИЯ КЛАССОВ СИГНАЛОВ | 1998 |

|

RU2133501C1 |

| Буферное динамическое оперативное запоминающее устройство | 1989 |

|

SU1695388A1 |

| УСТРОЙСТВО ФОРМИРОВАНИЯ СЛОЖНЫХ СИГНАЛОВ | 1988 |

|

SU1841042A1 |

Изобретение касается области электрических измерений и позволяет проводить высокоточные измерения в широком частотном диапазоне переменных сигналов произвольной формы. Высокая точность измерения достигается за счет устранения частотной составляющей погрешности, что достигается изменением спектра входного сигнала его двойным преобразованием (аналого-цифровым и цифроаналоговым). В результате этих преобразований измеряемый сигнал изменяется в узком фиксированном частотном диапазоне. 5 ил.

Изобретение относится к электрическим измерениям и может быть использовано при построении высокоточных измерительных приборов.

Известно устройство для измерения среднеквадратического значения сигнала, которое состоит из управляющего устройства, электронного ключа, генератора импульсов, источника компенсирующего напряжения, счетчика импульсов, дешифратора, регистрирующего устройства, нуль- органа, управляемого делителя и программирующего блока. В данном устройстве переменное входное напряжение предварительно преобразовывается в постоянное, а затем производится его измерение. Для преобразования переменного напряжения в постоянное применен преобразователь средних значений.

Постоянное напряжение измеряется следующим образом. При поступлении пускового импульса от управляющего устройства открывается электронный ключ и к источнику компенсирующего напряжения поступают сигналы генератора импульсов, которые одновременно фиксируются счетчиком импульсов. Источник компенсирующего напряжения вырабатывает компенсирующее напряжение Ux, изменяющееся на Д Ux с приходом каждого импульса от генератора импульсов. Процесс измерения сводится к подсчету счетчиком числа импульсов, прошедших через электронный ключ за определенное время. При срабатывании нуль-органа, когда преобразованное в постоянное переменное входное напряжение Ux, поступающее на нуль-орган через управляемый делитель, станет равным компенсирующему напряжению Ux. ключ закроXJ

Ю 00 00 О 00

ется, генерирование Ли и счет импульсов прекратится, показания счетчика импульсов после дешифрации передаются на регистрирующее устройство.

Недостатком данного устройства измерения среднеквадратического значения сигнала является низкая точность измерения. Это обусловлено тем, что применяемый в устройстве преобразователь переменного напряжения в постоянное не предназначен для преобразования сигналов произвольной формы.

Наиболее близким по технической сущности яляется вольтметр средне- квадратических значений, состоящий из последовательно соединенных полупроводникового измерительного выпрямителя, усилителя и регистрирующего устройства. Преобразование переменного сигнала в постоянный, пропорциональный среднеквад- ратическому значению переменного сигнала, производится измерительным выпрямителем. В измерительном выпрямителе среднеквадратических значений используются близкие к квадратичным участки вольт-амперной характеристики выпрямительных элементов (диодов). Участки эти ограничены небольшими пределами изменения напряжения. Для расширения динамического диапазона входного сигнала создают искусственные цепи с несколькими определенным образом подобранным диодами и резисторами. Такие цепи имеют уравнение преобразования Y КХ , где-Х. Y - соответственно входная и выходная величины напряжения.

Недостатком известного устройства измерения среднеквадратического значения сигнала является низкая точность измерения (1-2 % ). Это обусловлено частотной погрешностью диодов преобразователя среднеквадратических значений. Диоды обладают собственной емкостью, которая определяет их частотные свойства. Эта емкость шунтирует активное сопротивление диода и поэтому с увеличением частоты входного сигнала растет обратный ток диода, что приводит к падению коэффициента передачи измерительного выпрямителя.

Цель изобретения - повышение точности результата измерения среднеквэдрати- ческого значения сигнала.

Поставленная цель достигается тем. что в устройство для измерения среднеквадратического значения сигнала, содержащее формирователь измеряемого сигнала, подсоединенный входом к входной шине, фор- мирователь среднеквадратического значения сигнала,выход которого соединен через усилитель с входом блока регистрации, формирователь управляющих сигналов и формирователь импульсов, дополнительно введены первый регистр и дешифратор, подсоединенные входами соответственно к

первому и второму выходам формирователя управляющих сигналов, счетчик, соединенный нулевым входом и входом разрешения соответственно с третьим и четвертым выходами формирователя управляющих сиг0 налов, второй регистр: подсоединенный управляющим входом к пятому выходу формирователя управляющих сигналов, первый и второй элементы И, соединенные первыми входами с шестым выходом фор5 мирователя управляющих сигналов, аналого-цифровой преобразователь, подсоединенный запускающим входом к седьмому выходу формирователя управляющих сигналов, счетчик адреса, соединенный ну0 левым входом с восьмым выходом формирователя управляющих сигналов, первый триггер, подсоединенный счетным входом к девятому выходу формирователя управляющих сигналов, формирователь интервала за5 писи, соединенный входом и выходом соответственно с десятым выходом и первым входом формирователя управляющих сигналов, формирователь импульсов перехода через нуль, включенный между выхо0 дом формирователя измеряемого сигнала и вторым входом формирователя управляющих сигналов, первый и второй реверсивные счетчики, подсоединенные нулевыми входами к выходу формирователя импуль5 сов, цифроаналоговый преобразователь, подключенный выходом к входу формирователя среднеквадратического значения, формирователь сигнала считывания, третий регистр, второй триггер, подключенный вы0 ходом к входу формирователя импульсов, третий триггер, первый и второй элементы задержки, третий и четвертый элементы И, первая, вторая, третья, четвертая и пятая группы элементов 2-2И-2ИЛИ, первая и вто5 рая группы элементов И, первый и второй блоки памяти, делитель частоты, генератор импульсов и элементы ИЛИ, причем формирователь управляющих сигналов подключен пятым и седьмым выходами соответственно

0 к первому входу второго триггера и к счетному входу счетчика адреса, соединенного выходами с первыми группами входов первой и второй групп элементов 2-2И-2ИЛИ и с информационными входами второго реги5 стра, выходы которого подключены к группе входов третьей группы элементов 2-2И- 2ИЛИ, подсоединенных входом к выходу первого элемента задержки и соединенных выходами с информационными входами первого реверсивного счетчика, выходы коорого подключены к группе входов третьего элемента И и к первой группе входов етвертой группы элементов 2-2И-2ИЛИ, подсоединенной первым входом к первому выходу третьего триггера, подключенному к входу реверса первого реверсивного счетика, подсоединенного счетным входом к первому выходу делителя частоты, соединенному с первым входом формирователя сигналов считывания, с входом второго элемента задержки и со счетным входом второго реверсивного счетчика, подключенного выходами к группе входов четвертого элемента И и к второй группе входов четвертой группы элементов 2-2И-2ИЛИ, второй вход которого подсоединен к второму выходу ретьего триггера, соединенному с входом реверса второго реверсивного счетчика, формирователь сигналов считывания подключен первым, вторым и третьим выходами соответственно к входу третьего регистра и к входам считывания первого и второго блоков памяти, соединен четверым и пятым выходами с первым и вторым входами первой группы элементов 2-2И- 2ИЛИ, подключен шестым и седьмым выходами к первому и второму входам второй группы элементов 2-2И-2ИЛИ, соединен восьмым и девятым выходами с первым и вторым входами пятой группы элементов 2-2И-2ИЛИ и подсоединен вторым входом к первому выходу первого триггера, соединенному с входом первой группы элементов И, с вторым входом первого элемента И. подключенного выходом к входу записи первого блока памяти, который подсоединен адресными входами к выходам первой группы элементов 2-2И-2ИЛИ и соединен информационными входами с выходом первой группы элементов И, подсоединенной группой входов к выходам аналого-цифрового преобразователя, подключенным к группе входов второй группы элементов И, соединенного выходами с информационными входами второго блока памяти, который соединен адресными входами с выходами второй группы элементов 2-2И-2ИЛИ и подсоединен входом записи к выходу второго элемента И, соединенного вторым входом с вторым выходом первого триггера, подключенным к второму входу второй группы эле- ментов И, вход цифроаналогового преобразователя подсоединен к выходу третьего регистра, соединенного информационными входами с выходами пятой группы элементов 2-2И-21/1ЛИ, подсоединенной первой и второй группами входов к выходам соответственно первого и второго блоков памяти, выход второго элемента задержки одключен к входу третьего элемента И и к

входу четвертого элемента И, соединенного выходом с вторым входом второго триггера и с первым входом элемента ИЛИ, который подсоединен вторым входом к выхо дутретьего элемента И и подключен выходом к счетному входу третьего триггера, соединенного нулевым входом с выходом формирователя импульсов, а выход формирователя измеряемого сигнала соединен с измерительным

входом аналого-цифрового преобразователя, подсоединенного тактовым входом к второму выходу делителя частоты, который соединен входом с выходом генератора импульсов, подключен третьим выходом к

счетному входу счетчика и соединен группой выходов с первой группой входов формирователя интервала записи, подсоединенного второй группой входов к выходам первого регистра, соединенного группой входов с

выходами дешифратора, группа входов которого подсоединена к выходам счетчика.

Повышение точности результата измерения среднеквадратических значений сигнала обусловлено тем, что спектр

переменного входного сигнала изменяется в широком частотном диапазоне, переносится на узкий диапазон, в котором частотная погрешность преобразователя среднеквадратических значений сводится к

минимуму и не превышает 0,1 %.

С этой целью на выбранном интервале измерения проводится двойное аналого- цифровое и цифроаналоговое преобразование входного переменного, сигнала. В

зависимости от частоты входного сигнала выбирается поддиапазон измерения, в котором число выборок мгновенных значений входного сигнала одинаково с фиксированным интервалом между ними. Восстановление входного сигнала (обратное цифроаналоговое преобразование) проводится с фиксированым интервалом ДТв между выборками. Поскольку кодирование мгновенных значений входного сигнала в

каждом поддиапазоне проводится через равные промежутки времени ATi, то число выборок при восстановлении будет изменяться отщ до П2, где и П2 число выборок за период входного сигнала в начале и в

конце поддиапазона. Поэтому частота восстановленного переменного входного сигнала, изменяющегося в широком частотном диапазоне, будет изменяться в узком фиксированном диапазоне от fi до f2.

Для переноса спектра измеряемого сигнала в устройство для измерения средне- квадратического значения сигнала вводятся аналого-цифровой и цифроаналоговые преобразователи, блоки памяти, группы элементов И, группы элементов 2-2И-2ИЛИ, логические элементы И, ИЛИ, формирователь сигналов считывания, реверсивные счетчики, формирователь импульсов, регистры, элементы задержки, счетчики, триггеры.

Управляющие сигналы, необходимые для преобразования спектра измеряемого сигнала в узкий фиксированный диапазон, формируются формирователем управляющих сигналов, формирователем импульсов перехода через нуль, генератором импульсов, делителем, счетчиком, дешифратором, формирователем интервала записи.

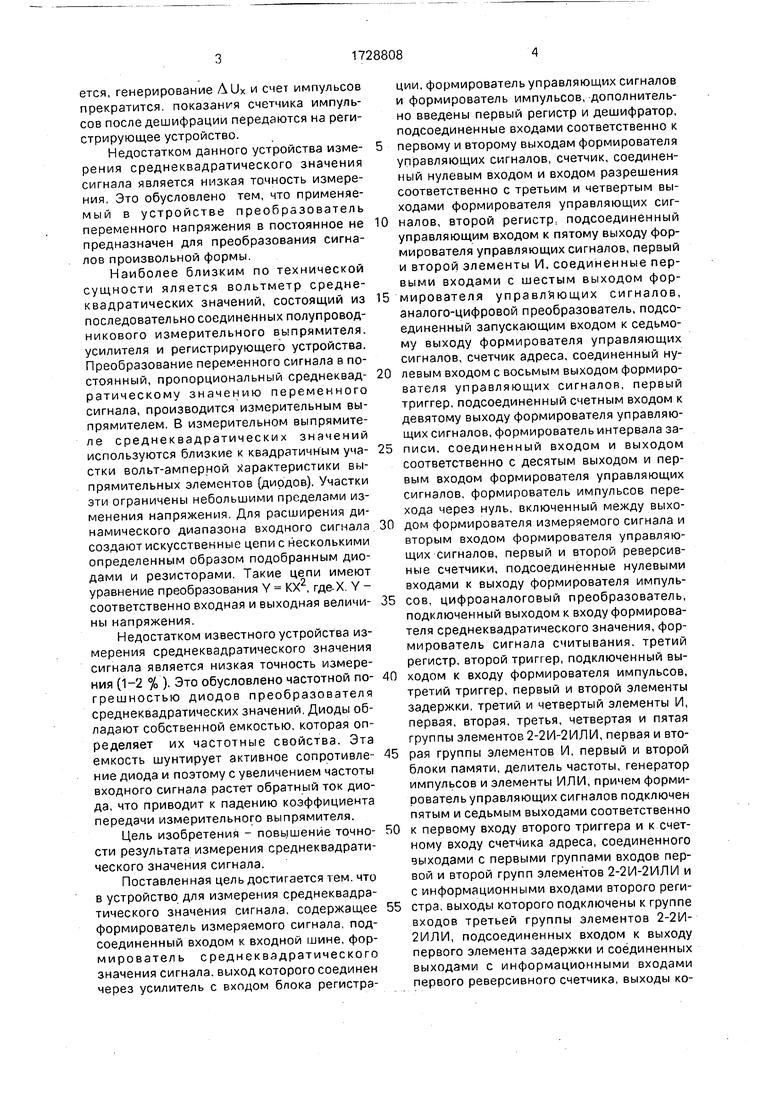

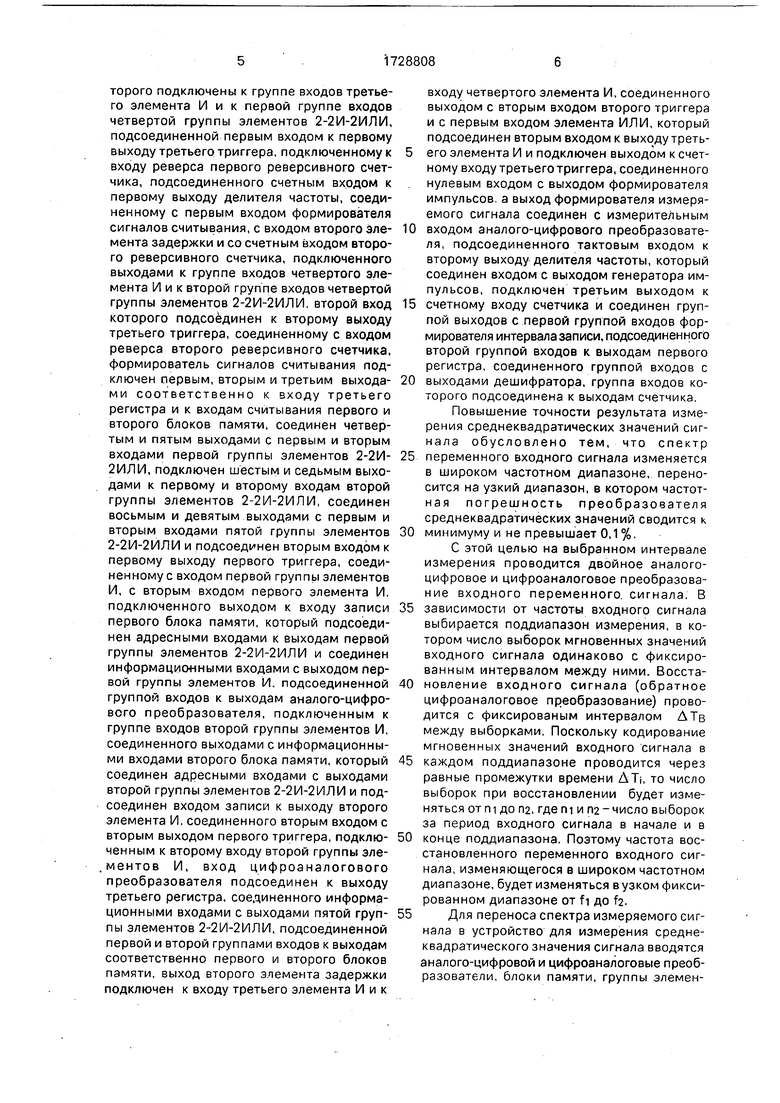

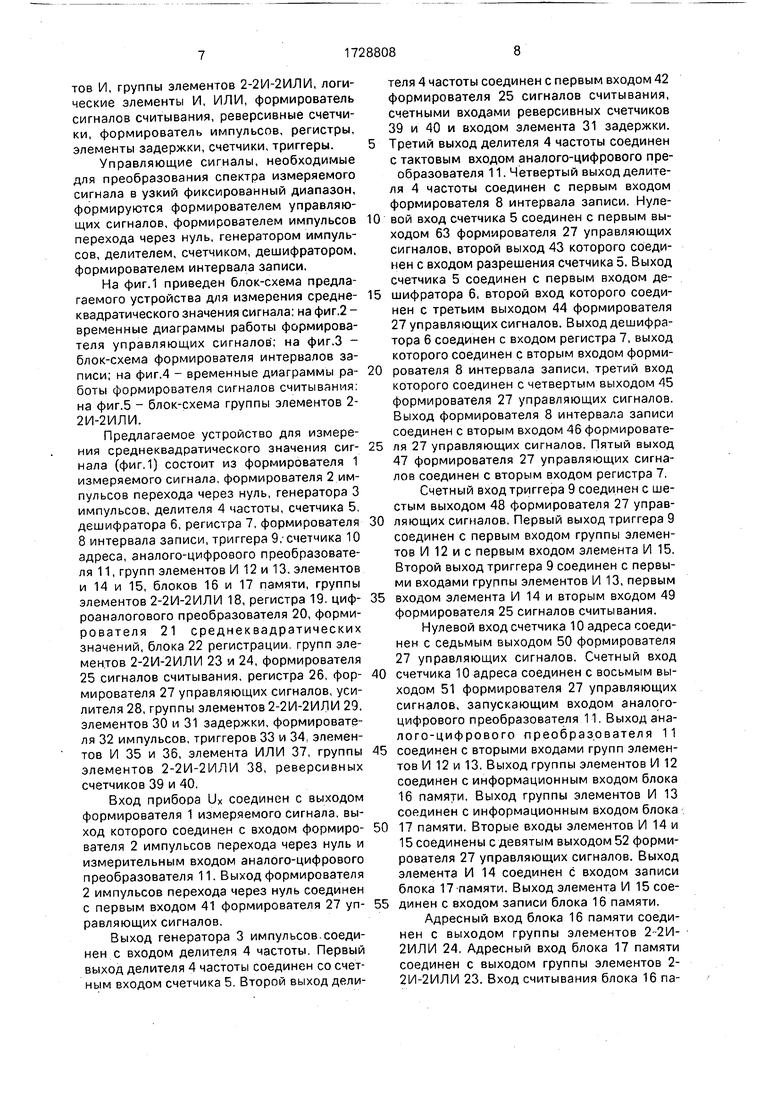

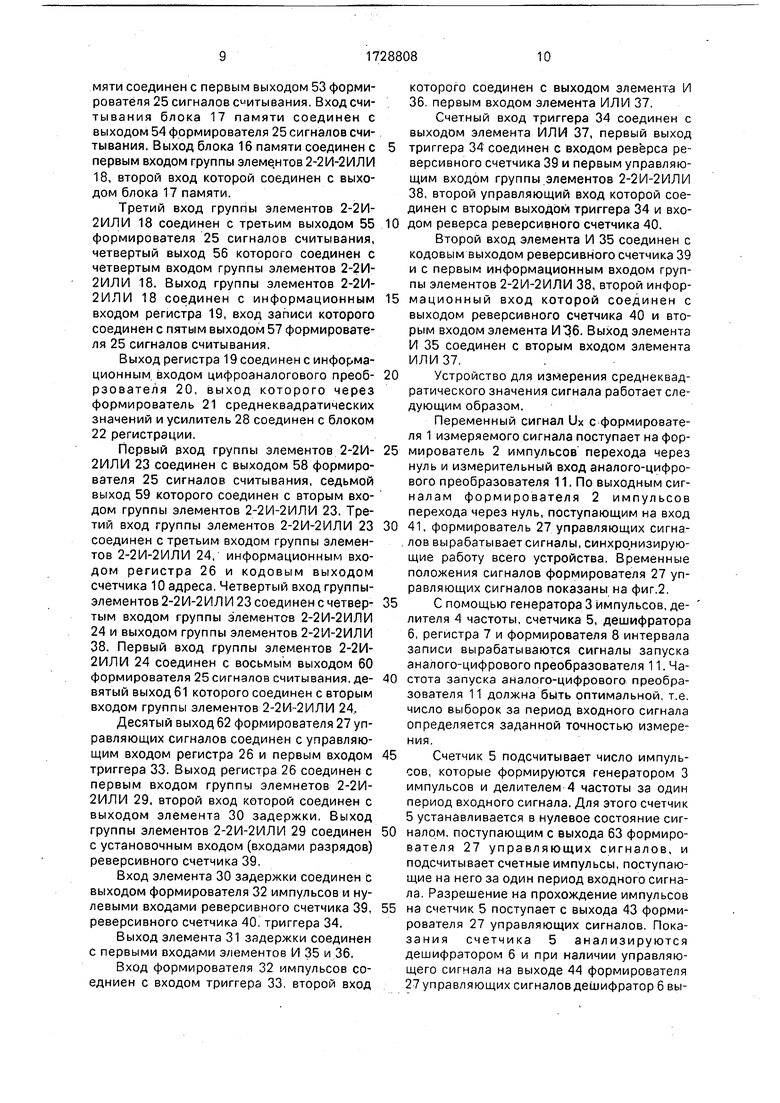

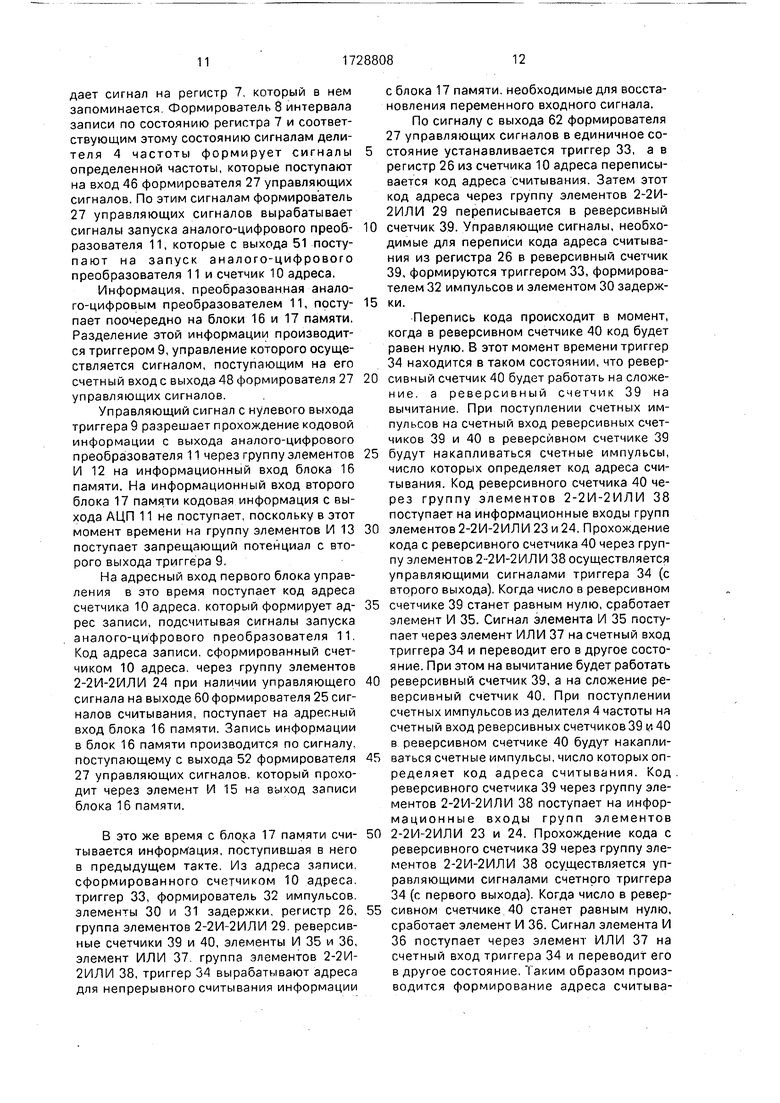

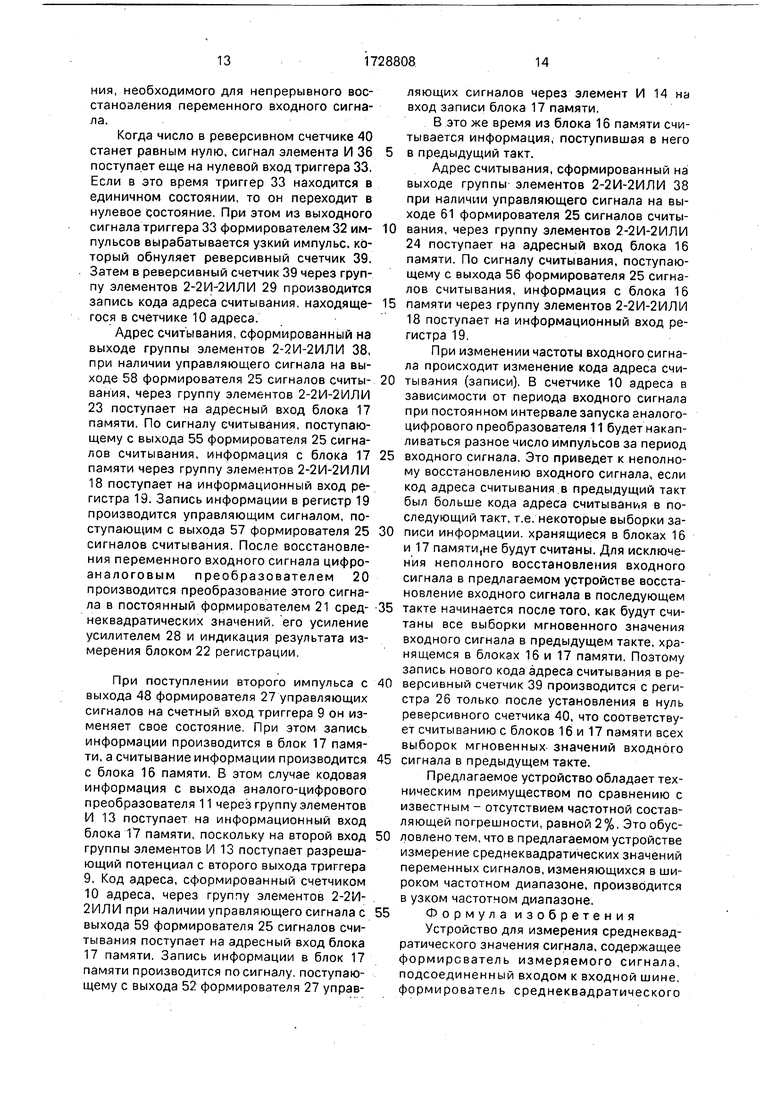

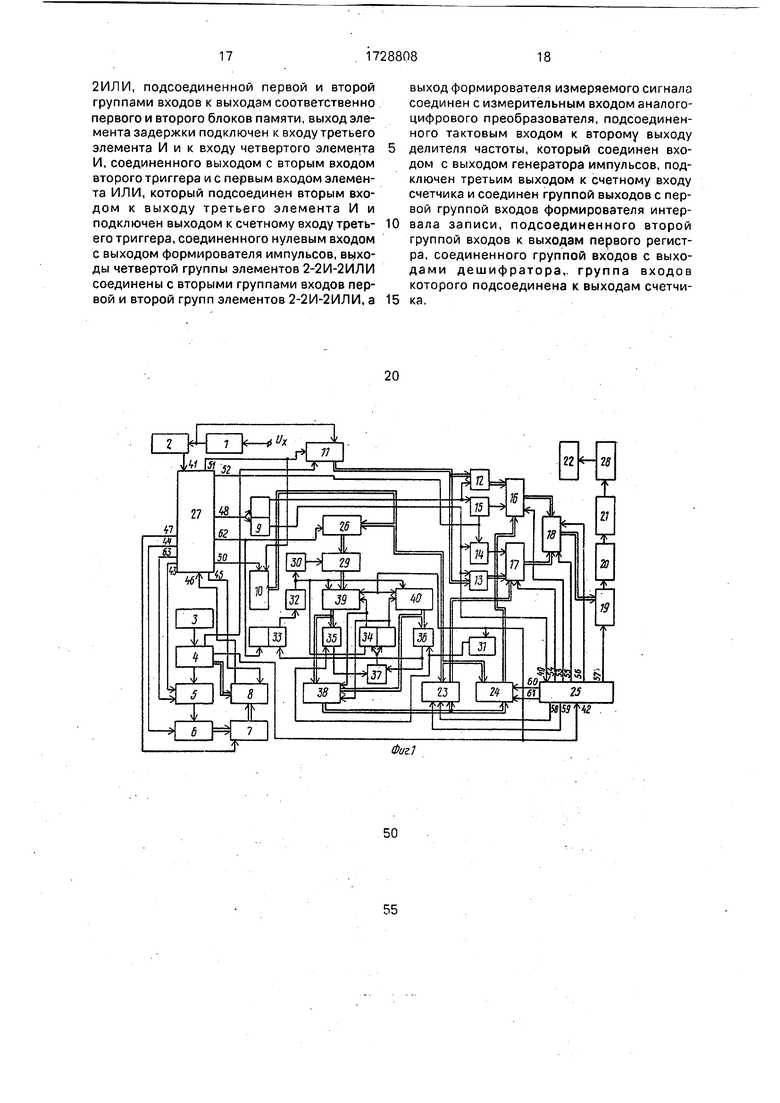

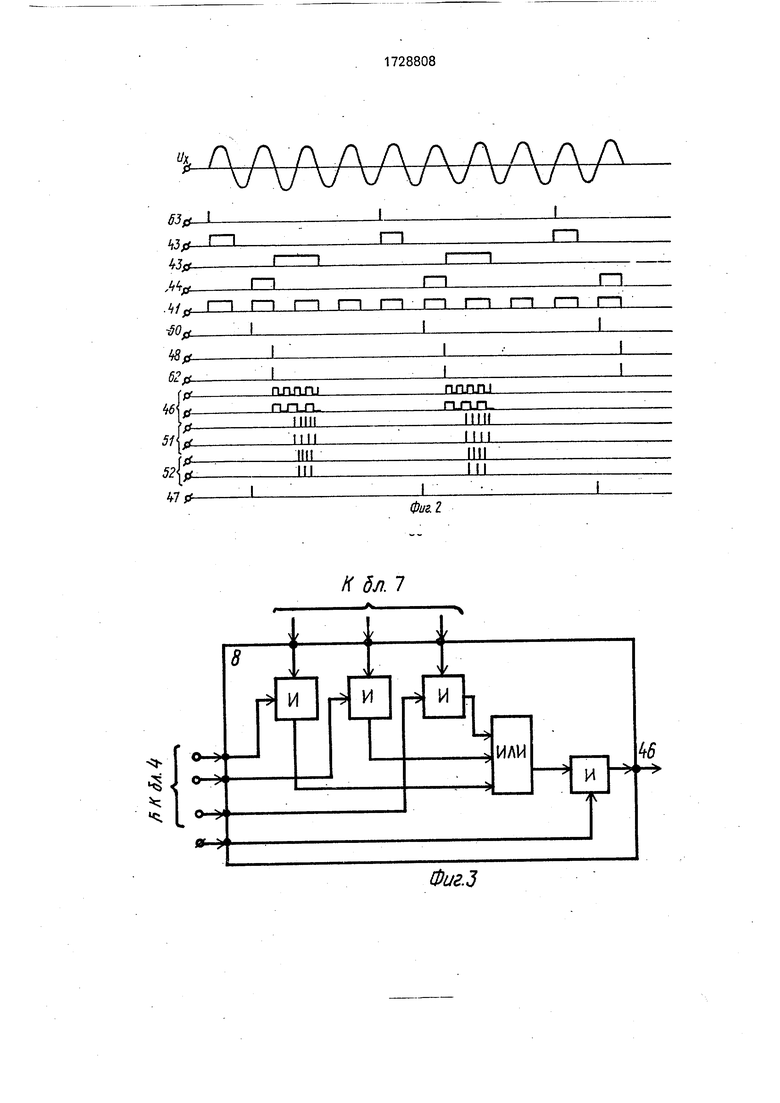

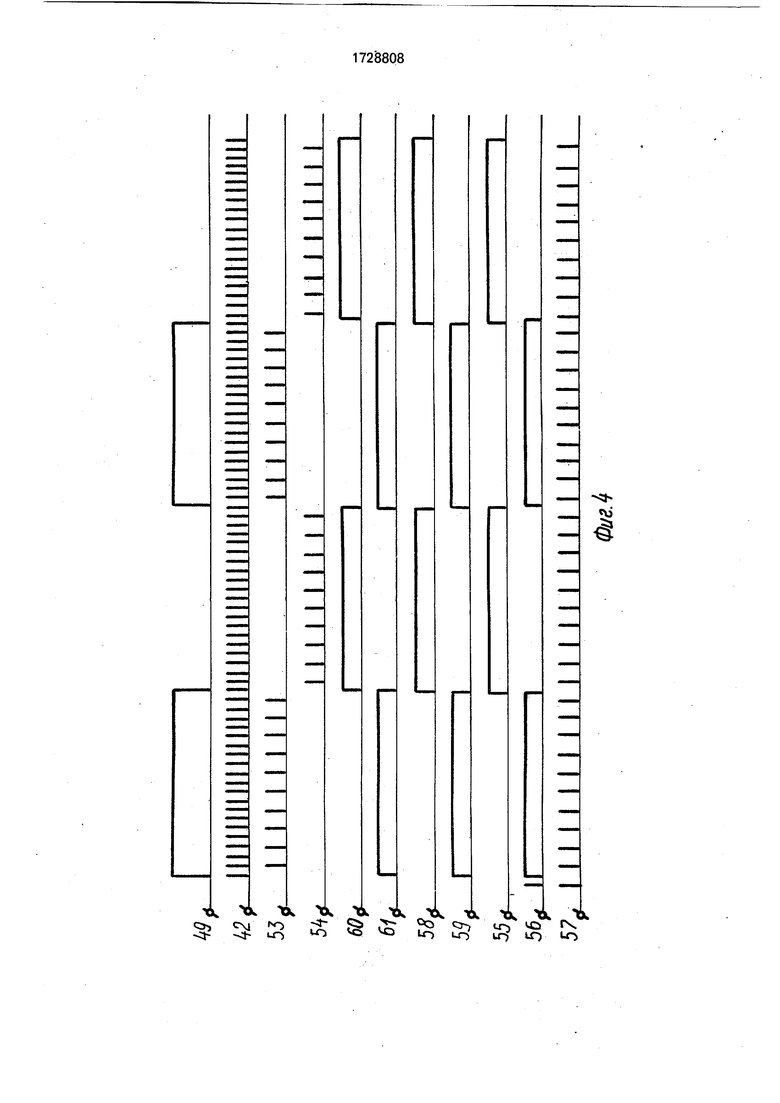

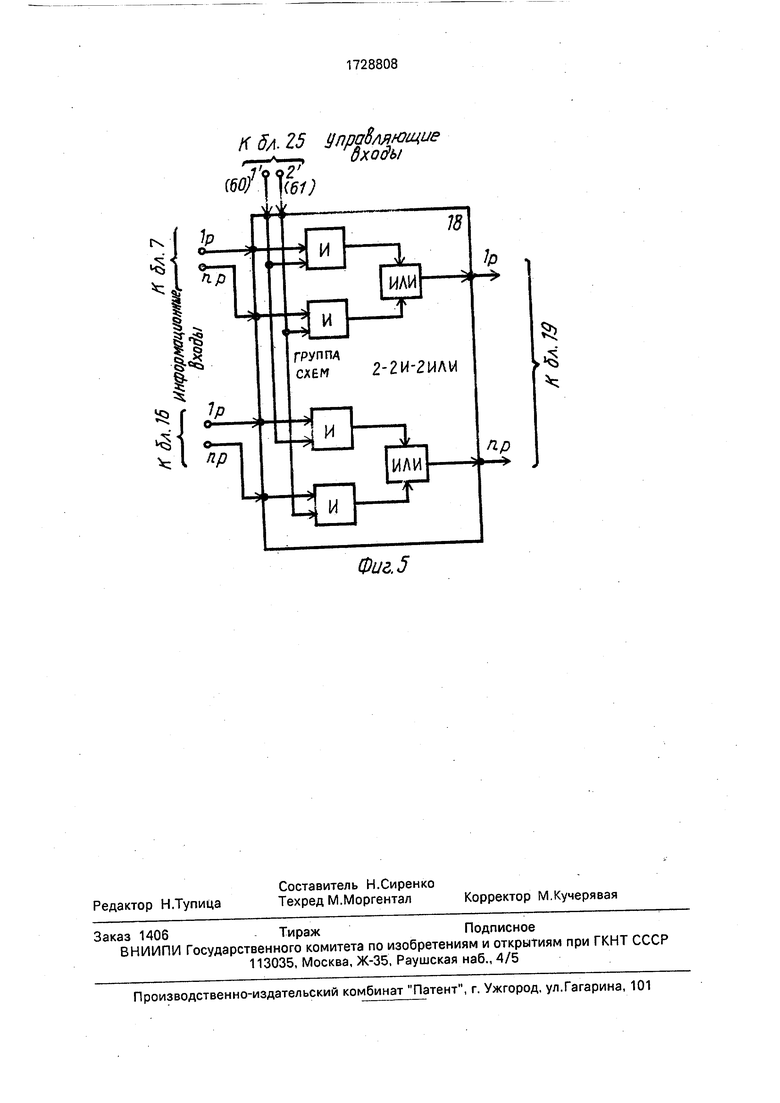

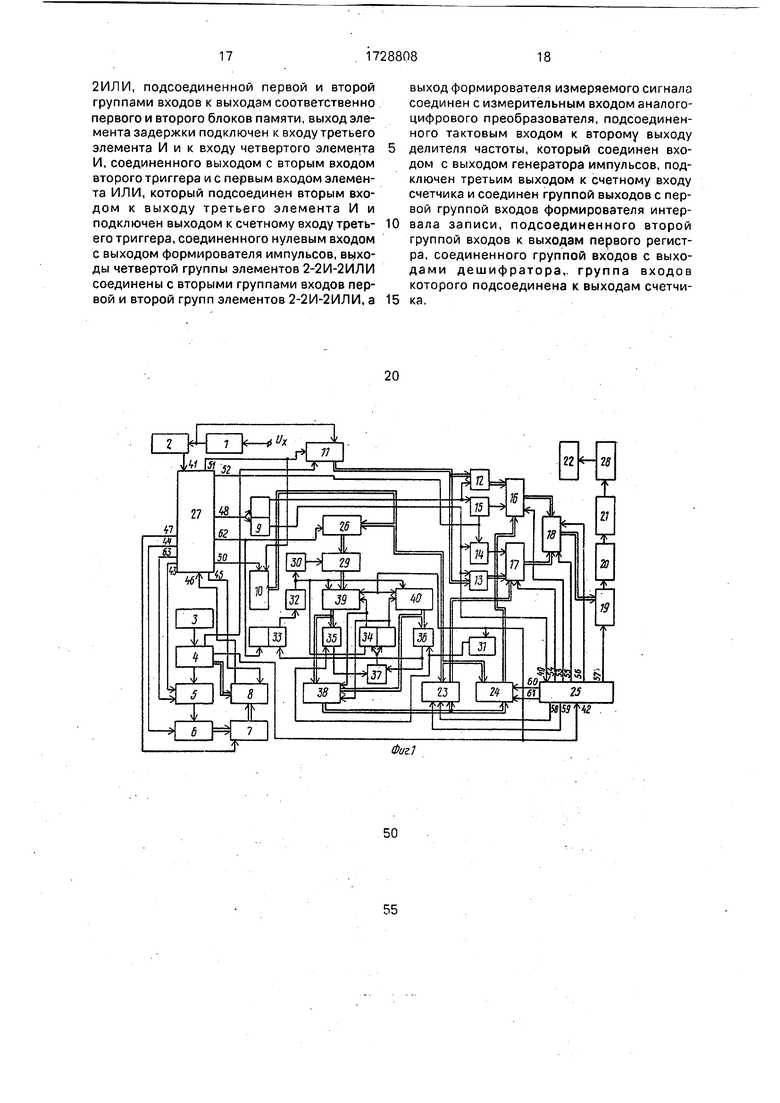

На фиг.1 приведен блок-схема предлагаемого устройства для измерения средне- квадратического значения сигнала: на фиг.2 - временные диаграммы работы формирователя управляющих сигналов; на фиг.З - блок-схема формирователя интервалов записи; на фиг.4 - временные диаграммы работы формирователя сигналов считывания: на фиг.5 - блок-схема группы элементов 2- 2И-2ИЛИ.

Предлагаемое устройство для измерения среднеквадратического значения сигнала (фиг.1) состоит из формирователя 1 измеряемого сигнала, формирователя 2 импульсов перехода через нуль, генератора 3 импульсов, делителя 4 частоты, счетчика 5, дешифратора 6, регистра 7, формирователя 8 интервала записи, триггера 9;счетчика 10 адреса, аналого-цифрового преобразователя 11, групп элементов И 12 и 13, элементов и 14 и 15, блоков 16 и 17 памяти, группы элементов 2-2И-2ИЛИ 18, регистра 19. циф- роаналогового преобразователя 20, формирователя 21 среднеквадратических значений, блока 22 регистрации, групп элементов 2-2И-2ИЛИ 23 и 24, формирователя 25 сигналов считывания, регистра 26, формирователя 27 управляющих сигналов, усилителя 28, группы элементов 2-2И-2ИЛИ 29, элементов 30 и 31 задержки, формирователя 32 импульсов, триггеров 33 и 34, элементов И 35 и 36, элемента ИЛИ 37, группы элементов 2-2И-2ИЛИ 38, реверсивных счетчиков 39 и 40.

Вход прибора их соединен с выходом формирователя 1 измеряемого сигнала, выход которого соединен с входом формирователя 2 импульсов перехода через нуль и измерительным входом аналого-цифрового преобразователя 11. Выход формирователя 2 импульсов перехода через нуль соединен с первым входом 41 формирователя 27 управляющих сигналов.

Выход генератора 3 импульсов.соединен с входом делителя 4 частоты. Первый выход делителя 4 частоты соединен со счетным входом счетчика 5. Второй выход делителя 4 частоты соединен с первым входом 42 формирователя 25 сигналов считывания, счетными входами реверсивных счетчиков 39 и 40 и входом элемента 31 задержки.

Третий выход делителя 4 частоты соединен с тактовым входом аналого-цифрового преобразователя 11. Четвертый выход делителя 4 частоты соединен с первым входом формирователя 8 интервала записи. Нуле0 вой вход счетчика 5 соединен с первым выходом 63 формирователя 27 управляющих сигналов, второй выход 43 которого соединен с входом разрешения счетчика 5, Выход счетчика 5 соединен с первым входом де5 шифратора 6, второй вход которого соединен с третьим выходом 44 формирователя 27 управляющих сигналов. Выход дешифратора 6 соединен с входом регистра 7, выход которого соединен с вторым входом форми0 рователя 8 интервала записи, третий вход которого соединен с четвертым выходом 45 формирователя 27 управляющих сигналов. Выход формирователя 8 интервала записи соединен с вторым входом 46 формировате5 ля 27 управляющих сигналов. Пятый выход 47 формирователя 27 управляющих сигналов соединен с вторым входом регистра 7.

Счетный вход триггера 9 соединен с шестым выходом 48 Формирователя 27 управ0 ляющих сигналов. Первый выход триггера 9 соединен с первым входом группы элементов И 12 и с первым входом элемента И 15. Второй выход триггера 9 соединен с первыми входами группы элементов И 13, первым

5 входом элемента И 14 и вторым входом 49 формирователя 25 сигналов считывания.

Нулевой вход счетчика 10 адреса соединен с седьмым выходом 50 формирователя 27 управляющих сигналов. Счетный вход

0 счетчика 10 адреса соединен с восьмым выходом 51 формирователя 27 управляющих сигналов, запускающим входом аналого- цифрового преобразователя 11. Выход аналого-цифрового преобразователя 11

5 соединен с вторыми входами групп элементов И 12 и 13. Выход группы элементов И 12 соединен с информационным входом блока 16 памяти. Выход группы элементов И 13 соединен с информационным входом блока :

0 17 памяти. Вторые входы элементов И 14 и 15 соединены с девятым выходом 52 формирователя 27 управляющих сигналов. Выход элемента И 14 соединен с входом записи блока 17 памяти. Выход элемента И 15сое5 динен с входом записи блока 16 памяти.

Адресный вход блока 16 памяти соединен с выходом группы элементов 2--2И- 2ИЛИ 24, Адресный вход блока 17 памяти соединен с выходом группы элементов 2- 2И-2ИЛИ 23. Вход считывания блока 16 памяти соединен с первым выходом 53 формирователя 25 сигналов сиитывания. Вход счи- тывания блока 17 памяти соединен с выходом 54 формирователя 25 сигналов считываний. Выход блока 16 памяти соединен с первым входом группы элементов 2-2И-2ИЛИ 18, второй вход которой соединен с выходом блока 17 памяти.

Третий вход группы элементов 2-2И- 2ИЛИ 18 соединен с третьим выходом 55 формирователя 25 сигналов считывания, четвертый выход 56 которого соединен с четвертым входом группы элементов 2-2И- 2ИЛИ 18. Выход группы элементов 2-2И- 2ИЛИ 18 соединен с информационным входом регистра 19, вход записи которого соединен с пятым выходом 57 формирователя 25 сигналов считывания.

Выход регистра 19 соединен с информационным, входом цифроаналогового преоб- рзователя 20, выход которого через формирователь 21 среднеквадратических значений и усилитель 28 соединен с блоком 22 регистрации.

Первый вход группы элементов 2-2И- 2ИЛИ 23 соединен с выходом 58 формирователя 25 сигналов считывания, седьмой выход 59 которого соединен с вторым входом группы элементов 2-2И-2ИЛИ 23. Третий вход группы элементов 2-2И-2ИЛИ 23 соединен с третьим входом группы элементов 2-2И-2ИЛИ 24, информационным входом регистра 26 и кодовым выходом счетчика 10 адреса, Четвертый вход группы- элементов 2-2И-2ИЛ И 23 соединен с четвертым входом группы элементов 2-2И-2ИЛИ 24 и выходом группы элементов 2-2И-2ИЛИ 38. Первый вход группы элементов 2-2И- 2ИЛИ 24 соединен с восьмым выходом 60 формирователя 25 сигналов считывания, девятый выход 61 которого соединен с вторым входом группы элементов 2-2И-2ИЛИ 24,

Десятый выход 62 формирователя 27 управляющих сигналов соединен с управляющим входом регистра 26 и первым входом триггера 33. Выход регистра 26 соединен с первым входом группы элемнетов 2-2И- 2ИЛИ 29, второй вход которой соединен с выходом элемента 30 задержки. Выход группы элементов 2-2И-2ИЛИ 29 соединен с установочным входом (входами разрядов) реверсивного счетчика 39.

Вход элемента 30 задержки соединен с выходом формирователя 32 импульсов и нулевыми входами реверсивного счетчика 39, реверсивного счетчика 40, триггера 34.

Выход элемента 31 задержки соединен с первыми входами элементов И 35 и 36.

Вход формирователя 32 импульсов соединен с входом триггера 33, второй вход

которого соединен с выходом элемента И 36. первым входом элемента ИЛИ 37.

Счетный вход триггера 34 соединен с выходом элемента ИЛИ 37, первый выход

триггера 34 соединен с входом реверса реверсивного счетчика 39 и первым управляющим входом группы элементов 2-2И-2ИЛИ 38, второй управляющий вход которой соединен с вторым выходом триггера 34 и вхо0 дом реверса реверсивного счетчика 40.

Второй вход элемента И 35 соединен с кодовым выходом реверсивного счетчика 39 и с первым информационным входом группы элементов 2-2И-2ИЛИ 38, второй инфор5 мационный вход которой соединен с выходом реверсивного счетчика 40 и вторым входом элемента И З.б. Выход элемента И 35 соединен с вторым входом элемента ИЛИ 37.

0Устройство для измерения среднеквадратического значения сигнала работает следующим образом.

Переменный сигнал Ux с формирователя 1 измеряемого сигнала поступает на фор5 мирователь 2 импульсов перехода через нуль и измерительный вход аналого-цифрового преобразователя 11. По выходным сигналам формирователя 2 импульсов перехода через нуль, поступающим на вход

0 41, формирователь 27 управляющих сигна- . лов вырабатывает сигналы, синхронизирующие работу всего устройства. Временные положения сигналов формирователя 27 управляющих сигналов показаны на фиг.2.

5 С помощью генератора 3 импульсов, делителя 4 частоты, счетчика 5, дешифратора 6, регистра 7 и формирователя 8 интервала записи вырабатываются сигналы запуска аналого-цифрового преобразователя 11. Ча0 стота запуска аналого-цифрового преобразователя 11 должна быть оптимальной, т.е. число выборок за период входного сигнала определяется заданной точностью измерения.

5 Счетчик 5 подсчитывает число импульсов, которые формируются генератором 3 импульсов и делителем 4 частоты за один период входного сигнала. Для этого счетчик 5 устанавливается в нулевое состояние сиг0 налом, поступающим с выхода 63 формирователя 27 управляющих сигналов, и подсчитывает счетные импульсы, поступающие на него за один период входного сигнала. Разрешение на прохождение импульсов

5 на счетчик 5 поступает с выхода 43 формирователя 27 управляющих сигналов. Показания счетчика 5 анализируются дешифратором 6 и при наличии управляющего сигнала на выходе 44 формирователя 27 управляющих сигналов дешифратор 6 выдает сигнал на регистр 7. который в нем запоминается. Формирователь 8 интервала записи по состоянию регистра 7 и соответствующим этому состоянию сигналам делителя 4 частоты формирует сигналы определенной частоты, которые поступают на вход 46 формирователя 27 управляющих сигналов. По этим сигналам формирователь 27 управляющих сигналов вырабатывает сигналы запуска аналого-цифрового преобразователя 11, которые с выхода 51 поступают на запуск аналого-цифрового преобразователя 11 и счетчик 10 адреса,

Информация, преобразованная аналого-цифровым преобразователем 11, поступает поочередно на блоки 16 и 17 памяти. Разделение этой информации производится триггером 9, управление которого осуществляется сигналом, поступающим на его счетный вход с выхода 48 формирователя 27 управляющих сигналов.

Управляющий сигнал с нулевого выхода триггера 9 разрешает прохождение кодовой информации с выхода аналого-цифрового преобразователя 11 через группу элементов И 12 на информационный вход блока 16 памяти. На информационный вход второго блока 17 памяти кодовая информация с выхода АЦП 11 не поступает, поскольку в этот момент времени на группу элементов И 13 поступает запрещающий потенциал с второго выхода триггера 9.

На адресный вход первого блока управления в это время поступает код адреса счетчика 10 адреса, который формирует адрес записи, подсчитывая сигналы запуска аналого-цифрового преобразователя 11. Код адреса записи, сформированный счетчиком 10 адреса, через группу элементов 2-2И-2ИЛИ 24 при наличии управляющего сигнала на выходе 60 формирователя 25 сигналов считывания, поступает на адресный вход блока 16 памяти. Запись информации в блок 16 памяти производится по сигналу, поступающему с выхода 52 формирователя 27 управляющих сигналов, который проходит через элемент И 15 на выход записи блока 16 памяти.

В это же время с блока 17 памяти считывается информация, поступившая в него в предыдущем такте. Из адреса записи, сформированного счетчиком 10 адреса, триггер 33, формирователь 32 импульсов, элементы 30 и 31 задержки, регистр 26, группа элементов 2-2И-2ИЛИ 29. реверсивные счетчики 39 и 40, элементы И 35 и 36, элемент ИЛИ 37. группа элементов 2-2И- 2ИЛИ 38, триггер 34 вырабатывают адреса для непрерывного считывания информации

с блока 17 памяти, необходимые для восстановления переменного входного сигнала.

По сигналу с выхода 62 формирователя 27 управляющих сигналов в единичное состояние устанавливается триггер 33, а в регистр 26 из счетчика 10 адреса переписывается код адреса считывания. Затем этот код адреса через группу элементов 2-2И- 2ИЛИ 29 переписывается в реверсивный

0 счетчик 39. Управляющие сигналы, необходимые для переписи кода адреса считывания из регистра 26 в реверсивный счетчик 39, формируются триггером 33, формирователем 32 импульсов и элементом 30 задерж5 ки.

Перепись кода происходит в момент, когда в реверсивном счетчике 40 код будет равен нулю. В этот момент времени триггер 34 находится в таком состоянии, что ревер0 сивный счетчик 40 будет работать на сложение, а реверсивный счетчик 39 на вычитание. При поступлении счетных импульсов на счетный вход реверсивных счетчиков 39 и 40 в реверсивном счетчике 39

5 будут накапливаться счетные импульсы, число которых определяет код адреса считывания. Код реверсивного счетчика 40 через группу элементов 2-2И-2ИЛИ 38 поступает на информационные входы групп

0 элементов 2-2И-2ИЛ И 23 и 24. Прохождение кода с реверсивного счетчика 40 через группу элементов 2-2И-2ИЛИ 38 осуществляется управляющими сигналами триггера 34 (с второго выхода). Когда число в реверсивном

5 счетчике 39 станет равным нулю, сработает элемент И 35. Сигнал элемента И 35 поступает через элемент ИЛИ 37 на счетный вход триггера 34 и переводит его в другое состояние. При этом на вычитание будет работать

0 реверсивный счетчик 39, а на сложение реверсивный счётчик 40. При поступлении счетных импульсов из делителя 4 частоты на счетный вход реверсивных счетчиков 39 и 40 в реверсивном счетчике 40 будут накапли5 ваться счетные импульсы, число которых определяет код адреса считывания. Код реверсивного счетчика 39 через группу элементов 2-2И-2ИЛИ 38 поступает на информационные входы групп элементов

0 2-2И-2ИЛИ 23 и 24. Прохождение кода с реверсивного счетчика 39 через группу элементов 2-2И-2ИЛИ 38 осуществляется управляющими сигналами счетного триггера 34 (с первого выхода). Когда число в ревер5 сивном счетчике 40 станет равным нулю, сработает элемент И 36. Сигнал элемента И 36 поступает через элемент ИЛИ 37 на счетный вход триггера 34 и переводит его в другое состояние. Таким образом производится формирование адреса считывания, необходимого для непрерывного восстановления переменного входного сигнала.

Когда число в реверсивном счетчике 40 станет равным нулю, сигнал элемента И 36 поступает еще на нулевой вход триггера 33. Если в это время триггер 33 находится в единичном состоянии, то он переходит в нулевое состояние. При этом из выходного сигнала триггера 33 формирователем 32 импульсов вырабатывается узкий импульс, который обнуляет реверсивный счетчик 39. Затем в реверсивный счетчик 39 через группу элементов 2-2И-2ИЛИ 29 производится запись кода адреса считывания, находящегося в счетчике 10 адреса.

Адрес считывания, сформированный на выходе группы элементов 2-2И-2ИЛИ 38, при наличии управляющего сигнала на выходе 58 формирователя 25 сигналов считывания, через группу элементов 2-2И-2ИЛИ 23 поступает на адресный вход блока 17 памяти. По сигналу считывания, поступающему с выхода 55 формирователя 25 сигналов считывания, информация с блока 17 памяти через группу элементов 2-2И-2ИЛИ 18 поступает на информационный вход регистра 19. Запись информации в регистр 19 производится управляющим сигналом, поступающим с выхода 57 формирователя 25 сигналов считывания. После восстановления переменного входного сигнала цифро- аналоговым преобразователем 20 производится преобразование этого сигнала в постоянный формирователем 21 сред- неквадратических значений, его усиление усилителем 28 и индикация результата измерения блоком 22 регистрации.

При поступлении второго импульса с выхода 48 формирователя 27 управляющих сигналов на счетный вход триггера 9 он изменяет свое состояние. При этом запись информации производится в блок 17 памяти, а считывание информации производится с блока 16 памяти. В этом случае кодовая информация с выхода аналого-цифрового преобразователя 11 через группу элементов И 13 поступает на информационный вход блока 17 памяти, поскольку на второй вход группы элементов И 13 поступает разрешающий потенциал с второго выхода триггера 9, Код адреса, сформированный счетчиком 10 адреса, через группу элементов 2-2И- 2ИЛИ при наличии управляющего сигнала с выхода 59 формирователя 25 сигналов считывания поступает на адресный вход блока 17 памяти. Запись информации в блок 17 памяти производится по сигналу, поступающему с выхода 52 формирователя 27 управляющих сигналов через элемент И 14 на вход записи блока 17 памяти.

В это же время из блока 16 памяти считывается информация, поступившая в него

в предыдущий такт.

Адрес считывания, сформированный на выходе группы элементов 2-2И-2ИЛИ 38 при наличии управляющего сигнала на выходе 61 формирователя 25 сигналов считы0 вания, через группу элементов 2-2И-2ИЛИ 24 поступает на адресный вход блока 16 памяти. По сигналу считывания, поступающему с выхода 56 формирователя 25 сигналов считывания, информация с блока 16

5 памяти через группу элементов 2-2И-2ИЛИ 18 поступает на информационный вход регистра 19.

При изменении частоты входного сигнала происходит изменение кода адреса счи0 тывания (записи). В счетчике 10 адреса в зависимости от периода входного сигнала при постоянном интервале запуска аналого- цифрового преобразователя 11 будет накапливаться разное число импульсов за период

5 входного сигнала. Это приведет к неполному восстановлению входного сигнала, если код адреса считывания.в предыдущий такт был больше кода адреса считывания в последующий такт, т.е. некоторые выборки за0 писи информации, хранящиеся в блоках 16 и 17 памяти,не будут считаны. Для исключения неполного восстановления входного сигнала в предлагаемом устройстве восстановление входного сигнала в последующем

5 такте начинается после того, как будут считаны все выборки мгновенного значения входного сигнала в предыдущем такте, хранящемся в блоках 16 и 17 памяти. Поэтому запись нового кода адреса считывания в ре0 версивный счетчик 39 производится с регистра 26 только после установления в нуль реверсивного счетчика 40, что соответствует считыванию с блоков 16 и 17 памяти всех выборок мгновенных значений входного

5 сигнала в предыдущем такте.

Предлагаемое устройство обладает техническим преимуществом по сравнению с известным - отсутствием частотной составляющей погрешности, равной 2%. Это обус0 ловлено тем, что в предлагаемом устройстве измерение среднеквадратических значений переменных сигналов, изменяющихся в широком частотном диапазоне, производится в узком частотном диапазоне.

5 Формула изобретения

Устройство для измерения среднеквад- ратического значения сигнала, содержащее формирователь измеряемого сигнала, подсоединенный входом к входной шине, формирователь среднеквадратического

значения, выход которого соединен через усилитель с входом блока регистрации, формирователь управляющих сигналов и формирователь импульсов, отличающее- с я тем, что, с целью повышения точности результата измерения среднеквадратиче- ского значения сигнала, в него введены первый регистр и дешифратор, подсоединенные входами соответственно к первому и второму выходам формирователя управляющих сигналов, счетчик, соединенный нуле- вым входом и входом разрешения соответственно с третьим и четвертым выходами формирователя управляющих сигналов, второй регистр, подсоединенный управляющим входом к пятому выходу формирователя управляющих сигналов, первый и второй элементы И,соединенные первыми входами с шестым выходом формирователя управляющих сигналов, аналого-цифровой преобразователь, подсоединенный запускающим входом к седьмому выходу формирователя, управляющих сигналов, счетчик адреса, соединенный нулевым входом с восьмым выходом формирователя управляющих сигналов, первый триггер, подсоединенный счетным входом к девятому выходу формирователя управляющих сигналов, формирователь интервала за- писи, соединенный входом и выходом соответственно с десятым выходом и первым входом формирователя управляющих сигналов, формирователь импульсов перехода через ноль, включенный между выходом формирователя измеряемого сигнала и вторым входом формирователя управляющих сигналов, первый и второй реверсивные счетчики, подсоединенные нулевыми входами к выходу формирователя импульсов, цифроаналоговый преобразователь, подключенный выходом к входу формирователя среднеквадратического значения, формирователь сигналов считывания, третий регистр, второй триггер, подключенный выходом к входу формирователя импульсов, третий триггер, первый и второй элементы задержки, третий и четвертый элементы И, первая, вторая, третья, четвертая и пятая группы элементов 2-2И-2ИЛИ. первая и вторая группы элементов И, первый и второй блоки памяти, делитель частоты, генератор импульсов и элемент ИЛИ. причем формирователь управляющих сигналов подключен пятым и седьмым выходами соответственно к первому входу второго триггера и к счетному входу счетчика адреса, соединенного выходами с первыми группами входов первой и второй групп элементов 2-2И-2ИЛИ и с информационными входами второго регистра, выходы которого подключены к группе

входов третьей группы элементов 2-2И- 2ИЛИ, подсоединенной входом к выходу первого элемента задержки и соединенного выходами с информационными входами

первого реверсивного счетчика, выходы которого подключены к группе входов третьего элемента И и к первой группе входов четвертой группы элементов2-2И-2ИЛИ, подсоединенной первым входом к первому выходу

0 третьего триггера,, подключенному к входу реверса первого реверсивного счетчика, подсоединеного счетным входом к первому выходу делителя частоты, соединеному с первым входом формирователя сигналов

5 считывания, с входом второго элемента задержки и с счетным входом второго реверсивного счетчика, подключенного выходами к группе входов четвертого элемента И и к второй группе входов четвертой группы эле0 ментов 2-2И-2ИЛИ, второй вход которой подсоединен к второму выходу третьего триггера, соединенному с входом реверса второго реверсивного счетчика, формирователь сигналов считывания подключен пер5 вым, вторым и третьим выходами соответственно к входу третьего регистра и к входам считывания первого и второго блоков памяти, соединен четвертым и пятым выходами с первым и вторым входами пер0 вой группы элементов 2-2И-2ИЛИ, подключен шестым и седьмым выходами к первому и второму входам второй группы элементов 2-2И-2ИЛИ, соединен восьмым и девятым выходами с первыми и вторыми входами

5 пятой группы элементов 2-2И-2ИЛИ и подсоединен вторым входом к первому выходу первого триггера, соединенному с входом первой группы элементов И и с вторым входом первого элемента И, подключенного вы

0 ходом к входу записи первого блока памяти, который подсоединен адресными входами к выходам первой группы элементов 2-2И- 2ИЛИ и соединен информационными входами с выходами первой группы элементов И,

5 подсоединенной группой входов к выходам аналого-цифрового преобразователя, под- ключеным к группе входов второй группы элементов И, соединенного выходами с информационными входами второго блока па0 мяти, который соединен адресными входами с выходами второй группы элементов 2-2И-2ИЛИ и подсоединен входом записи к выходу второго элемента И, соединенного вторым входом с вторым вы5 ходом первого триггера, подключенным к второму входу второй группы элементов И, вход цифроаналогового преобразователя подсоединен к выходу третьего регистра, соединенного информационными входами с выходами пятой группы элементов 2-2И2ИЛИ, подсоединенной первой и второй группами входов к выходам соответственно первого и второго блоков памяти, выход элемента задержки подключен к входу третьего элемента И и к входу четвертого элемента И, соединенного выходом с вторым входом второго триггера и с первым входом элемента ИЛИ, который подсоединен вторым входом к выходу третьего элемента И и подключен выходом к счетному входу третьего триггера, соединенного нулевым входом с выходом формирователя импульсов, выходы четвертой группы элементов 2-2И-2ИЛИ соединены с вторыми группами входов первой и второй групп элементов 2-2И-2ИЛИ, а

выход формирователя измеряемого сигнала соединен с измерительным входом аналого- цифрового преобразователя, подсоединенного тактовым входом к второму выходу

делителя частоты, который соединен входом с выходом генератора импульсов, подключен третьим выходом к счетному входу счетчика и соединен группой выходов с первой группой входов формирователя интервала записи, подсоединенного второй группой входов к выходам первого регистра, соединенного группой входов с выходами дешифратора,, группа входов которого подсоединена к выходам счетчика.

4t

Л-Л А АЛ АЛ А АЛ

vvV/v yV/Y/Y/V/

К 6л. 7

«

Фиг. I

Фиг.З

1Ь &. . .Ъ

О, .-Ј t -O °

J ., O CJ-, u-j ГЧ 0 to LO trji LT) l-O

К 5л 25 Управляющие

$ 4

Фиг. 5

| Хлыстунов В.М | |||

| .Основы цифровой электроизмерительной техники | |||

| - М.-Л.: Энергия, 1966, с.102-110 | |||

| Шрамков Е.Г | |||

| Электрические измерения | |||

| - М.: Высшая школа, 1972, с.126. |

Авторы

Даты

1992-04-23—Публикация

1989-07-10—Подача