(54) РАЗРЯД РЕВЕРСИВНОГО СЧЕТЧИКА

1

Изобретение относится к устройствам реверсивного деления частоты импульсных сигналов и может быть использовано при построении реверсивных и разиостных счетчиков различного назначения для измерительной, управляющей, и вычислительной аппаратуры.

Известны реверсивные счетчики импульсов, каждый разряд в которых содержит счетный триггер, первый и второй злементы совпадения и злемент сборки (злемент ИЛИ), первый и второй входы которого соеданены соответственно с первым и вторым входами разряда реверсивного счетчика, которые соединены с первыми входами соответственно первого и второго злементов совпадения, вторые входы которых соединены соответственно с прямым и инверсным выходами счетного триггера, а выходы первого и второго элементов совпадения соединены соответственно с первым и вторым выходами разряда реверсивного счетчика импульсов 1

Недостатком этого разряда реверсивного счетчика является относительно большая задержка формирования выходного сигнала при счете, :-.. () с тем. что по сравнению с обычИМПУЛЬСОВ

.ными двоичными счетчиками, кроме времени, необходимого для срабатывания собственно счетного триггера, требуется дополиительиое время, необходимое для срабатывания межразрядного коммутирующего злемента (в данном случае его функции вьшолняют злементы совпадения и сборки).

Известен разряд реверсивного счетчика импульсов, содержащий две входные шины, счетный триггер и три злемента И-НЕ, выход, первый и второй входы первого злемента И-НЕ

10 соединены соответственно со счетным входом счетного триггера, с выходами второго и третьего злементов И-НЕ, первые входы которых соединень соответственно- с первой и второй

15 входными шинами, вторые входы второго и третьего элементов И-НЕ соединены соответственно с прямым и инверсным выходами счетного триггера предыдущего разряда 2.

Недостатком известного устройства является

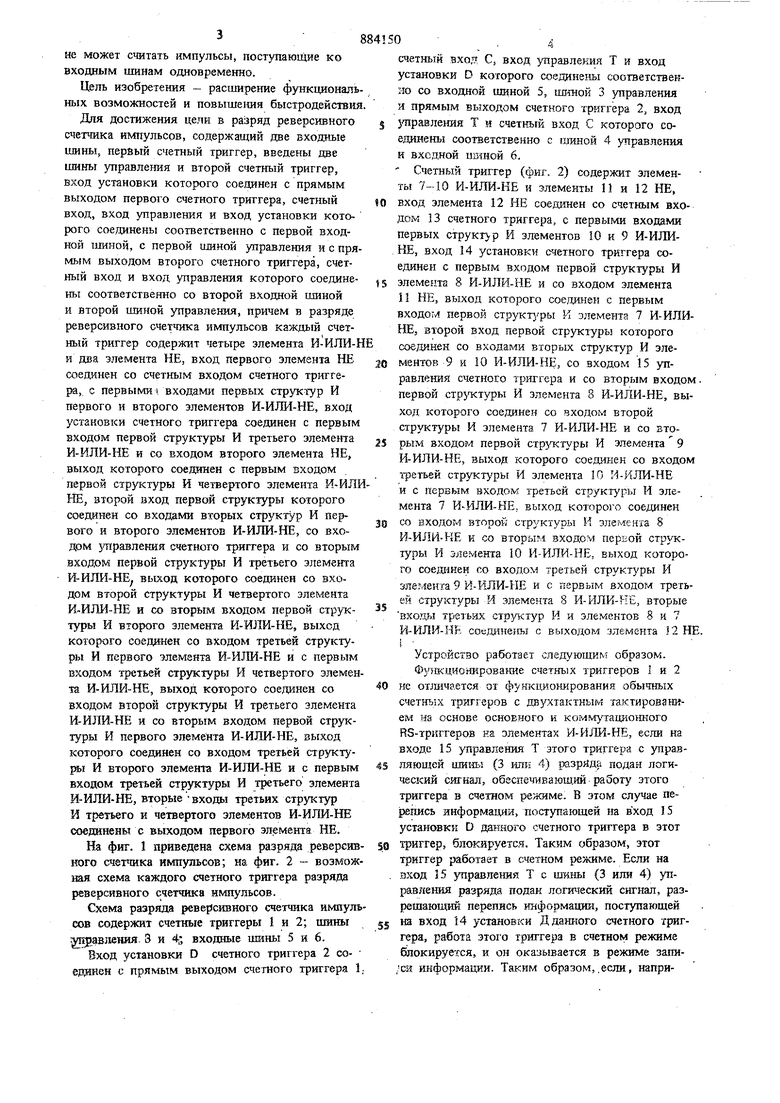

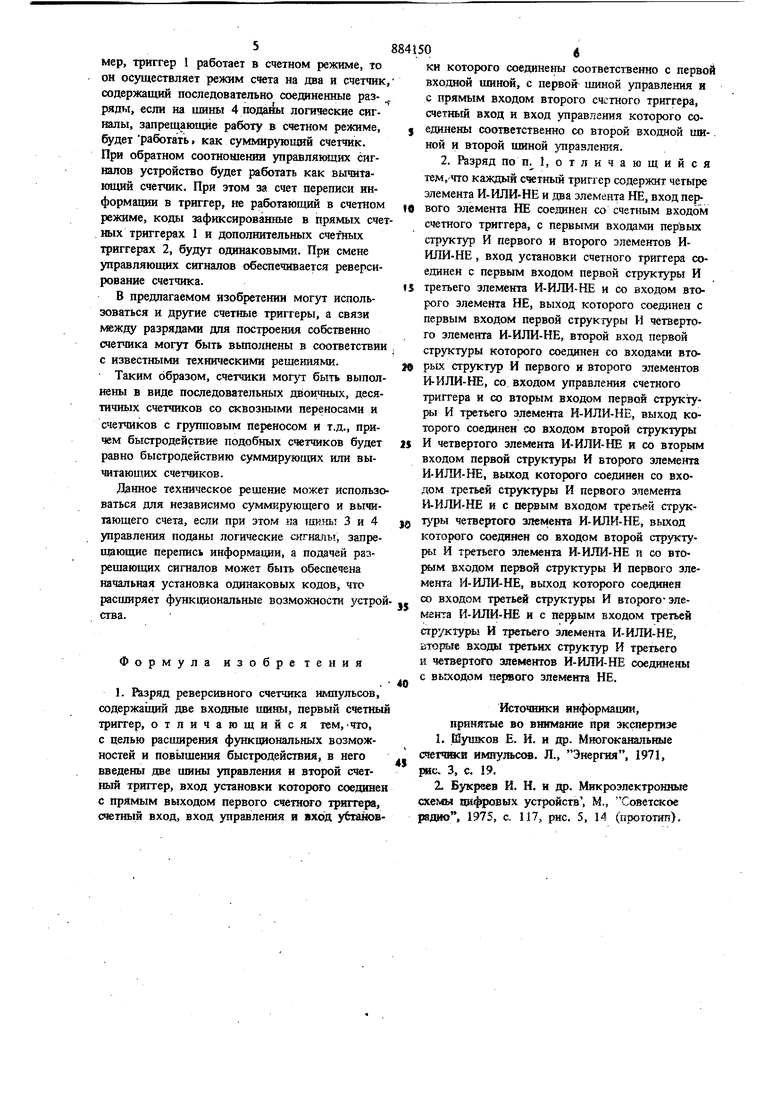

20 относительно низкое быстродействие, -гто связано с задержкой сигналов переноса в злементах И-НЕ, и относительно малые функциональные возможности, что связано с тем, что разряд не может считать импульсы, поступающие ко входным шинам одновременно. Цель изобретения - расширение функциональ ных возможностей и повыше1шя быстродействия Для достижения цели в ра;зряд реверсивного счетчика импульсов, содержащий две входные шины, первый счетный триггер, введены две шины управления и второй счетный триггер, вход установки которого соединен с прямым выходом первого счетного триггера, счетный вход, вход управления и вход установки которого соединены соответственно с первой входной шиной, с первой шиной управления и с пря мым выходом второго счетного триггера, счетный вход и вход управления которого соединепы соответственно со второй входной шиной и второй щиной управления, причем в разряде реверсивного импульсов каждый счетный триггер содержит четыре элемента И-ИЛИ-Н и два элемента НЕ, вход первого элемента НЕ соединен со счетным входом счетного триггера, с первыми I входами первых структур И первого и второго элементов И-И.ПИ-НЕ, вход установки счетного триггера соединен с первым входом первой структуры И третьего элемента И-ИЛИ-НЕ и со входом второго элемента НЕ, выход которого соединен с первым входом первой структуры И четвертого элемента И-ИЛ НЕ, второй вход первой структуры которого соединен со входами вторых структур И первого и второго элементов И-ИЛИ-НЕ, со входом управления счетного триггера и со вторым входом первой структуры И третьего элемента И-ИЛИ-НЕ выход которого соединен со входом второй структуры И четвертого элемента И..ИЛМ-НБ и со вторым входом первой структуры И второго элемента И-ЙЛИ-НЕ, выход которого соединен со входом третьей структуры И первого элемента И-ИЛИ-НЕ и с первым входом третьей стрзлктуры И четвертого элемен та И-ИЛИ-НЕ, выход которого соединен со входом второй структуры И третьего элемента И-ИЛИ-НЕ и со вторым входом первой структуры И первого элемента И-ИЛИ-НЕ, зыход которого соединен со входом третьей структуры И второго элемента и с первым входом третьей структуры И третьего элемента И-ИЛИ-НЕ, вторые входы третьих структур И третьего и четвертого элементов И-ИЛИ-НЕ соединены с выходом первого элемента НЕ. На фиг. 1 приведена схема разряда реверсив ного счегшка импульсов; из фиг. 2 - воэмож ная схема каждого счетного триггера разряда реверсивного счетчика импульсов. Схема разряда реверсивного счетчика импул сов содержит счетные триггеры 1 и 2; шины {равзюния. 3 и 4-, входные шины 5 и 6. Вход установки D счетного триггера 2 соеданен с прямым выходом счетного триггера .4 счетный вход С, вход правлекия Т и вход установки D которого соедине15ы соответственно со входной шиной 5, шютой 3 управления и прямым выходом счетного триггера 2, вход Зщравления Т и счетный вход С которого соединены соответственно с ыиной 4 управления и входной ишной 6, - Счетный триггер (фиг, 2) содержит элемен- ты 7-10 И-ИЛИ-НЕ и элементы 11 и 12 НЕ, вход элемента 12 НЕ соединен со счетным входом 13 счетного триггера, с первыми входами первых структур И элементов 10 и 9 И-ИЛИНЕ, вход 14 установки счетного триггера соединен с первым входом первой структуры И элемента 8 И-ИЛИ-НЕ и со входом элемента il НЕ, выход которого соединен с первым входом первой структ ры И элемента 7 И-ИЛИНЕ, второй вход первой структуры которого соединен со входами вторых структур И элементов 9 и 10 И-ИЛИ-НЕ, со входом 15 управления счетного триггера и со вторым входом, первой структуры И элемента 8 И-ИЛИ-НЕ, выход которого соединен со входом второй структуры И элемента 7 И-ИЛИ-НЕ и со вторым входом первой стр тстуры И элемента 9 И-ИЛИ-НЕ, выход которого соединен со входом третьей структ ры И элемента 10 М-ИЛИ-НЕ и с первым входом третьей структуры И элемента 7 И ИЛИ-НЕ. выход которого соединен со входом второй структуры И элемента 8 й-ИЛИ-НЕ и со вторым входсгм первой структуры И элемента 10 И-ИЛИ-НЕ, выход которого соединен со входом третьей структуры И элемента 9 й-ИЛИ-НЕ и с первым входоги: третьей структуры И элемента 8 И-ИЛИ-НЕ, вторые входы третьих структур И и элементов 8 и 7 И-ИЛИ-НЕ соедине}5Ы с BFJFXOAOM элемента 12 НЕ. Устройство работает cлeдyющи образом. Фу51кционировакие счетных триггеров 1 и 2 не от;шчается от фзнкци-ои-шрования обычных счетнъ5Х триггеров с двухтактным тактированием на основе основного и комм пгацио{шого RS-TpKiTepoB на элементах И-ИЛИ-НЕ, если на входе 15 )правления Т этого триггера с управляющей шинь5 (3 или 4) разряда подан логический сигнал, обеспечивающий-работу этого триггера в счетном режиме. В этом случае перепись информации, поступающей на вход 15 установки D данного счетного триггера в этот 1риггер, блокируется. Таким образом, этот триггер работает в счетном режиме. Если на вход 15 управле1шя Т с ш-кны (3 или 4) управяения разряда подан логический сигнал, разрешающий перепись информации, поступающей на вход 14 установки Д данного счетного триггера, работа этого триггера в счетном режиме блокируется, и он оказывается в режиме запи,сй информации. Таким образом,.если, например, триггер 1 работает в счетном режиме, то он осуществляет режим счета на два и счетчик содержащий последовательно соединенные разряды, если на щины 4 поданы логические сигналы, запрещающие работу в счетном режиме, будет работать, как суммирующий счетчик. При обратном соотношении управляющих сигналов устройство будет работать как вьгантающий счетчик. При этом за счет переписи информации в триггер, ие работающий в счетном режиме, коды зафиксированные в прямых счет ных триггерах 1 и дополнительных счетных триггерах 2, будут одинаковыми. При смене управляющих сигналов обеспечивается реверсирование счетчика. В предлагаемом изобретении могут использоваться и другие счетные триггеры, а связи между разрядами для построения собственно счетчика могут быть вьщогшены в соответствии с известными техническими решениями. Таким образом, счетчики MorjT быть выполнены в виде последовательных двоичных, десятичных счетчиков со сквозными переносами и счетчиков с групповым переносом и т.д., причем быстродействие подобных счетчиков будет равно быстродействию суммирующих или вычитающих счетчиков. Данное техническое рещение может использо ваться для независимо сзммкрующего и вычитающего счета, если при этом на ширгк 3 и 4 управления поданы логические сигналы, запрещающие перепись информации, а подачей разрещающих сигиалов может бьпъ обеспечена начальная установка одинаковых кодов, что расщиряет функщюнальные возможности устро ства. Формула изобретения 1. К13ряд реверсивного счетчика илшульсов, содержавши две входные щины, первый счетны триггер, отличающийся тем, Что, с целью расщирения функциональных возможностей и повыщения быстродействия, в него введены дае щииы управления и второй счетный триггер, вход установки которого соедине с прямым выходом первого счетного триггера, счетный вход, вход управления и вход убташв ки которого соединены соответственно с первой входной щиной, с первой шиной управления и с прямым входом второго счетного триггера, счетный вход и вход управления которого соединены соответственно со второй входной щи-. ной и второй щнной управления. 2. Разряд по п. 1, о т л и ч а ю щ и и с я тем, что каждый счетный триггер содержит четыре элемента И-ИЛИ-НЕ и два элемента НЕ, вход первого элемента НЕ соединен со счетным входом счетного триггера, с первыми входами первых структур И первого и второго элементов ИИЛИ-НЕ, вход установки счетного триггера соединен с первым входом первой структуры И третьего элемента И-ИЛИ-НЕ и со входом второго элемента НЕ, выход которого соединен с первым входом первой структуры И четвертого элемента И-ИЛИ-НЕ, второй вход первой структуры которого соединен со входами вторых структур И первого и второго элементов И-ИЛИ-НЕ, со входом управления счетного триггера и со вторым входом первой структуры И третьего элемента И-ИЛИ-НЕ, выход которого соединен со входом второй структ5фы И четвертого элемента И-ИЛИ-НЕ и со вторым входом первой структуры И второго элемента И-ИЛИ-НЕ, выход которого соединен со входом третьей структуры И первого элемента И-ИЛИ-НЕ и с первым входом третьей структ ры четвертого элемента И-ИЛИ-НЕ, вьLxoд которого соединен со входом второй структуры И третьего элемента И-ИЛИ-НЕ и со втормм входом пе|жой структуры И первого элемента И-ИЛИ-НЕ, выход которого соединен со входом третьей структуры И второго- элемгнта И-ИЛИ-НЕ и с пepjpым входом третьей структуры И третьего эдамента И-ИЛИ-НЕ, вторые входы третьих структур И третьего к четвертого элелюнтов И-ИЛИ-НЕ соединены с вькодом пертого элемента НЕ. Источники информации, принятые во вшгмание при экспертизе 1.Шущков Е. И. и др. Многоканальные счетчшсй импульс(. Л., Энергия, 1971, рйс. 3, с. 19. 2,Букрзев И. Н. и др. Микроэлектронные схемы шаровых устройств , М., Советское рвдао, 1975, с, 117, рис. 5, 14 (прототш).

У

| название | год | авторы | номер документа |

|---|---|---|---|

| Реверсивное счетное устройство | 1981 |

|

SU974595A1 |

| Цифровой периодомер | 1985 |

|

SU1337801A1 |

| Следящий аналого-цифровой преобразо-ВАТЕль | 1979 |

|

SU797064A1 |

| Адаптивный аналого-цифровой преобразователь | 1983 |

|

SU1109899A1 |

| Реверсивный счетчик | 1981 |

|

SU982201A1 |

| Реверсивный счетчик | 1988 |

|

SU1511863A1 |

| Генератор векторов | 1987 |

|

SU1437880A1 |

| Реверсивное пересчетное устройство | 1982 |

|

SU1092732A1 |

| Адаптивный формирователь опережающего синхросигнала | 1988 |

|

SU1554110A1 |

| Цифровой некогерентный дискриминатор задержки псевдослучайного радиосигнала | 1983 |

|

SU1131034A2 |

Авторы

Даты

1981-11-23—Публикация

1980-03-18—Подача