оо

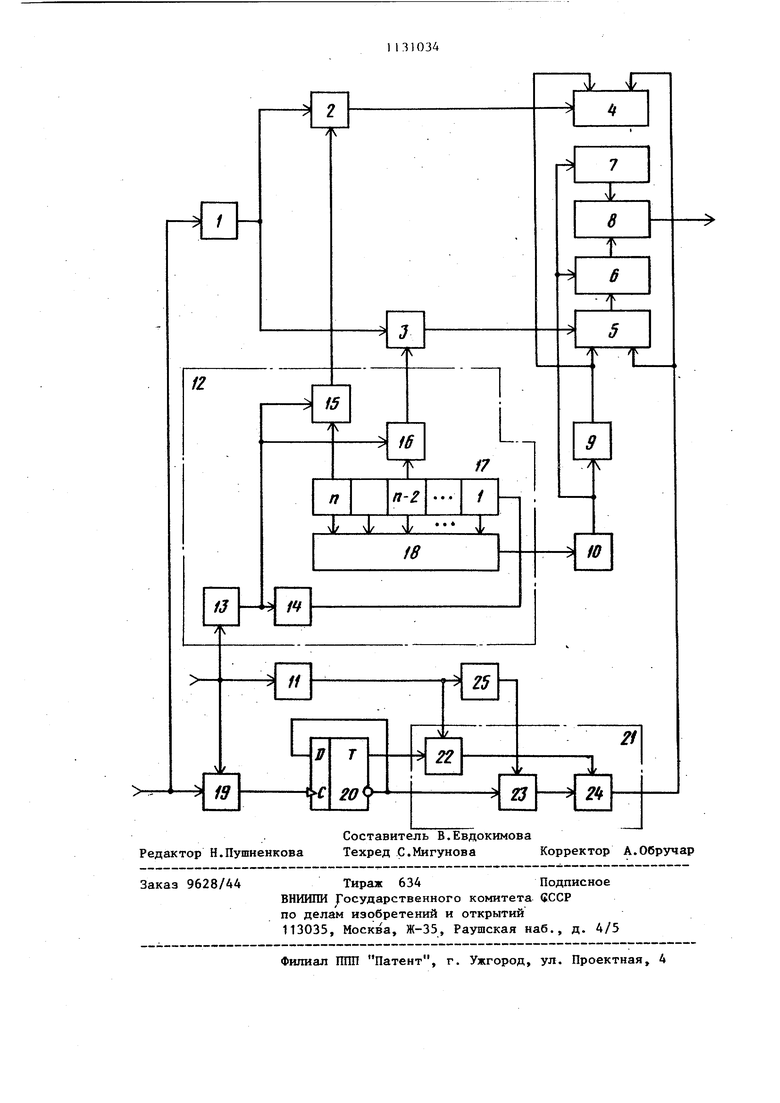

о со Изобретение относится к технике связи и может использоваться в сист мах связи и Управления с псевдослучайными сигналами. По основному авт.св. № 726671 известен цифровой некогерентный дис риминатор задержки псевдослучайного радиосигнала, содержащий объединенные по входу первый и второй перемножители, выход каждого из которых через последовательно соединенные реверсивный счетчик и стробирующий блок подключен к соответствующему входу вычитающего блока, а также опорный генератор, выходы которого подключены к другим входам первого и второго перемножителей, формирователь входного сигнала, блок задержки и два формирователя импульсов, причем выход формирователя входного сигнала подключен к входам первого и второго перёмножителей, дополнительный выход опорного генератора через последовательно соединенные первьй формирователь импульсов и блок задержки подключен к вторым входам реверсивных счетчиков, третьи входы кото рых соединены с выходом второго фор мирователя импульсов, вход которого объединен с входом опорного генератора, а выход первого формировате ля импульсов подключен к другим входам стробирующих блоковLi Однако известный цифровой некогерентный дискриминатор задержки имеет недостаточные устойчивость и точность, поскольку из-за случай ности начальной фазы входного сигнала возникает неоднозначность в о счетах, приводящая к срьшу работы дискриминатора при совпадении счет ных импульсов с моментами изменени фазы входного клиппированного сигнала. Цель изобретения - повышение точности путем исключения сбоев в работе дискриминатора при совпадении счетных импульсов с моментами изменения фазы входного сигнала Эта цель достига ется тем, что в цифровой некогерентный дискриминатор задержки псевдослучайного радиосигнала, содержащий объединен ные по входу первый и второй перемножители, выход каждого из которых через последовательно соединенные реверсивньй счетчик.и стробирунщий блок подключен к соответствующему входу вычитающего блока, а также опорный генератор, выходы которого подключены к другим входам первого и второго перемножителей, формирователь входного сигнала,блок задержки и два формирователя импульсов, причем выход формирователя входного сигнала подключен к входам первого и второго перемножителей, дополнительный выход опорного генератора через последовательно соединенные первьм формирователь импульсов и блок задержки подключен к вторым входам реверсивных счетчиков, третьим входы которых соединены с выходом второго формирователя импульсов, вход которого объединен с входом опорного генератора, а выход первого формирователя импульсов подключен к другим входам стробирующих блоков, введены дополнительный блок задержки, управляемый коммутатор и последовательно соединенные фазосдвиГающий блок и . тактируемый триггер, при зтом третьи входы реверсивньк счетчиков соединены с выходом второго формирова-.: -, теля импульсов через управляемый коммутатор , к другим входам которого подключены соответственно выход второго формирователя импульсов через дополнительньй блок задежки, прямой и инверсный выходы тактируемого триггера, причем первый вход фазосдвигающего блока подключен к входу опорной частоты второго формирователя импульсов, второй вход объединен с входом формирователя входного сигнала,а инверсный вькод такттиру ёмо го триггера подключен к другому входу трактируемого триггера. На чертеже представлена структурная электрическая схема предложенного цифрового некогерентного дискриминатора задержки псевдослучайного радиосигнала. Цифровой некогерентный дискриминатор задержки псевдослучайного радиосигнала содержит формирователь t входного сигнала, первый и второй перемножители 2 и 3, реверсивные счетчики 4 и 5, Отробирующие блоки 6 и 7, вычитающий блок 8, блок 9 задержки, формирователи 10 и 11 ш пульсов, опорный генератор 12, состоящий из двух делителей 13 и 14 частоты, третьего и четвертого перемножителей 15 и 16, регистра 17 сдвига с обратными связями и злемента И 18, а также фаэосдвигающий блок 19, тактируемый триггер 20, управляемый коммутатор 21, состоящий из ключей 22 и 23 и элемента ИЛИ 24, и дополнительный блок 25 задержки.

Цифровой некогерентный дискриминатор работает следующим образом.

На вход поступает«псевдослучайный радиосигнал, представлякмдий собой гармоническое колебание, манипулированное по фазе двоичной псевдослучайной последовательностью (ПСП). Этот сигнал проходит через формирователь 1 входного сигнала, который может быть вьшолнен, например, в виде жесткого ограничителя. Образованный при этом сигнал, называемый клилпированным, поступает на первые входы первого и второго перемножителей 2 и 3 соответственно. На другие входы первого и второго перемножителей 2 и 3 подается опорный клиппированный сигнал, полученный при перемножении опорных последовательностей каналов отставания и опережения, подаваемых на первые ходы третьего и четвертого перемножителей 15 и 16, на вторые входы которых поступает опорный .меандр от делителя 13 частоты. Этот меандр формируется путем деления частоты опорного синхросигнала, подаваемого на вход,и имеющего вид меандра, делителем 13 частоты. В рассматриваемом примере частота опорного синх росигнала f. 4F и .делитель 13 частоты имеет коэффициент деления N1 2, в результате чего частота опорного меандра р| 2F . Выходные сигналы третьего и четвертого перемножителей 15 и 16 представляют Собо клиппированные опорные радиосигналы. После перемножения в первом и втором перемножителях 2 и 3 клиппированного входного псевдослучайного радиосигнала с опорными клиппированными псевдослучайными радиосигналами каналов отставания и опережения, поступающим и от третьо.го и четвертого перемножителей 15 и 16 соответственно, получаются два сигнала,управления , которые прдаются на управляющие входы реверсивных счетчиков 4 и 5 соответственно. Эти сигналы служат для управления направлением счета счетных импульсов, подаваемых на счетные входы реверсивных счетчиков 4 и 5. Счетные импульсы образуются из опорного синхросигнала, который проходит через формирователь 11 импульсов. В формирователе 11 импульсов производится формирование коротких счетных импуль :ов из опорного синхросигнала, так что частота следования счетных импульсов cu

В реверсивных счетчиках 4 и 5 производится накопление счетных импульсов, поступающих от формирователя 11 в течение периода опорной ПСП. Знак каждого накапливаемого счетного импульса при этом определяется полярностью направления, подаваемого на управляющий вход реверсивного счетчика 4 или 5. По завершении периода ПСП в реверсивных счетчиках 4 и 5 будут накоплены числа.

По завершении периода ПСП во всех разрядах регистра 17 сдвига с обратньми связями с.одержатся единицы, в результате чего на выходе элемента И 18 появляется нулевое напряжение. В момент появления этого напряжения формирователь 10 импульсов выдает импульс, поступающий на управляющие входы (входы открывания) стробирующих блоков 6 и 7, которые пропускают содержимое реверсивных счетчиков 4 и 5 на входы сложения и вычитания вычитающего блока 8 соответственно. Существенным является то что из реверсивных счетчиков 4 и-5 в вычитающий бяок 8 переписывается содержимое без знака, т.е. в вычитающем блоке 8 выполняется операция вычитания модуля числа, занесенного в реверсивный счетчик 5, из модуля числа, занесенного в реверсивный счетчик 4i

; Et (l4-V(..

Операции переписи и вычитания могут быть выполнены в параллельной или последовательной форме. После ne реписи содержимого реверсивных счетчиков 4 и 5 в вычитающий блок 8 на входы, сброса этих реверсивных счетчиков 4 и 5 поступает короткий кпульс от блока 9 задержки, который устанавливает реверсивные счетчики 4 и 5в нулевое состояние, и весь цикл работы цифрового некогерентного дискриминатора повторяется снова. Для обеспечения несмещенности оценки з.адержки, образуемой некогерентным дискриминатором, необходимо, Чтобы перепись содержимого реверсивных

счетчиков 4 и 5 и их установка в нулевое состояние производились за время, меньшее периода следования СЧЁТНЫХ импулвсов.

При совпадении счетных импульсов (частота 4Р ) с моментом изменения фазы клиппированного входного сигнала на входе реверсивных счетчиков 4 и 5 возникает неоднозначность или потеря отсчетов, записанных в реверсивном счетчике. Такое попожекие счетных импульсов относительно входного клиппированного сигнала соответствует моменту совпадения фаз входного и опорного синхросигнала. При этом в фазосдвигающем блоке 19 вырабатывается импульс, соответствующий моменту совпадения фаз сравниваемых сигналов. Этот имг1ульс, поступая на счетный вход, перекрывает тактйруемьй триггер 20.

. Пусть в начальный момент тактируемый триггер 20 находится в единичном состоянии, тогда ключ 22 открыт, а ключ 23 закрыт, и счетные импульсы от формирователя 11 импульсов через открытый ключ 22 и элемент ИЖ 24 поступают на третий вход реверсивных счетчиков 4 и 5. При поступлении очередного импульса с выхода фазосдвигающего блока 19 тактируемый триггер 20 переключается, при этом ключ 22 закрывается, ключ 23 откры.вается, тогда на третьи входы реверсивных счетчиков 4 и 5 поступают счетные импульсы, задержанные в дополнительном блоке 25 задержки на величину, равную г /2 входного клиппированного сигнала.

Таким образом, введение в известньй цифровой некогерентный дискриминатор новых элементов позволяет исключить сбои в работе цифрового некогерентного дискриминатора из-за совпадения временного положения счетных импульсов с моментом перехода фазы входного сигнала. В результате повьшается устойчивость и точность работы цифрового некогерентного дискриминатора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой некогерентный дискриминатор задержки псевдослучайного радиосигнала | 1978 |

|

SU726671A1 |

| АДАПТИВНЫЙ ЦИФРОВОЙ ЧАСТОТНЫЙ ДИСКРИМИНАТОР | 2000 |

|

RU2166773C1 |

| ЦИФРОВОЙ ЧАСТОТНЫЙ ДИСКРИМИНАТОР | 1991 |

|

RU2040852C1 |

| Следящий фильтр фазоманипулированного псевдослучайного сигнала | 1982 |

|

SU1072252A1 |

| Цифроаналоговое устройство слежения за задержкой псевдослучайной последовательности импульсов | 1982 |

|

SU1083390A1 |

| Многоканальное устройство для управ-лЕНия -фАзНыМ иНВЕРТОРОМ | 1979 |

|

SU813669A1 |

| Устройство тактовой синхронизации псевдослучайных последовательностей | 1983 |

|

SU1092744A1 |

| Генератор последовательности импульсов | 1983 |

|

SU1192120A1 |

| Устройство для приема сигналов с относительной фазовой модуляцией | 1989 |

|

SU1635278A1 |

| Цифровое устройство для слежения за задержкой псевдослучайной последовательности | 1978 |

|

SU999172A1 |

ЦИФРОВОЙ НЕКОГЕРЕНТНЫЙ ДИСКРИМИНАТОР ЗАДЕРЖКИ ПСЕВДОСЛУЧАЙНОГО РАДИОСИГНАЛА по авт.св. 72667Ь отличающийся тем, что, с целью повышения точности путем исключения сбоев в работе дискриминатора при совпадении счетных импульсов с моментами изменения фазы входного сигнала, в него введены дополнительный блок задержки, управляемый коммутатор и последовательно соединенные фазосдвигающий блок и тактируемый триггер, приэтом третьи входы реверсивных счетчиков соединены с выходом второго формирователя импульсов через управляемый коммутатор к другим входам которого подключены соответственно выход второго формирователя импуль-сов через дополнительный блок задержки, прямой и инверсный выходы тактируемого триггера, причем первый вход фазосдвигающего блока подключен к входу опорной частоты второго формирователя импульсов, второй вход 9 объединен с входом формирователя входного, сигнала, a инверсный выход тактируемого триггера подключен к другому входу тактируемого триггера.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Цифровой некогерентный дискриминатор задержки псевдослучайного радиосигнала | 1978 |

|

SU726671A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1984-12-23—Публикация

1983-04-07—Подача