рователь импульсов, два элемента ИЛИ, три элемента И, причем первый вход первого дополнительного элемента ИЛИ соединен с входом уста- . новки в положение 1 второго триггера, второй вход - с выходом первого дополнительного цифрового компаратора и первым входом первого дополнительного счетчика, а выход - с первым входом первого дополнительного элемента И, второй вход которого соеди-нен с первым выходом дополнительного триггера и с первым входом второго дополнительного элемента И, а выход - с первым входом второго дополнительного элемента ИЛИ, второй вход которого соединен с выходом первого элемента И а выход - с четвертым входом блока переключения, второй выход дополнительного триггера соединен с вторым входом первого элемента И, с первым входом третьего дополнительного элемента И и через дополнительный формирователь импульсов с пятой выходной йиной, с первым входом второго дополнительного счетчика импульсов и вторым входом второго элемента ИЛИ, вход установки в О - с выходом фop№ poвaтeля импульсов, а счетный вход - с выходом ц1-1фрового компаратора , второй вход второго дополнительного элемента И соединен с вторым выходом генератора -импульсов и с первым входом третьего дополнительного счетчика импульсов, второй вход которого соединен с выходом второго дополнительного цифрового компаратора и вторым входом третьего дополнительного элемента И, а выход с первым входом второго дополнительного, цифрового компаратора, второй вход которого соединен с вторым выходом блока задания цифровой апертуры, второй вход второго дополнительного счетчика импульсов соединен с выходом третьего дополнител1 кого элемента И, а выход - с первым входом первого дополнительного цифрового компаратора, второй вход которого соединен с выходом первого дополнительного счетчика импульсов, второй вход которого соединен Q выходом второго дополнительного элемента И,

| название | год | авторы | номер документа |

|---|---|---|---|

| Система для передачи телеизмерительной информации | 1982 |

|

SU1113832A1 |

| Адаптивный аналого-цифровой преобразователь | 1982 |

|

SU1051703A1 |

| Система для передачи телеизмерительной информации | 1981 |

|

SU1023379A2 |

| Адаптивный аналого-цифровой преобразователь | 1979 |

|

SU864552A1 |

| Адаптивный аналого-цифровой преобразователь | 1980 |

|

SU942257A1 |

| Адаптивный аналого-цифровой преобразователь | 1980 |

|

SU875622A1 |

| Система для передачи телеизмерительной информации | 1981 |

|

SU1037313A1 |

| Система для передачи телеизмерительной информации | 1981 |

|

SU1084852A1 |

| Система для передачи телеизмерительной информации | 1981 |

|

SU1056246A1 |

| Устройство для центрирования изображений объектов | 1990 |

|

SU1836697A3 |

АДАПТИВШЙ АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ, содержащий два реверсивных счетчика, регистр сдвига, блок цифрового задания апертуры, блок переключения, цифровой компаратор, блок совпадения нулей, генератор импульсов, блок переноса кода, два триггера, два элемента И, два элемента ИЛИ и формирователь импульсов, блок сдвига совпадающих импульсов, первый вход которого соединен с входной шиной и первым входом регистра сдвига, второй вход которого соединен с первым выходом генератора импульсов и с вторым входом блока сдвига совпадаю1цих импульсов, третий вход которого подключен к выходу регистра сдвига, третий вход которого соединен с шиной с входами установки в О первого и второго триггеров, с первыми входами первого реверсивного счетчика и первого элемента ШШ, второй вход которого соединен с выходом цифрового компаратора, а выход - с первым входом второго реверсивного счетчика, первый выход которого через блок совпадения нулей соединен со счетным входом первого триггера, первой выходной шиной и первьм входом второго элемента ИЛИ, второй выход - с первым входом цифрового компаратора, второй вход которого соединен с первым выходом блока цифрового задания апертуры, выход второго элемента ИЛИ соединен с первым входом блока переноса кода, выход которого соединен с второй йыходной шиной, а второй вход i с выходом первого реверсивного (Л С счетчика, второй вход которого соединен с первым выходом блока сдвига совпадающих импульсов, первым входом первого элемента И и входом установки в положение 1 второго триггера, третий вход - с вторым выходом блока сдвига совпадающих импульсов и первым входом второго элемента И, второй вход котосо 00 рого соединен с выходом второго триггера и входом первого формиросо со вателя импульсов, а выход - с первым входом блока переключения, второй и третий входы которого соединены соответственно с первым и вторым вы} одами первого триггера и с третьей и четвертой выходными шинами, а выходы - с вторым и третьим входами второго реверсивного счетчика, отличающийся тем, что, с целью повьш1ения информативности, в него введены три счетчика импульсов и дополнительно два цифровых компаратора, триггер, форми

Изобретение относится к вычислительной технике и может быть использовано для аффективного сжатия преобразуемой информации.

Известен адаптивный аналого-цифровой преобразователь, содержащий два счетчика, один из которых реверсивный, два блока переноса кода, формирователь временного интервала, элементы совпадения единиц и нулей, два триггера, генератор импульсов, два формирователя импульсов два элемента И, два элемента ИЛИ и блок задержки 3 .

Недостатком преобразователя является низкий коэффициент сжатия информации.

Известен также адаптивный аналого-цифровой преобразователь, содержащий генератор импульсов, блок переноса кода, первый вход которого соединен с выходом первого элемента ИЛИ, а вторые входы - с выходами разрядов первого реверсивного счетчика, первый вход которого соединен с первым входом второго элемента ИЛИ и клеммой Пуск, два

управляюш их триггера, в.ходы установки в О которых соединены с клеммой Пуск, при этом счетный вход первого управляющего триггера соединен с выходом блока совпадения нулей и с первым входом первого элемента ИЛИ, а выход второго управляющего триггера - с первыми входами двух элементов И и входом формирователя импульсов, выход которого соединен с вторым

входом первого элемента ИЛИ, выход второго элемента ИЛИ соединен с первьм входом второго реверсивного счетчика, первые выходы которого соедине(1ы с входами блока совпадения нулей, регистр сдвига, блок цифрового задания апертуры, цифровой компаратор, блок сдвига сов3

падающих икшульсов и блок переключения, при этом входная клемма устройства соединена с первыми входаьм блока сдвига совпадающих импульсов и регистра сдвига, второй вход которого соединен с выходом генератора импульсов и с вторым входом блока сдвига совпадающих импульсов, третий вход которого подключен к выходу регистра сдвига, а два выхода соединены со счетными входами первого реверсивного счетчика и с вторыми входами двух элементов И, выходы которых соединены с информационными входами блока переключения, управляющие входы которого соединены с выходами первого триггера, а вьсходы - с равнозначными счетными входами второго реверсивного счетчика, вторые входы которого соединены с первыми входами цифрового компаратора, вторые входы которого соединены с выходами разрядов блока цифрового задания апертуры, а выход цифрового компаратора - с третьим входом первого элемента ИЛИ и с вторым входом второго элемента ИЛИ, первый выход блока сдвига совпадающих импульсов соединен с единичным входом второго триггера, а клемма Пуск с третьим входом регистра сдвига 2.

Недостатком известного преобразователя является то, что он реализует принцип адаптивного сжатия информации с помощью экстраполятора нулевого порядка, поэтому имеет невысокий коэффициент сжатия, особенно для преобразования процессов, имеющих участки с изменением параметра, близкого к линейному. К таким процессам относится вертикальная структура изменения температуры в морях и океанах с явно выраженным линейным участком термоклина (слой скачка температуры). Так как на этом участке отмечается резкое изменение температуры, иногда достигающее 1,5 С/м, то известный преобразователь формирует много лишних отсчетов практически при изменении глубины в пределах погрешности измерителя глубины, что усложняет восстановление структуры и собирает большой объем излишней информации.

Цель изобретения - повьппенйе информативности устройства.

098994

. Поставлерсная цель достигается тем, что в адаптивный аналого-цифровой преобразователь, содержащий два реверсивных счетчиКа, регистр 5 сдвига, блок цифрового задания апертуры, блок переключения, цифровой компаратор, блок совпадения нулей, генератор и тульсов, блок переноса кода, два триггера, два элемента И,

)0 два элемента ИЛИ, формирователь импульсов, блок сдвига совпадающих импульсов, первый вход которого соединен с входной щиной и первым вхюдом регистра сдвига, второй вход

15 которого соединен с первым выходом генератора импульсов и с вторым входом блока сдвига совпадающих импульсов, третий вход которого соединен с выходом регистра сдвига,

20 третий вход которого соединен с шиной Пуск преобразователя и с входа ми установки в О первого и второго триггеров, с первыми входами первого реверсивного счетчика и пер25 вого элемента ИЛИ, второй вход кото, рого соединен с выходом цифрового компаратора, а выход - с первым входом второго реверсивного счетчика, первый выход которого через блок

30 совпадения нулей соединен со счетным входом первого триггера, первой; выходной шиной и первым входом второго элемента НИИ, второй выход - с первым входом цифрового компаратора, второй вход которого соединен с

35 первым выходом блока цифрового задания апертуры, выход второго элемента ИШ соединен с первым входом блока переноса кода, выход которого

. соединен с второй выходной шиной,

40

а второй вход - с выходом первого реверсивного счетчика, второй вход которого соединен с первым выходом блока сдвига совпадающих импульсов, первым входом первого элемента И и входом установки в положение 1 второго триггера, третий вход с вторым выходом блока сдвига совпадающих импульсов и первым входом

второго элемента И, второй вход которого соединен с выходом второго триггера и входом первого формирователя импульсов, а выход - с первым входом блока переключения, второй и третий входы которого соединены соответственно с первым и вторым выходами первого триггера и с третьей и четвертой выходными шинами, а выходы - с вторым и третьим

входами второго реверсивного счетчика ввелены три счетчика и fflyльcGB и дополнитель}ю два цифровых компаратора, триггер, ерормироватепь импульсов5 два элемента ИЛИ, три элемента Из-причем лервьгй вход первого дополнительЕюго элемента ИШ соединен с входом установки в положение 1 второго триггера, второй вход - с выходом первого дополнител кого Цифрового компаратора и первым входом первого дополнительного счетчика, а вькод - с первым входом первого дополнительпого элемента И, второй вход которого соединен с первьм выходом дополпр5тельного триггера и с первым входом второго допол нительгюго элемента И, а выход с первым входом второго дополнительного элемента ШК, второй вход которого соединен с вькодом первого элемента И, а выход -- с четвертым входом блока перегсчючения,) второй выход дополнительгюго триггера соединен с вторым входом первого элемента И, с йервым входом третх его дополнительного элемента И и через дополнительный форг--шрователь импульсов с пятой выходной шиной, с первым входом второго дополнительного счетчика импульсов к вторым входом второго элем2 ;та ИЖ 5 вход установки в О - с выходом формирователя импульсов5 а счетный вход с выходом 1ЩФРОВОГО компаратора, второй вход второго дополнительноГО элемента И соединен с выходом генератора импульсов и с; первым входом peibero дополнительного п тульсовэ второй вхо которого соединен с выходом второго дополиителт.пого цифрового комnapaTOja и вторым входом третьего дополнительпого элемента И а выход с первым входом второго дополнительного цифрового компаратора,, второй вход которого соединен с вторым вькодоь блока задания цифровой апертлфы; второй вход второго дополнительного счетчика импульсов соединен с выводом третьего дополнительного элемспта И, а выход - с первым входом первого дополннтельного цифрового компаратораj второй вход которого ;оединен с выходом первого дополнительного счетчика иь/тульсов, второй вход которого соединен с выходом второго дополнительного элемента И,

98996

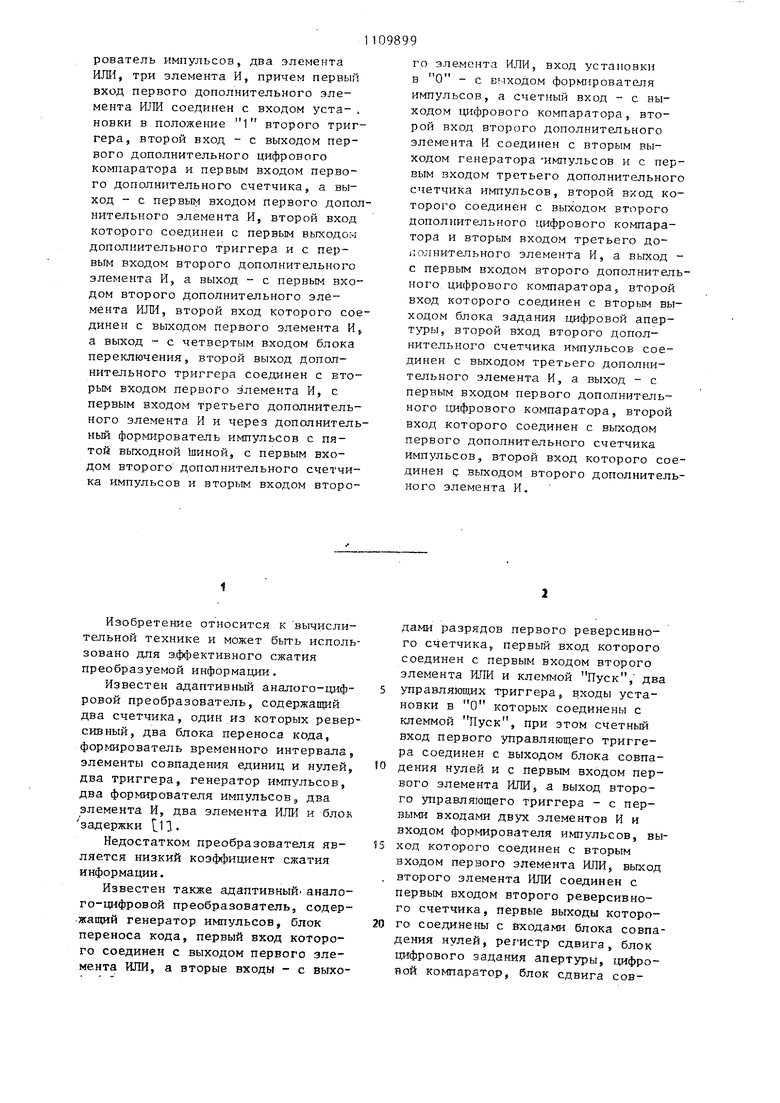

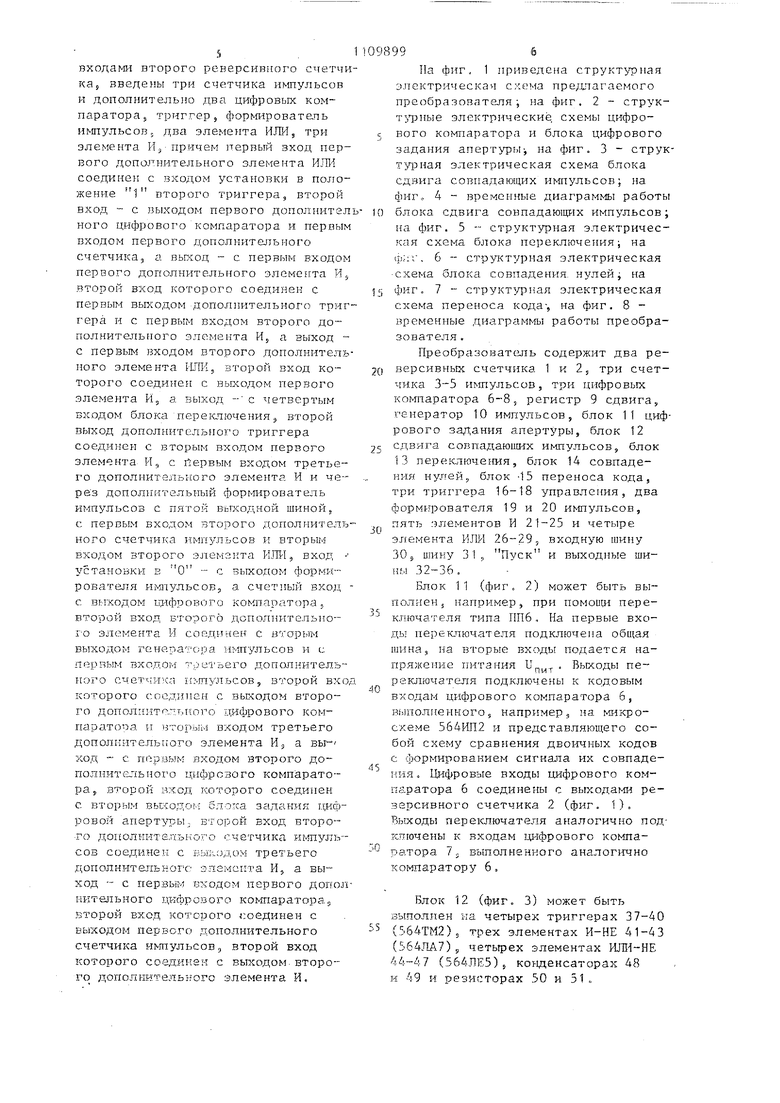

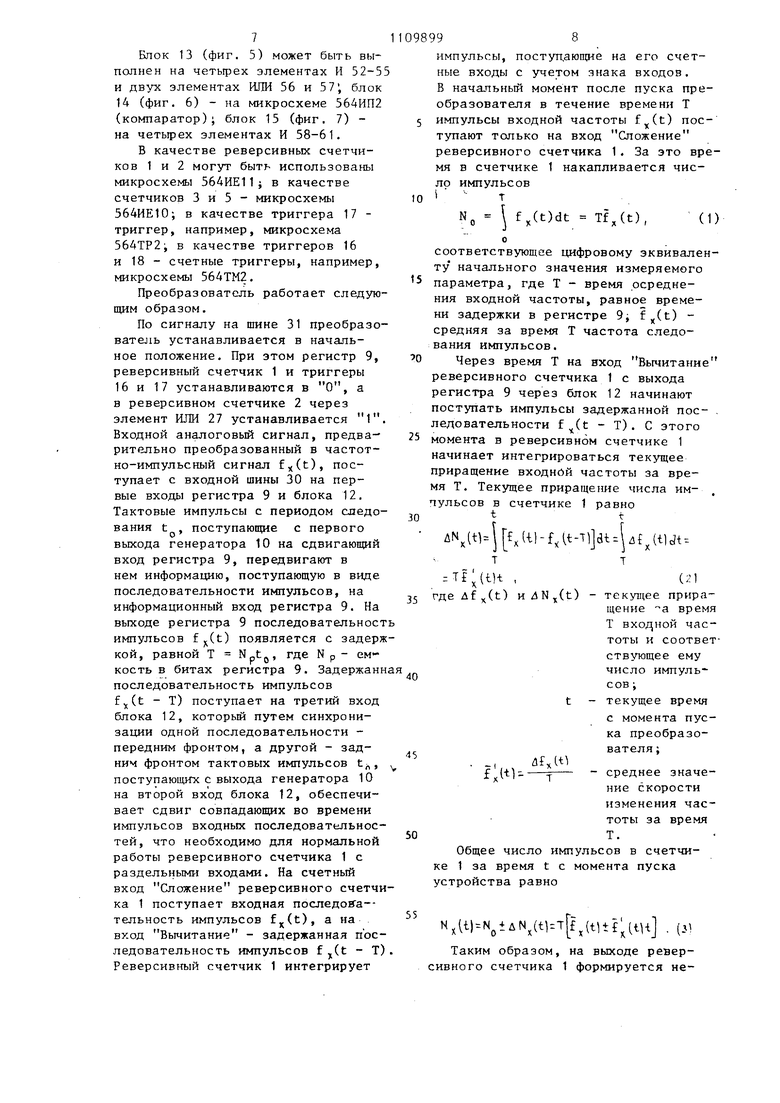

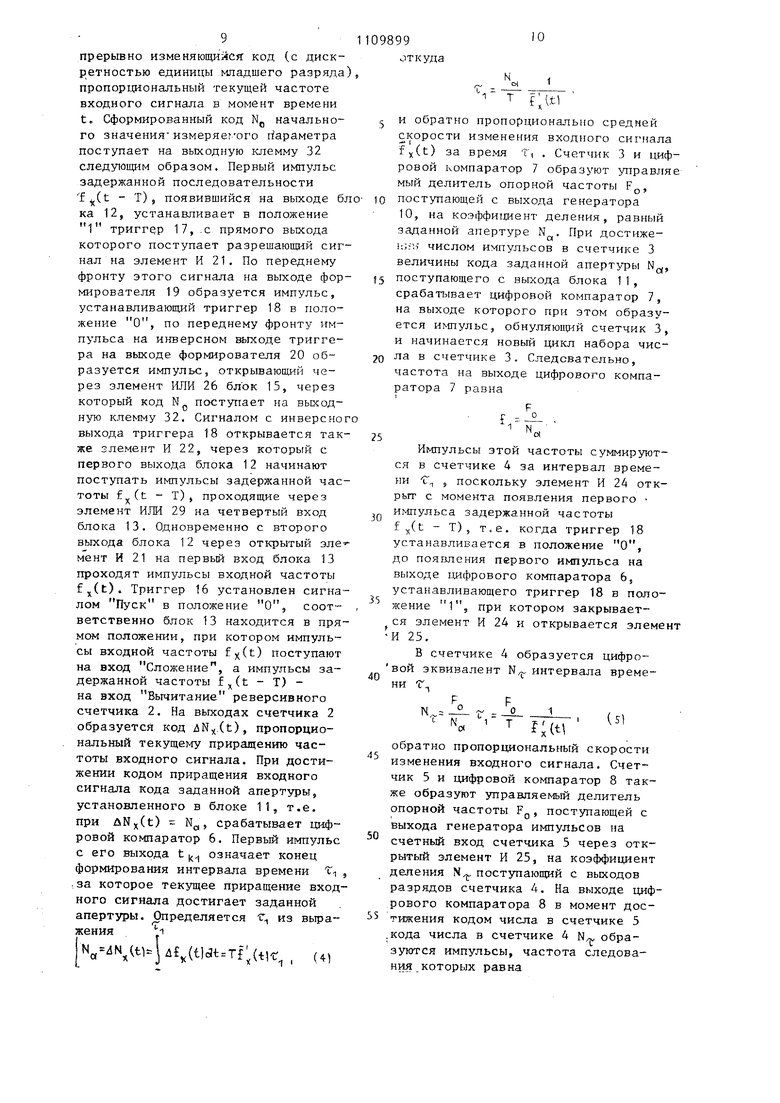

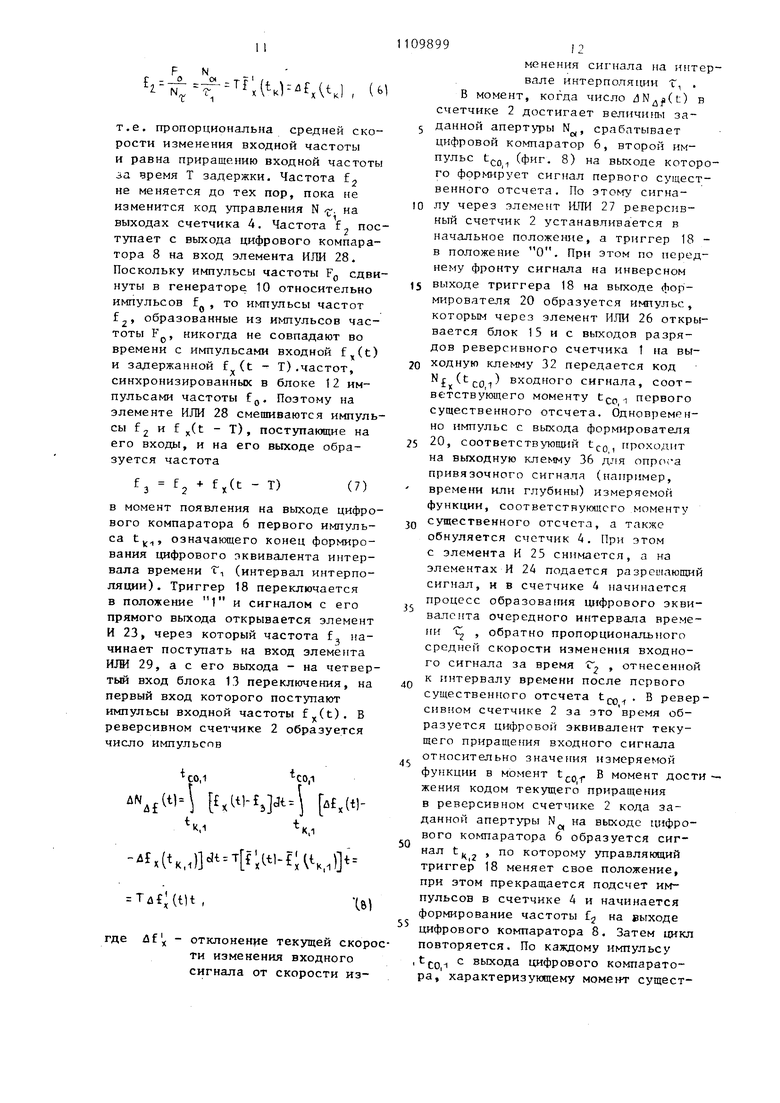

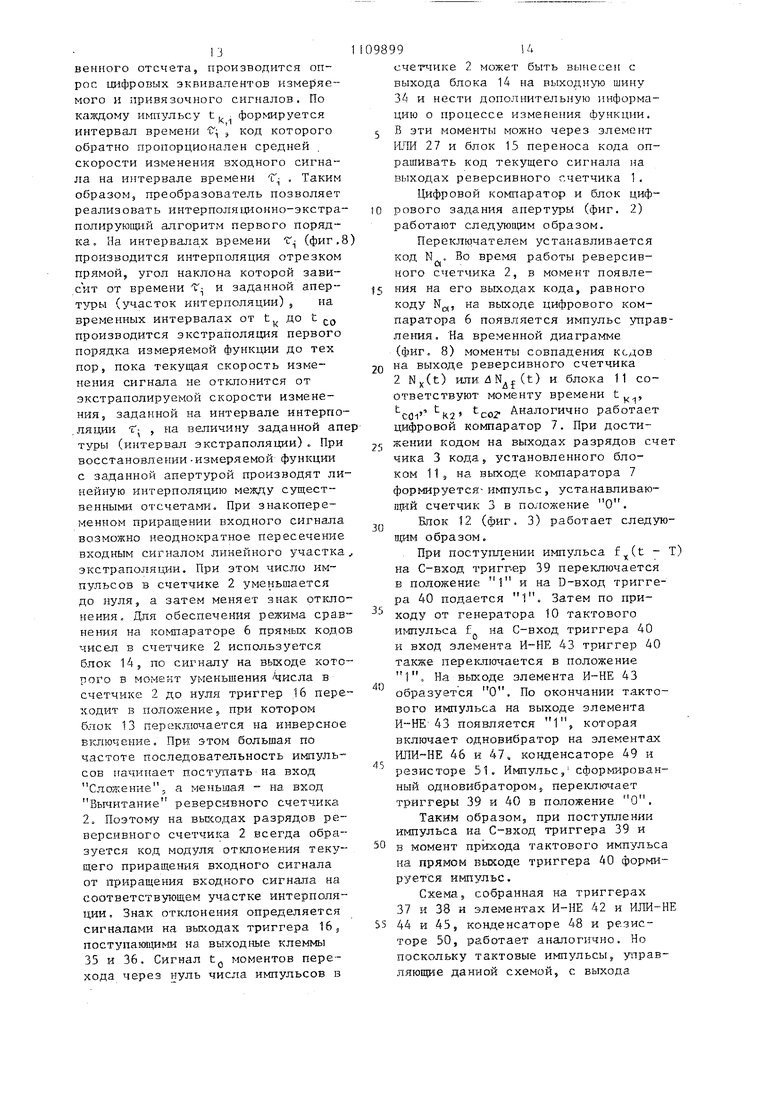

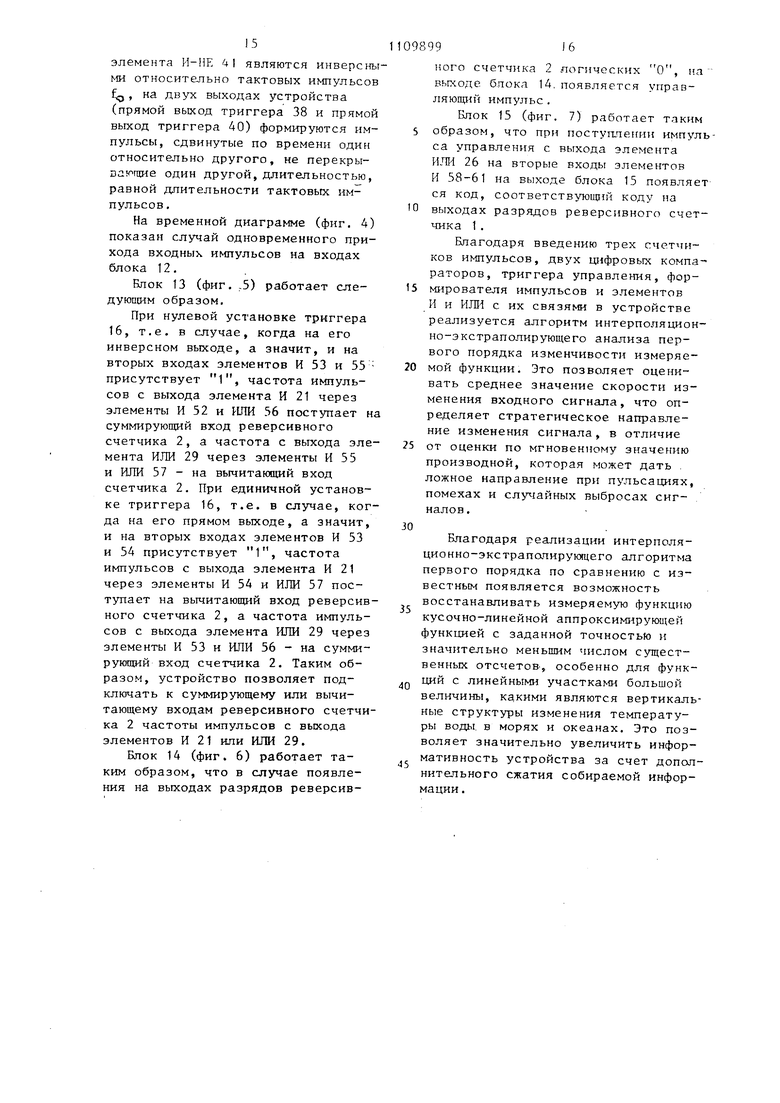

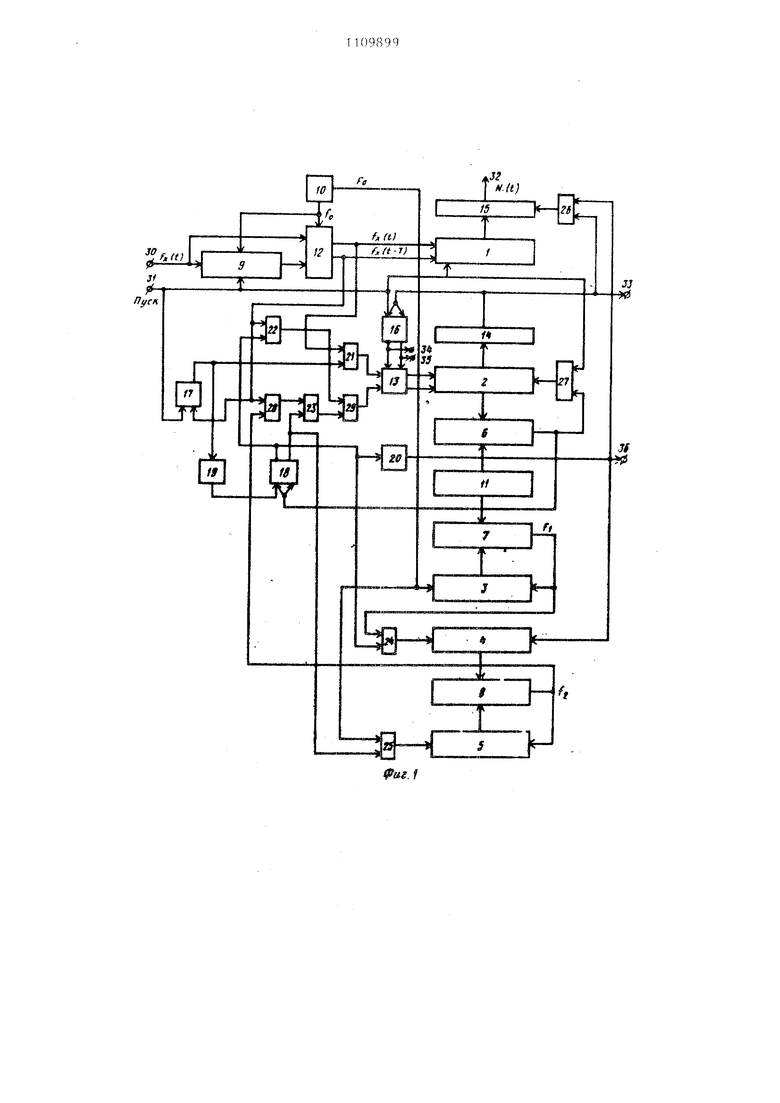

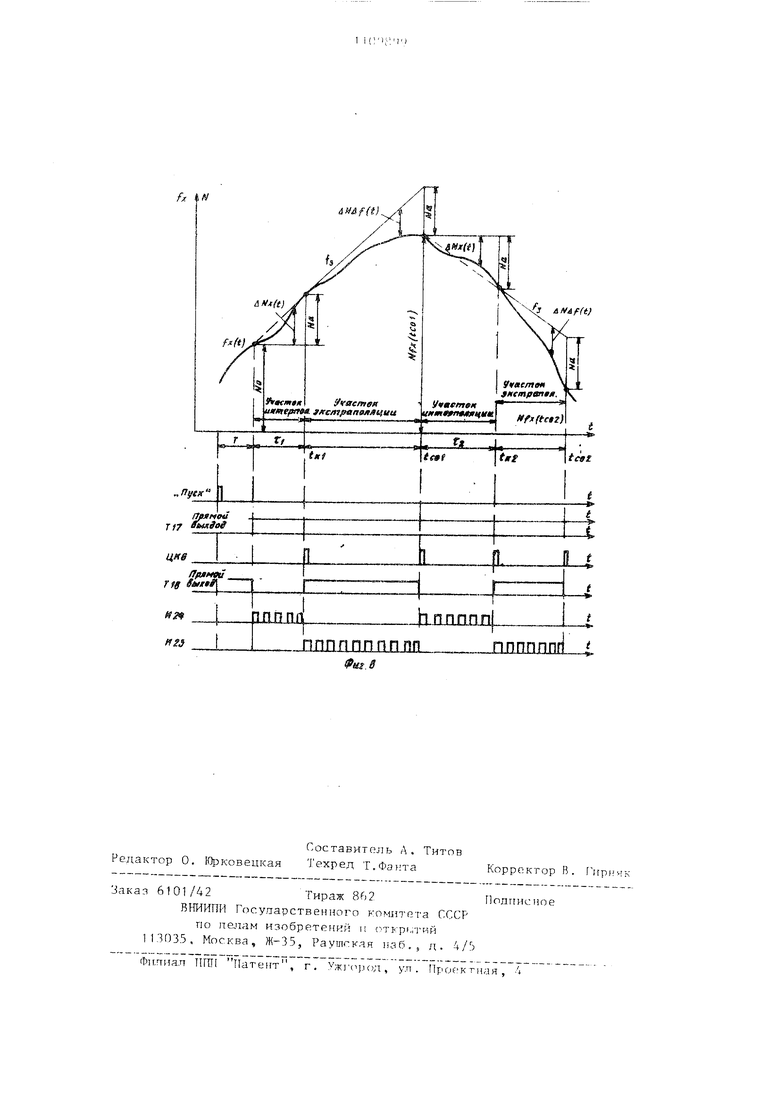

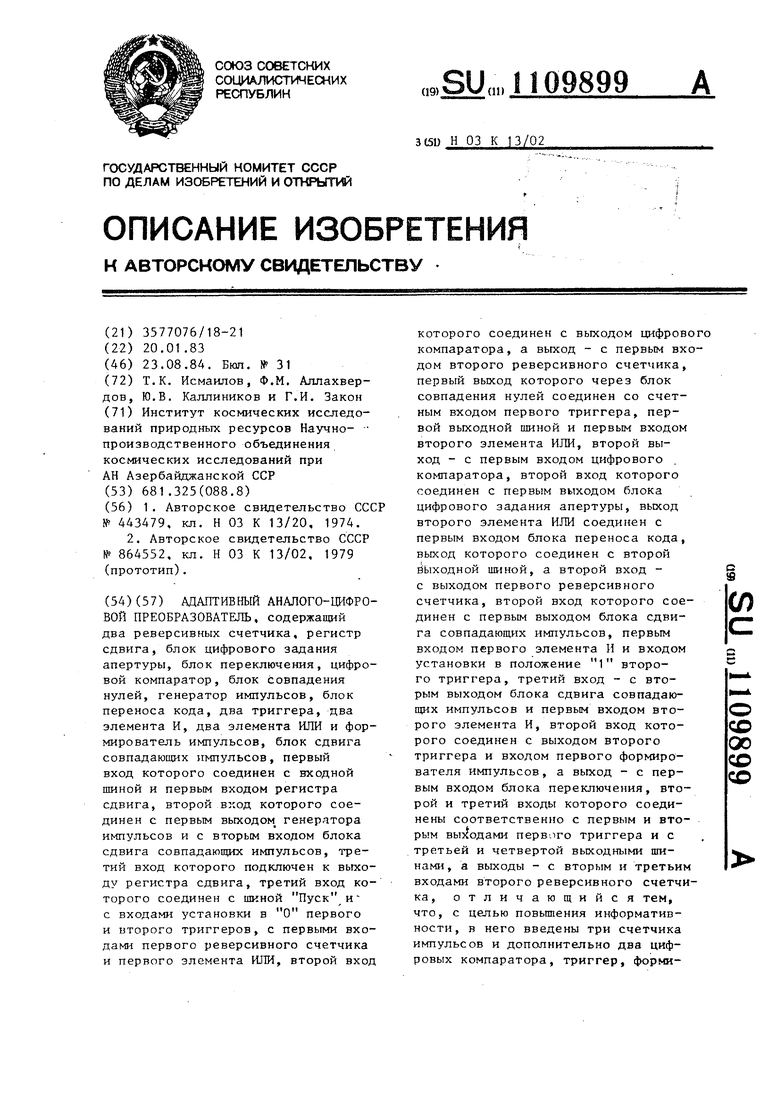

Па фиг, 1 приведена структ тэная электрическая схема предлагаемого преобразователя 5 на фиг. 2 - струкT;,T3Hbie электрические, схемы цифрового компаратора и блока цифрового задания апертуры на фиг. 3 - структ;л ная электрическая схема блока сдвига совпадающих импульсов; на dn-ir., 4 - временные диаграммы работы 10 блока сдвига совпадаю1цих импульсов; на фиг. 5 - структурная электрическая схема блока переключения; на (р;;г, 6 - структурная электрическая схема блока совпадения, нулей j на

js: фиг. 7 - структурная электрическая схема переноса кода-, на фиг, 8 временные диаграммы pa6oTiji преобразователя .

Преобразователь содержит два ре20 версивньЕх счетчика 1 и 2, три счетчика 3-5 импульсов, три цифровых ког-таратора 6-8,, регистр 9 сдвига, генератор 10 импульсов, блок 11 цифрового задания апертуры, блок 12

сдвига совпадающих импульсов, блок 13 переключения, блок 14 совпадения нулей, блок -15 пе1)еноса кода, три триггера 16-18 управления, два формрфователя 19 и 20 импульсов, пять элементов И 21-25 и четыре элемента ИЛИ 26-29; входн-зю шину 30 5 цину 315 Пуск и выходные шины 32-36,

Блок 11 (фиг, 2) может быть выполнен; например, при помощи переключателя типа ППб. На первые входь; переключателя подключена общая щ-ина, на вторые входы подается напряжение питания и,-| , Выходы переключателя подключены к кодовым входам цифрового компаратора 6, выполненного, HanpisMep, на микросхеме 564ИП2 и представляющего собой схему сравнения двоичных кодов с формированием сигнала их совпаде ПИЯ. Цифровые входы цифрового компаратора 6 соединены с выходами реверсивного счетчика 2 (фиг. 1). Выходы пере1спючателя аналогично подключены к входам цифрового компа-- ратора 7, выполненного аналогично компаратору 6.

Блок 12 (фиг. 3) может быть в-з1полпен ка четырех триггерах 37-40 55 (564ТМ2)5 трех элементах И-НЕ 41-43 (564ЛА7) 5 четырех элементах ШШ-НЕ 44-47 (564ЛЕ5)5 конденсаторах 48 и 49 и резисторах 50 и 51„

7

Блок 13 (фиг. 5) может быть выполнен на четырех элементах И 52-5 и двух элементах ИЛИ 56 и 57, блок 14 (фиг. 6) - на микросхеме 564ИП2 (компаратор); блок 15 (фиг. 7) на четьфех элементах И 58-61.

В качестве реверсивных счетчиков 1 и 2 могут бытъ использованы микросхемы 564ИЕ11j в качестве счетчиков 3 и 5 - микросхемы 564ИЕ10; в качестве триггера 17 триггер, например, микросхема 564TP2j в качестве триггеров 16 и 18 - счетные триггеры, например, микросхемы 564ТМ2.

Преобразователь работает следующим образом.

По сигналу на шине 31 преобразователь устанавливается в начальное положение. При этом регистр 9, реверсивный счетчик 1 и триггеры 16 и 17 устанавливаются в О, а в реверсивном счетчике 2 через элемент ИЛИ 27 устанавливается 1 Входной аналоговый сигнал, предварительно преобразованный в частотно-импульсный сигнал f(t), поступает с входной шины 30 на первые входы регистра 9 и блока 12. Тактовые импульсы с периодом следования t , поступающие с первого выхода генератора 10 на сдвигающий вход регистра 9, передвигают в нем информацию, поступающую в виде последовательности импульсов, на информационный вход регистра 9. На выходе регистра 9 последовательност импульсов f,(t) появляется с задержЛ

кой, равной Т Nptg, где N р - ем«кость в битах регистра 9. Задержанн последовательность импульсов f(t - Т) поступает на третий вход блока 12, который путем синхронизации одной последовательности передним фронтом, а другой - задним фронтом тактовых импульсов t,, поступающих с выхода генератора 10 на второй вход блока 12, обеспечивает сдвиг совпадающих во времени импульсов входных последовательностей, что необходимо для нормальной работы реверсивного счетчика 1 с раздельными входами. На счетный вход Сложение реверсивного счетчика 1 поступает входная последояа-тельность импульсов f(t), а на вход Вычитание - задержанная последовательность импульсов f j(t - Т) Реверсивный счетчик 1 интегрирует

09899

импульсы, постудаюп(ие на его счетные входы с учетом знака входов. В начальный момент после пуска преобразователя в течение времени Т импульсы входной частоты f(t) поступают только на вход Сложение реверсивного счетчика 1. За это время в счетчике 1 накапливается число импульсов i - т

f,(t)dt Tf,(t),

(1)

соответствующее цифровому эквиваленту начального значения измеряемого параметра, где Т - время осреднения входной частоты, равное времени задержки в регистре 9 f - средняя за время Т частота следования импульсов.

Через время Т на вход Вычитание реверсивного счетчика 1 с выхода регистра 9 через блок 12 начинают поступать импульсы задержанной пос- , ледовательности f(t - Т). С этого момента в реверсивном счетчике 1 начинает интегрироваться текущее приращение входной частоты за время Т. Текущее приращение числа имтульсов в счетчике 1 равно tt

(l-f..4f(tldt-Т (t)t

Т

.;

me Afx(t) (t) - TCKyniee приращение -a время Т входной частоты и соответствующее ему число импуль сов ;

t - текущее время с момента пуска преобразователя;

af.U

- среднее значение скорости изменения частоты за время Т.

Общее число импульсов в счетчике 1 за время t с момента пуска устройства равно

N,lt)(tl--T(tlt(tH . (31

Таким образом, на выходе реверсивного счетчика 1 формируется не9прерывно изменяющимсяг код (с дискретностью единицы младшего разряда пропорциональный текущей частоте входного сигнала в момент времени t. Сформированный код N начального значения-измеряемого riapaMeTpa поступает на выходную клемму 32 следующим образом. Первый импульс задержанной последовательности f (t - т) j появившийся на выходе б ка 12, устанавливает в положение 1 триггер 17, -С прямого выхода которого поступает разрешающий сиг нал на элемент И 21. По переднему фронту этого сигнала на выходе фор мирователя 19 образуется импульс, устанавливающий триггер 18 в положение О, по переднему фронту импульса на инверсном выходе триггера на выходе формирователя 20 образуется импульс, открывающий через элемент ИЛИ 26 блок 15, через который код NP поступает на выходную клемму 32. Сигналом с инверсно выхода триггера 18 открывается так же элемент И 22, через который с первого выхода блока 12 начинают поступать импульсы задержанной час тоты f(t - Т), проходящие через элемент ИЛИ 29 на четвертый вход блока 13. Одновременно с второго выхода блока 12 через открытый эле мент И 21 на первьй вход блока 13 проходят импульсы входной частоты f(t). Триггер 16 установлен сигна лом Пуск в положение О, соответственно блок 13 находится в пря мом положении, при котором импульсы входной частоты f j({t) поступают на вход Сложение, а импульсы задержанной частоты - Т) на вход Вычитание реверсивного счетчика 2. На выходах счетчика 2 образуется код 4N.(t), пропорциональный текущему приращению частоты входного сигнала. При достижении кодом приращения входного сигнала кода заданной апертуры, установленного в блоке 11, т.е. при uN)(t) NQ , срабатывает цифровой компаратор 6. Первый импульс с его выхода t означает конец формирования интервала времени Т ,за которое текущее приращение вход ного сигнала достигает заданной апертуры. Определяется т из выраженияN,aN(t1.J4f(t)a-Tf;(tK 99 откуда и обратно пропорционально средней скорости изменения входного сигнала fx(t) за время Т, . Счетчик 3 и цифровой компаратор 7 образуют управ гяе мый делитель опорной частоты F, поступающей с выхода генератора 10, на коэффициент деления, равный заданной апертуре N. При достижеlc,i ЧИСЛОМ импульсов в счетчике 3 величины кода заданной апертуры N,, поступающего с выхода блока 11, срабаттз1вает цифровой компаратор 7, на выходе которого при этом образуется импульс, обнуляющий счетчик 3, и начинается новый цикл набора числа в счетчике 3. Следовательно, частота на выходе цифрового компаратора 7 равна 1 Импульсы этой частоты суммируются в счетчике 4 за интервал времени С , поскольку элемент И 24 открьгг с момента появления первого и тульса задержанной частоты (t - т)J т.е. когда триггер 18 устанавливается в положение О, до появления первого импульса на выходе цифрового компаратора 6, устанавливающего триггер 18 в положение I, при котором закрывается элемент И 24 и открывается элемент И 25. В счетчике 4 образуется цифровой эквивалент N -интервала времеN. v -« . f;w обратно пропорциональный скорости изменения входного сигнала. Счетчик 5 и цифровой компаратор 8 также образуют управляеьФш делитель опорной частоты F, поступающей с выхода генератора импульсов на счетный вход счетчика 5 через открытый элемент И 25, на коэффициент деления N поступающий с выходов разрядов счетчика 4. На выходе цифрового компаратора 8 в момент достижения кодом числа в счетчике 5 кода числа в счетчике 4 N образуются импульсы, частота следования которых равна M4)fx( т.е. пропорциональна средней ско рости изменения входной частоты и равна приращению входной частоты за чремя Т задержки. Частота fj не меняется до тех пор, пока не изменится код управления N -j. на выходах счетчика 4. Частота f пос тупает с выхода цифрового компаратора 8 на вход элемента ИЛИ 28. Поскольку игчпульсы частоты F сдви нуты в генераторе 10 относительно импульсов f , то импульсы частот f , образованные из импульсов частоты Fp, никогда не совпадают во времени с импульсами входной f(t и задержанной f (t - Т).частот, синхронизированных в блоке 12 импульсами частоты fp. Поэтому на элементе ИЛИ 28 смешиваются импуль сы f и f (t - т), поступающие на его входы, и на его выходе образуется частота 5з f f,(t - Т) в момент появления на выходе цифро вого компаратора 6 первого импульса t, означающего конец формирования цифрового эквивалента интервала времени Т (интервал интерполяции). Триггер 18 переключается в положение 1 и сигналом с его прямого выхода открывается элемент И 23, через который частота f начинает поступать на вход элемента ИЛИ 29, а с его выхода - на четвер тый вход блока 13 переключения, на первый вход которого поступают импульсы входной частоты f(t). В реверсивном счетчике 2 образуется число импульсов Чо,140,1 ( , .W-(tK,i),.) Tdf(t)t где - отклонение текущей ско ти изменения входного сигнала от скорости изменения сигнала на HFiTepвале интерполяции Т, . В момент, когда число (t) в счетчике 2 достигает величию заданной апертуры N, срабатывает цифровой кo пapaтop 6, второй импульс t(4Q (фиг. 8) на выходе которого формирует сигнал первого сущест;венного отсчета. По этому сигналу через элемент ИШ 27 реверсивный счетчик 2 устанавливается в начальное положение, а триггер 18 в положение О. При этом по переднему фронту сигнала на инверсном выходе триггера 18 на выходе формирователя 20 образуется импульс, которым через элемент ИЛИ 26 открывается блок 15 и с выходов разрядов реверсивного счетчика 1 на выходную клемму 32 передается код N (tcoi- входного сигнала, соответствующего моменту ССР 1 первого существенного отсчета. Одновременно импульс с выхода формирователя 20, соответствующий t(-Q проходит на выходную клеьа у 36 для опрги-а привязочного сигналя (например, времени или глубины) измеряемой функции, соответствующего моменту существенного отсчета, а также обнуляется счетчик Д. При этом с элемента И 25 снимается, а на элементах И 24 подается разреичающий сигнал, и в счетчике 4 начинается процесс образования цифрового эквивалента очередного интервала времени i , обратно пропорционального средней скорости изменения входного сигнала за время Т , отнесенной к интервалу времени после первого существенрюго отсчета . В реверcneiioM счетчике 2 за это время образуется цифровой эквивалент текущего приращения входного сигнала относительно значения измеряемой функции в момент tj- В момент дости жения кодом текущего приращения в реверсивном счетчике 2 кода заданной апертуры N на вьгходс цифрового компаратора 6 образуется сигнал t.., , по которому управляющий триггер 18 меняет свое положение, при этом прекращается подсчет импульсов в счетчике А и начинается формирование частоты fj на выходе цифрового компаратора 8. Затем цикл повторяется. По каждому импульсу tj.Q с выхода цифрового компаратора, характеризующему момент сущест13

венного отсчета, производится опрос цифровых эквивалентов измеряемого и привязочного сигналов. По каждому импульсу t,., формируется интервал времени V: , код которого обратно пропорционален средней скорости изменения входного сигнаТаким

ла на интервале времени

образом, преобразователь позволяет реализовать интерполяционно-экстраполирующий алгоритм первого порядка. На интервалах времени V (фиг,8 производится интерполяция отрезком прямой, угол наклона которой зависит от времени f и заданной апертуры (участок интерполяции) на временных интервалах от t до t . производится экстраполяция первого порядка измеряемой функции до тех пор, пока текущая скорость изменения сигнала не отклонится от экстраполируемой скорости изменения, заданной на интервале интерпо,ляции Т- , на величину заданной ап туры (интервал экстраполяции)„ При восстановлении-измеряемой функции с заданной апертурой производят линейную интерполяцию между существенными отсчетами. При знакопеременном приращении входного сигнала возможно неоднократное пересечение входным сигналом линейного участка экстраполятдии. При этом число импульсов в счетчике 2 уменьшается до нуля, а затем меняет знак отклонения. Для обеспечения режима сра.внения на KONraapaTOpe 6 прямых кодо чисел в счетчике 2 используется блок 14, по сигналу на выходе которого в момент уменьшения числа в счетчике 2 до нуля триггер 16 переходит в положение j при котором блок 13 перекл1сгаается на инверсное включение. При этом большая по частоте последовательность импульсов начинает поступать на вход Сложение 5 а меньшая - на вход Вычитание реверсявного счетчика 2. Поэтому на вькодах разрядов реверсивного счетчика 2 всегда образуется код модуля отклонения текущего приращения входного сигнала от приращения входного сигнала на ссгответствутощем участке интерполяции. Знак отклонения определяется сигналами на выходах триггера 16, nocTynasfflUHNOi на выходные клеммы 35 и 36, Сигнал t моментов перехода через нуль числа импульсов в

9899 4

счетчике 2 может быть вынесен с выхода блока 14 на шину 34 и нести дополнительную информацию о процессе изменения функции. 5 В эти моменты можно через элемент -ШИ 27 и блок 15 переноса кода опрашивать код текущего сигнала на выходах реверсивного счетчика 1.

1Гифровой компаратор и блок циф0 рового задания апертуры (фиг. 2) работают с.ледуюп1 1м образом.

Переключателем устанавливается код N. Во время работы реверсивного счетчика 2, в момент появле5 НИН на его выходах кода, равного коду N, на выходе цифрового компаратора 6 появляется импульс управления. На временной диаграмме

(фиг, 8) моменты совпадения кедов Q на выходе реверсивного счетчика 2 N(t) HHHdN j(t) и блока 11 соответствуют моменту времени t.,.,

ь С01 К2 сог Аналогично работает

цифровой компаратор 7. При дости1J женин кодом на выходах разрядов счет чика 3 кода, установленного блоком 11J на выходе компаратора 7 формируется иьтульс, устанавливаюнтий счетчик 3 в положение О.

„Блок 12 (фиг. 3) работает следующим образом.

. При постуштении импульса f(t - Т) на С-вход тригг.ер 39 переключается в положение 1 и на D-вход триггера 40 подается 1. Затем по приходу от генератора 10 тактового импульса f на С-вход триггера 40 и вход элемента И-НЕ 43 триггер 40 также пареклю гается в положение 1, На зькоде элемента И-НЕ 43 образуется О. По окончании тактового импульса на выходе элемента И-НЕ 43 появляется 1, которая включает одновибратор на элементах ИЛИ-НЕ 46 и 47, конденсаторе 49 и резисторе 51. Импульс,- сформированный одновибратором. переключает триггеры 39 и 40 в положение О. Таким образом, при поступлении ш-тульса на С-вход триггера 39 и

0 в момент прихода тактового импульса на прямом вькоде триггера 40 формируется импульс.

Схема, собранная на триггерах 37 и 38 и элементах И-НЕ 42 и ИЛИ-НЕ

S 44 и 45, конденсаторе 48 и резисторе 50, работает аналогично. Но поскольку тактовые импульсы управляющие данной схемой, с выхода

15

элемента И-НЕ 41 являются инверсными относительно тактовых импульсов f, на двух выходах устройства (прямой выход триггера 38 и прямой выход триггера 40) формируются импульсы, сдвинутые по времени один относительно другого, не перекрывающие один другой, длительностью, равной длительности тактовых импульсов ,

На временной диаграмме (фиг. 4) показан случай одновременного прихода входных импульсов на входах блока 12.

Елок 13 (фиг. ,5) работает следуюпщм образом.

При нулевой установке триггера 16, т.е. в случае, когда на его инверсном выходе, а значит, и на вторых входах элементов И 53 и 55 присутствует 1, частота импульсов с выхода элемента И 21 через элементы И 52 и ИГШ 56 поступает н суммирующий вход реверсивного счетчика 2, а частота с выхода элемента ИЛИ 29 через элементы И 55 и ИЛИ 57 - на вычитаюсций вход счетчика 2. При единичной установке триггера 16, т.е. в случае, когда на его прямом выходе, а значит, и на вторых входах элементов И 53 и 5А присутствует 1, частота импульсов с выхода элемента И 21 через элементы И 54 и ИЛИ 57 поступает на вычитающий вход реверсивного счетчика 2, а частота импульсов с выхода элемента ИЛИ 29 через элементы И 53 и ИЛИ 56 - на суммирующий вход счетчика 2. Таким образом, устройство позволяет подключать к суммирующему или вычитающему входам реверсивного счетчика 2 частоты импульсов с выхода элементов И 21 или ИЛИ 29.

Блок 14 (фиг. 6) работает таким образом, что в случае появления на выходах разрядов реверсив98996

него счетчика 2 логических О, на выходе блока 14. появляется управляющий импульс.

Блок 15 (фиг. 7) работает таким 5 образом, что при поступлении импульса управления с выхода элемента ИТМ 26 на вторые входы элементов И 58-61 на выходе блока 15 появляет СИ код, соответствующий коду на

О выходах разрядов реверсивного счетчика 1 .

Благодаря введению трех счетчиков импульсов, двух цифровых компараторов, триггера управления, фор15 мирователя импульсов и элементов И и ИЛИ с их связями в устройстве реализуется алгоритм интерполяционно-экстраполирующего анализа первого порядка изменчивости измеряе0 мой функции. Это позволяет оценивать среднее значение скорости изменения входного сигнала, что определяет стратегическое направление изменения сигнала, в отличие

5 от оценки по мгновенному значению производной, которая может дать . ложное направление при пульсациях, помехах и случайных выбросах сигналов.

0

Благодаря реализации интерполяционно-экстраполирующего алгоритма первого порядка по сравнению с известным появляется возможность восстанавливать измеряемую функцию

5 кусочно-линейной аппроксимирующей функцией с заданной точностью и значительно меньшим числом существенных отсчетов-, особенно для функций с линейными участками большой

0 величины, какими являются вертикальные структуры изменения температуры воды, в морях и океанах. Это позволяет значительно увеличить информативность устройства за счет допол5нительного сжатия собираемой информации .

12

Л

Пуск

f,lt-f)

л

13М®7аЬ&

/

J4 33

«J

JY

Jf

//

V h

i

-ЬВ-Ч

/г7

AN ft)

Фиг. 2

Фиг. 7

ЩШЛ

ПППППППППП

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Адаптивный аналого-цифровой преобразователь частотно-модулированных сигналов | 1972 |

|

SU443479A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Адаптивный аналого-цифровой преобразователь | 1979 |

|

SU864552A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1984-08-23—Публикация

1983-01-20—Подача