I

Изобретение относится к радиотехнике, в частности к фазовым детекторам, и может быть использовано в различных радиотехнических устройствах для определения разности фаз сравниваемых сигналов.

Известен фазовый детектор, содержащий три триггера, два логических элемента ИСКЛЮЧА1011Ц1Е ИЛИ и фильтр нижних частот 1}.

Недостатком известного фазового детектора является низкая надежность. Это объясняется тем, что при совпадении во времени обоих сравниваемых сигналов на установочные входы RSтриггера одновременно поступают одинаковые установочные потенциалы, и триггер принимает неопределенное состояние. Позтому логические устройства на основе RS-триггёров, выполненных на логических элементах ИЛИ-НЕ, должны строиться с учетом исключения комбинации сигналов PvS 1,« а логические устройства на основе RS-триггеров, выполненных на логических злементах И-НЕ, должны строиться, с учетом исключения комбинации сигналов .

Известен также фазовый детектор, содержащий триггер, два логических элемента И-НЕ, два инвертора и два элемента совпадения 12.

Недостаток известного фазового

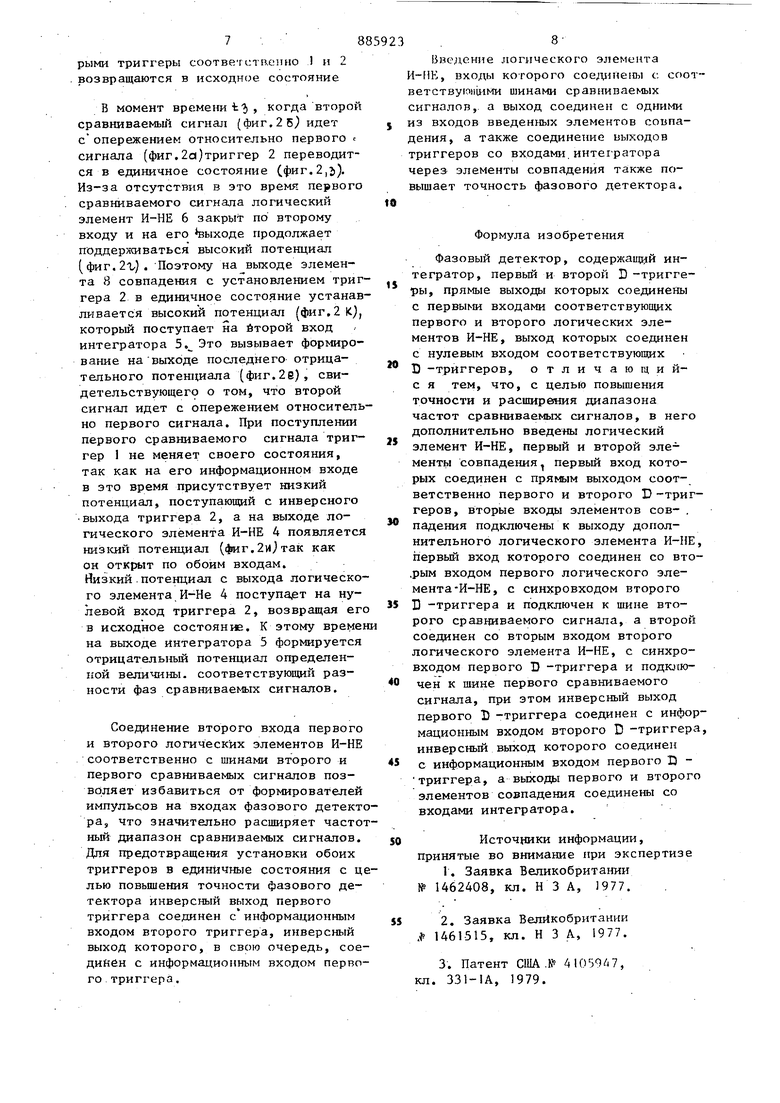

10 детектора состоит в том, что для обеспечения достаточной точности определения разности фаз йеобходимо, чтобы длительности импульсов во входных последовательностях быtsли одинаковыми. Кроме того, для нормальной работы указанного фазового детектора необходимо, чтобы оба входных сигнала перекрывались во времени. В противном случае триггер фаJOзового детектора не устанавливается в единичное состояние, то есть фазовьй детектор не реагирует на разность фаз сравниваемых сигналов. Наиболее близким к предлагаемоьгу по технической сущности является фаз вый детектор, содержащий интегратор, первый и второй D -триггеры, прямой выход которых соединен с первым входом соответственно первого и.второго логических элементов И-НЕ, выход которых соединен с нулевым входом соответствующих 1 -триггеров 13J. В данном фазовом детекторе для возможности определения разности фаз двух коротких, сравниваемых импульсов, не совпадающих во времени, длительность сравниваемых импульсов уве личивается формирователями импульсов подсоединенными .ко входам фазового детектора, что ограничивает возможность определения разности фаз сравниваемых сигналов в щироком диапазоне частот, то есть он становится непригодным при изменении частот сравниваемых сигналов в широком диапазоне, А соединение в известном фазовом детекторе выходов RS-триггеров со входами интегратора накладывает жесткие требования к разности потенциалов триггеров как в нулевом, так и в единичном состояниях. В противном случае при определении разности фаз сравниваемых сигналов указанный фазовый детектор вносит погрешность. Например . если сначала первый триггер устанавливается в единичное состояние, то на выходе интегратора до прихода импульса и на второй вход фазового детектора устанавливается определенный положительный потенциал. При поступлении сравниваемого иьотульса на второй вход фазового детектора второй триггер также перейдет в еди ничное состояние на время, равное сумме времени задержки сигнала в ло гическом элементе И-НЕ и в триггер Если единичный потенциал второго триггера хоть немного больше единич ного потенциала первого триггера, то на выходе интегратора появится отрицательный потенциал, свидетельс вующий о том, что сигнал, поступивший на второй вход фазового детекто ра идет с опережением сигнала на пе вом входе. Но этого не происходит. Таким образом, недостатками изве ного фазового детектора являются ни кая точность и невозможность опреде ления разности фаз сравниваемых сиг налов в широком диапазоне частот. Цель изобретения - повышение точности и расширение диапазона частот сравниваемых сигналов. Поставленная цель достигается тем, что в фазовый детектор, содержащий интегратор, первый и второй D -триггеры, прямиле выходы .которых соединены с первыми входами соответствующих первого и второго логических элементов И-НЕ, выход которых соединен с нулевым входом соответствующих D -триггеров, дополнительно введены логический элемент И-НЕ, первый и второй элементы совпадения, первый вход которых соединен с прямым выходом соответственно первого и второго D -триггеров j вторые входы элементов совпадения подключены к выходу дополнительного логического элемента И-НЕ, первый вход которого соединен со вторым входом первого логического элемента И-НЕ, с синхровходом второго С-триггера и подключен к шине второго сравниваемого сигнала, а второй соединен со вторым входом второго логического элемента И-НЕ, с синхровходом первого В -триггера и подключен к шине первого сравниваемого сигнала, при этом инверсш 1й выход первого D -триггера соединен с информационным входом второго D -триггера, инверсный выход которого соединен с -информационным входом первого D -триггера, а выходы первого и второго элементов совпадения соединены со входами интегратора. На фи1. I приведена функциональная схема фазового детектора; на фиг.2эпюры напряжений, поясняющие его работу. Фазовый детектор (фиг.1 содержит первьш 1 и второй 2 D -триггеры, первый 3 и второй 4 логические элементы И-НЕ, интегратор 5, дополнительный логический элемент Й-НЕ 6, первый 7 и второй 8 элементы совпадения, шину 9 первого сравниваемого сигнала и шину 10 второго сравниваемого сигнала. Выход 1 I интегратора является выходом фазового детектора. Прямой выхЬд D -триггеров 1 и 2 соединен с первым входом логических элементов И-НЕ соответственно 3 и Д, выход которых соединен с нулевым входом соответствующих D -триггеров 1 и 2. Первый вход элементов 7 и 8 совпадения соединен с прямым выходом -триггеров соответственно 1, и 2. Вторые входы элементов 7 и 8 совпаде| м соединены между собой и подклюены к выходу логического элемента -НЕ 6, первый выход которого соедиен со вторым входом логического элеента И-НЕ 3, с синхровходом D -триггера 2 и подключен к lIинe 10 сравниаемого сигнала. Второй вход логического элемента И-НЕ 6 соединен со вторым входом логического элемента И-НЕ 4, с синхровходом В -триггера I и подключен к шине 9 сравниваемого сигнала. Инверсный выход D -триггера I соединен с информационным входом D триггера 2, инверсный выход которого соединен с информационным входом D триггера 1, Выходы элементов 7 и 8 совпадения соединены соответственно с первым и вторым входами интегратоа 5.

При низком потенциале хотя бы на одном из своих входов на выходе огического элемента И-НЕ поддерживается высокий потенциал (элемент закрыт}, а при наличии высоких потенциалов на обоих входах логического элемента И-НЕ на его выходе поддерживается низкий потенциал (элемент открыт).

При наличии низкого потенциала хотя бы на одном входе элемента совпадения на его выходе поддерживается также низкий потенциал, а при наличии высоких потенциалов на обоих входах на его выходе поддерживается высокий потенциал.

При низком потенциале на нулевом входе D -триггера последний переходит в нулевое состояние (тшзкий потенциал на прямом В1 1ходе триггера) . Наличие перепада от низкого потенциала к высокому на синхровходе триггера переводит его в состояние, определяемое присутствующим потенциалом на его информационном входе,

Фазовый детектор работает следую щим образом.

В исходном положении триггеры фазового детекторл црхпдятся в нулевом состоянии. На первых входах элемент тов 7 и 8 совпадения поддерживаются низкие потенциалы, поступающие с прямого выходаD-триггеров соответственно 1 и 2. На выходе указанных элементов совпадения поддерживается низкий потенциал и па пыходе интегратора 5 сигнал отсутствует.

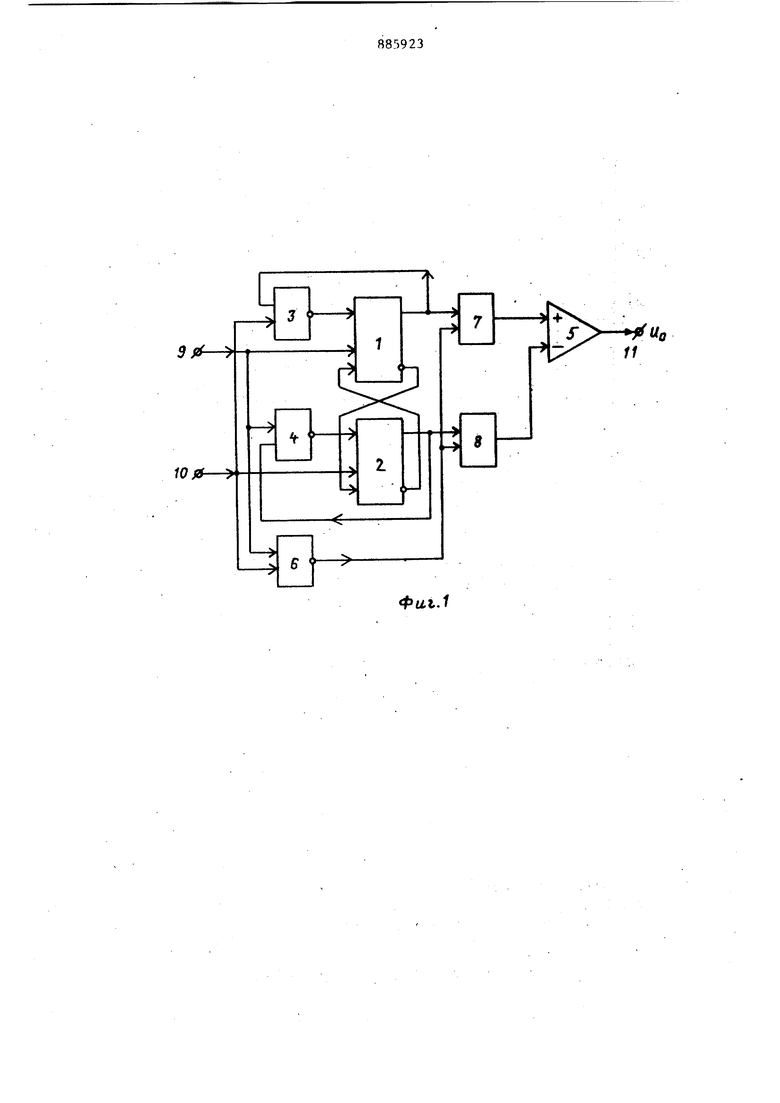

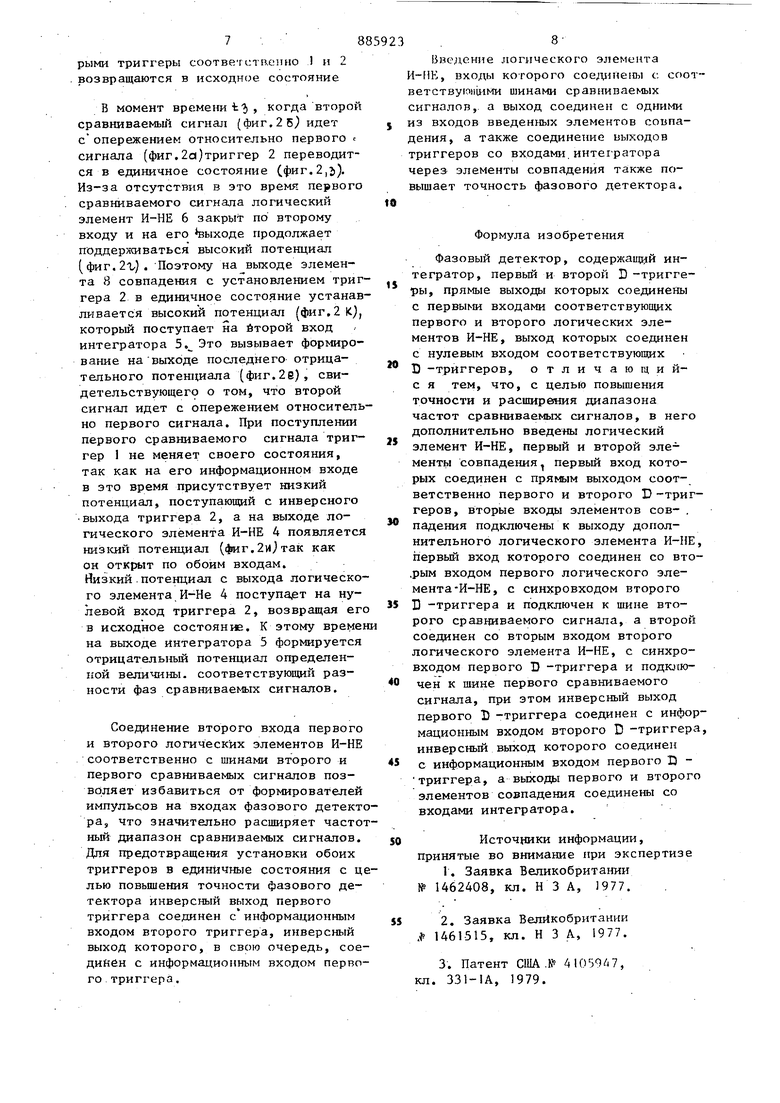

В момент премени t-|, когда первый сравниваемый сигнал ((hiir.Ci) идет с опережением «тцстптгльно пчорого сигнала (фиг,25), триггер 1 переЕодится в еди шчное состояние (фиг,2§ЛТак как в этовремя еще отсутствует второй сравниваемый сигнал, то логический элемент И-НЕ 6 закрыт по первому входу и на его выходе поддерживается высокий потенциал (фиг.21). Поэтому на выходе элемента 7 совпадения с установлением триггера 1 в единичное

состояние устанавливается высокий потенциал (фнг.25. Высокий потенциал с выхода элемента 7 совпадения посту.пает на первый вход интегратора 5, на выходе которого формируется полоj жительный потенциал (фиг.2е}, свидетельствующей о том, что первый сравниваемый сигнал идет с опережением относительно второго сигнала. При поступлении второго сравниваемого

сигнала триггер 2 не меняет своего состояния, так как на его информационном входе 6 это время присутствует низкий потенциал, поступающий с инверсного выхода триггера 1, а

J на выходе логического элемента И-НЕ 3 появляется низкий потенциал фиг,2лс), так как он открыт-по обоим

о,

входам. Низкий потенциал с выхода логического элемента И-НЕ 3 посту- Q пает на нулевой вход триггера 1, возвращая его в исходное состояние, К этому времени на .выходе интегратора 5 формируется положительньй потенциал определенной величины, со, ответствующий разности фаз сравниваеNbix сигналов,

В момент времени tft, когда передние фронты сравниваемых сигналов 0 совпадают во времени, т,е, когда фазы сравниваемых сигналов одинаковые триггеры 1 и 2 устанавливаются в единичные состояния (фиг,2В и З). В это же время на выходе логического

S элемента И-НЕ 6 появляется низкий уровень напряжения, так как на его первом и втором входах присутствуют cpaBHHBaei je сигналы. Нулевой потенциал с выхода логического элемента

0 И-НЕ 6 блокирует прохождение высоких потенциалов с выходов триггеров I и 2 через элементы 7 и 8 совпадения на входы интегратора 5. Таким образом, сигнал на выходе интегратора 5 в этом случае отсутствует, С установкой обоих триггеров в единичные состояния на выходе логических элементов И-НЕ 3 и 4 появляются низкие потенциалы (фиг.2х ,и) , кото7 8 рыми триггеры соответст. 1 и 2 возвращаются в исходнс е состояние В момент времени t5 , когда второй сравниваемьцЧ сигнал (фиг. 2 б) идет сопережением относительно первого с сигнала (фиг.2а)триггер 2 переводится в единичное состояние (фиг.2,5), Из-за отсутствия в это время первого сравниваемого сигнала логический элемент И-НЕ 6 закрыт по второму входу и на его выходе продолжает поддерлсиваться высокий потенциал (фиг. 2г.). Поэтому на выходе элемента 8 совпадения с установлением триг гера 2 в единичное состояние устанав ливается высокий потенциал (фиг, 2 К), который поступает на йторой вход интегратора 5. Это вызывает формирование навыходе последнего отрицательного потенциала (фиг.2е), свидетельствующего о том, что второй сигнал идет с опережением относитель но первого сигнала. При поступлении первого сравниваемого сигнала триг- гер 1 не меняет своего состояния, так как на его информационном входе в это время присутствует низкий потенциал, поступающий с инверсного выхода триггера 2, а на выходе логического элемента И-НЕ 4 появляется низкий потенциал (фиг.2и)так как он открыт по обоим входам. Низкий.потенциал с выхода логического элемента И-Не 4 поступает на нулевой вход триггера 2, возвращая ег в исходное СОСТОЯНИЕ. К этому време на выходе интегратора 5 формируется отрицательный потенциал определенной величины, соответствующий разности фаз сравниваемых сигналов. Соединение второго входа первого и второго логических элементов И-НЕ соответственно с шинами второго и первого сравниваемых сигналов позволяет избавиться от формирователей импульсов на входах фазового детект ра, что значительно расширяет часто ный диапазон сравниваемых сигналов. Для предотвращения установки обоих триггеров в единичные состояния с ц лью повышения точности фазового детектора инверсный выход первого триггера соединен с информшдионным входом второго триггера, инверсный выход которого, в свою очередь, соединен с информационным входом первого триггера. Внедение логического элемента -ПЕ, зходы которого сое;у1иены с соответству10 1Ц1Ми шинами сравниваемых сигналов, а выход соединен с одними з входов введенных элементов совпадения, а также соединение выходов триггеров со входами, интегратора через элементы совпадения также повышает точность фазового детектора. Формула изобретения Фазовый детектор, содержаидай интегратор, первый и второй D -триггеры, прямые выходы которых соединены с первыми входами соответствующих первого и второго логических элементов И-НЕ, выход которых соединен с нулевым входом соответствующих D -триггеров, отличающийс я тем, что, с целью повышения точности и расширения диапазона частот сравниваемых сигналов, в него дополнительно введены логический элемент И-НЕ, первый и второй элементы совпадения первый вход которых соединен с прямым выходом соответственно первого и второго D -триггеров, вторые входы элементов сов- . падения подключены к выходу дополнительного логического элемента И-НЕ, первый вход которого соединен со вто,рым входом первого логического элемента -И-НЕ, с синхровходом второго D -триггера и подключен к шине второго сравниваемого сигнала, а второй соединен со вторым входом второго логического элемента И-НЕ, с синхровходом первого D -триггера и подключен к шине первого сравниваемого сигнала, при этом инверсный выход первого D -триггера соединен с информационным входом второго D -триггера, инверсный выход которого соединен с информационным входом первого D триггера, а выходы первого и второго элементов совпадения соединены со входами интегратора. Источники информации, принятые во внимание при экспертизе 1.Заявка Великобритании № 1462408, кл. ИЗ А, 1977. 2.Заявка Великобритании 1461515, кл. Н 3 А, 1977. 3.Патент США .№ 4105967, кл. 331-1А, 1979.

Uo

| название | год | авторы | номер документа |

|---|---|---|---|

| Способ измерения рассогласования между углами поворота,один из которых задан кодом | 1985 |

|

SU1285595A1 |

| Устройство для измерения рассогласования между углом и кодом | 1987 |

|

SU1411973A1 |

| Устройство сравнения двух частот | 1981 |

|

SU982183A1 |

| Устройство для синхронизации цифровой магнитной записи | 1989 |

|

SU1691888A1 |

| Устройство для контроля и диагностики цифровых устройств | 1988 |

|

SU1583886A2 |

| УСТРОЙСТВО ПОИСКА И СОПРОВОЖДЕНИЯ СИГНАЛА СИНХРОНИЗАЦИИ В СПУТНИКОВЫХ СИСТЕМАХ СВЯЗИ ПО ПРИЕМУ | 1995 |

|

RU2093964C1 |

| Устройство для считывания графической информации | 1989 |

|

SU1683046A1 |

| Импульсный частотно-фазовый детектор | 1987 |

|

SU1483594A1 |

| Преобразователь время-код | 1991 |

|

SU1785073A1 |

| РАДИОЛОКАЦИОННАЯ СТАНЦИЯ | 1993 |

|

RU2037842C1 |

Фи,1.1

Фиг.г

Авторы

Даты

1981-11-30—Публикация

1979-11-29—Подача