Изобретение относится к электронике и может быть использовано на железнодорожном транспорте, где необнаруженный сбой в работе логических устройств может привести к непоправимым, последствиям. Известен способ получения логических схем с безопасным отказом, основанный на использовании безопасных элементов И, ИЛИ, НЕ Г. Недостатком известного способа является наличие в предложенных схемах большого количества трансформаторов, изготовление которых в интегральном исполнении не освоено, что резко сни жает перспективу их массового производства. Наиболее близким техническим реше нием к изобретению является способ получения схем с безопасным отказом, заключающийся з том, что каждую логи ческую функцию выполняют одновременно элементами двух каналов пересураи ваемой логики, перестройку которых с положительной на отрицательную и обратно выполняют с помощью специаль ных опорных последовательностей. Сиг налы на выходах соответствующих элементов каналов контролируют на со ответствие и формируют опорные и логические последовательности, которые в случае обнаружения несоответствия в работе логических схем каналов, прерывают 2. Если входные последовательности логического элемента, выполненного на основе мажоритарного элемента,совпадают с опорной последовательностью, возможные обЕ«:1вы внутри мажоритарного элемента не могут быть обнаружены . схемой контроля, хотя способны привести к опасной ситуации. Логика мажоритарного элемента может быть описана функцией у х х X Х XjV X/jX. В случае,если все последовательности X,j, Х, Х идентичны, возможен обрыв двух входов схемы ИЛИ, который приведет к выполнению функции У ) Хд и после этого сигналы на выходе мажоритарного элемента не изменяют своей формы. Последующий обрыв входа Xj мажоритарного элемента также не будет зафиксирован. Если аналогичные обрывы произвести рр йтором канале, то и они не будут . замечены. Полученная ситуация опасна, хотя и не обнаруживаема. Цель изобретения - исключение необнаруживаемых отказов.

Для достижения поставленной цели в способе получения комбинационных логических схем с безопасным отказом заключающемся в том, что каждую логическую функцию выполняют одновременн в двухканалах логики, соответствие работы которых покаскадно контролируют, формируют опорные и логические последовательности, которые в случае

обнаружения несоответствия в работе каналов логики,прерывают, для каждог входа логического элемента, входящего в состав комбинационной логической , формируют последовательность, состоящую не менее, чем из п+2 временных интервалов (где п максимальное количество входов логического элемента, входящего.в состав комбинационной логической схемы), в первом из которых,, определяющим подают сигнал, соответствующий значению аргумента функции, выполняемой комбинационной логической схемой, затем подают хотя бы в одном из п+1 оставшихся временных интервалов контрольный сигнал, беспрепятственно проходящий к выходу логического элемента и не совпадающий хотя бы в одном временном интервале с контрольными сигналами других входов комбинацион.ной логической схемы, исключают хотя бы в одном из п+1 временных интервалов появление на входах логического элемента контрольных сигналов и определяют результат выполнения логической функции по значению выходных сигналов в определяющем временном интервале на выходах двух каналов логики. о .

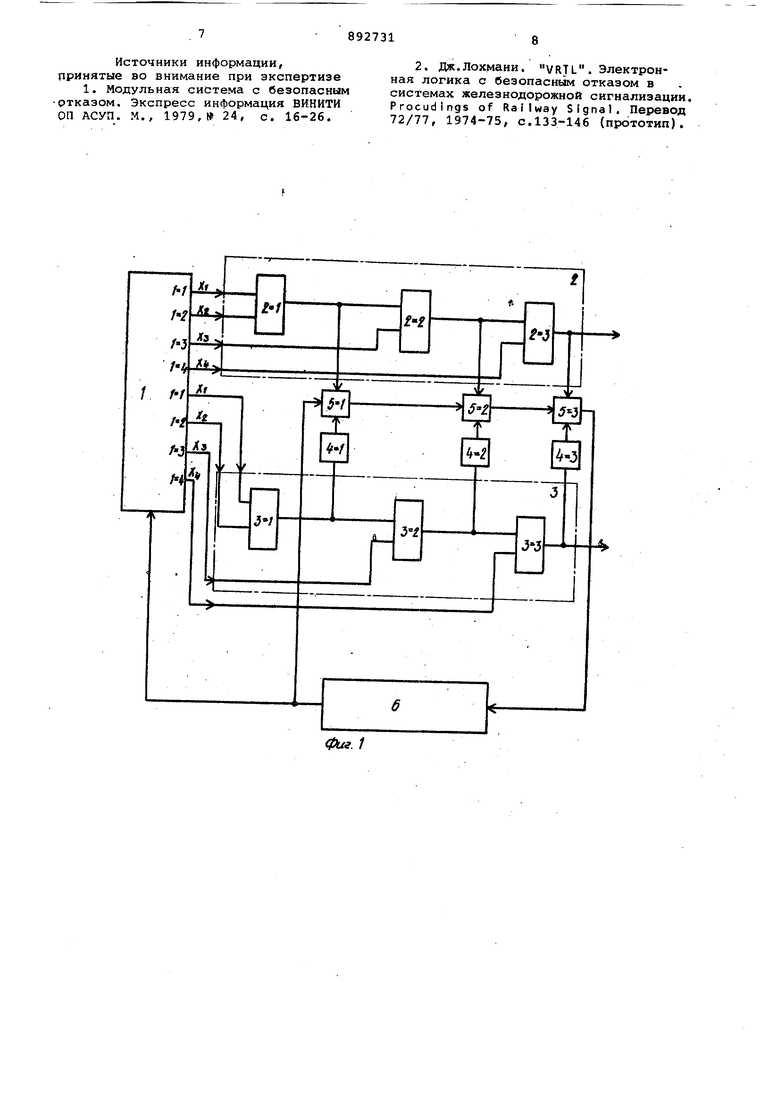

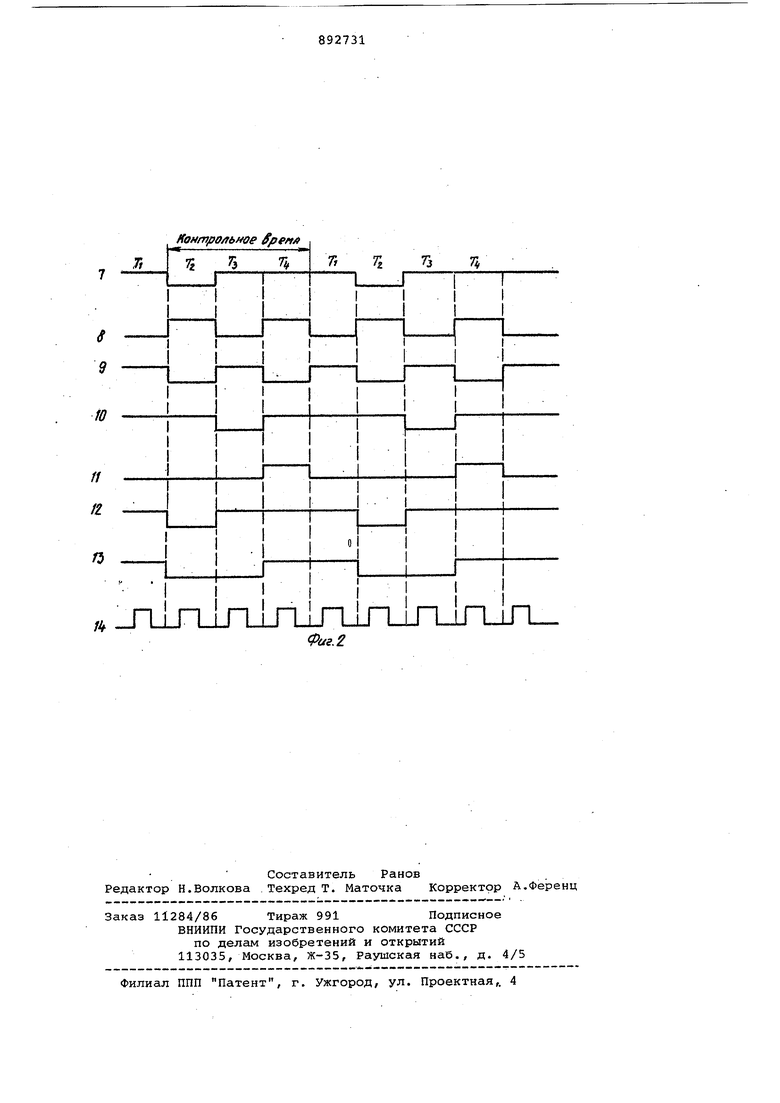

На фиг. 1 показана комбинационная логическая -схема, реализующая функцию ( Х4Х2 + Xj) на фиг. 2 - временная диаграмма работы устройства. Логическая схема включает блок 1 формирования входных последовательностей., выходы блока 1 формирования входных последовательностей, каналы 2 и 3 логики, элементы соответственно И, ИЛИ и И канала 2 логики, элементы соответственно И, ИЛИ и И канала 3 логики, элементы НЕ ,элементы сравнения и блок б контроля. Выходы и (фиг. 1) соединены со входами элементов И и , выход соединен с первыми входами элементов ИЛИ ,вторые входы которых соединены соответственно с выходами элементов И и , выход соединен с первыми входами элементов И и ,вторые входы котррых соединены соответственн6 с выходами элементов ИЛИ и , первые входы элементов сравнения соединены соответственно с выходами элементов И , ИЛИ и И , вторые входы элементов сравнения соединены соответственно с выходами элементов

НЕ , входы которых соединены соответственно с выходами элементов И , ИЛИ и И , третьи входы элементов сравнения соединены соответственно с выходами блока 6 контроля и элементов и сравнения, выход элемента сравнения соединен со входом блока б контроля, выход которого соединен со входом блока 1 формирования входных последовательностей.

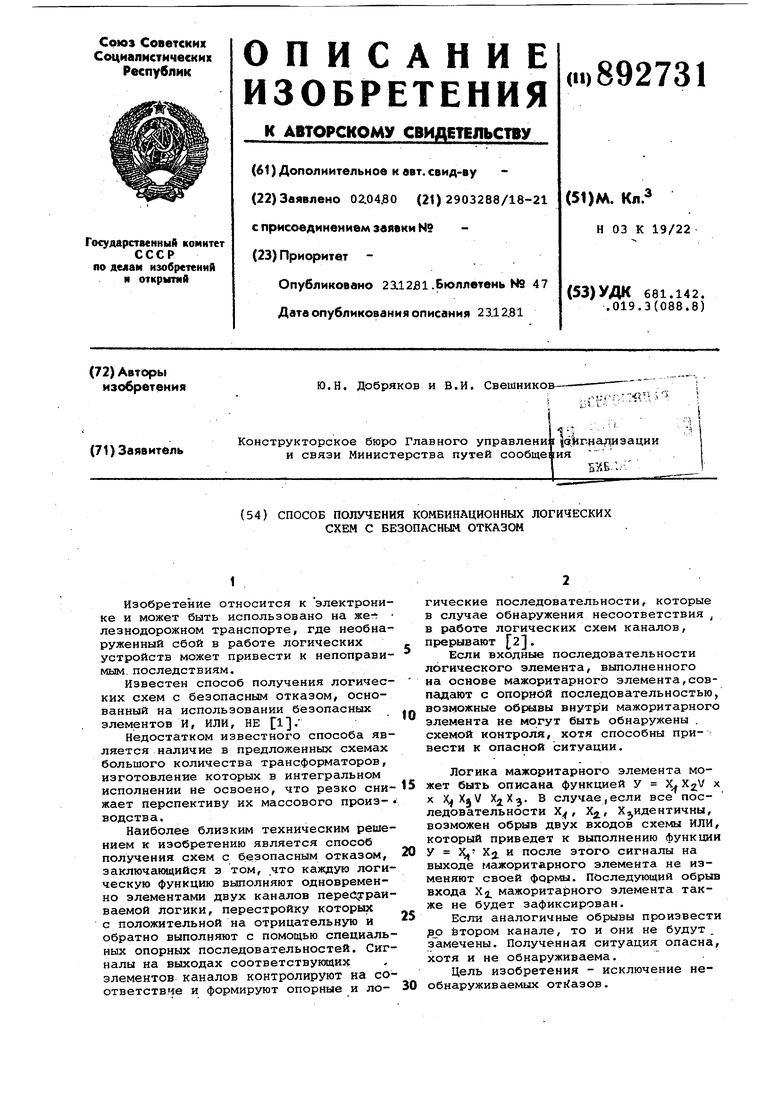

Напряжение на выходах блока 1 изображено диаграммами 7-10,соответственно (фиг. 2), на выходау элементов (или на выходах элментов ) - диаграммами 11-13, на выходе блока 6 контроля - диаграммой 14. J,

В двух каналах 2 и 3 логики с помощью элементов и , соответственно, реализуют искомую функцию. С помощью элементов сравнения и блока 6 контролируют факт совпадения сигналов на выходах соответствующих логических элементов каналов, для чего с помощью блока 6 контроля анализируют факт прохождения к его входу сигнала, сформированного на выходе. В случае, если сигнал с выхода блока б контроля приходит к его входу, считают, что сигналы на выходах соответствующих логических элементов каналов совпадают, и на выходе блока б формируют очередной контролирующий сигнал.J,

Под влиянием сигналов с выхода блока б контроля на выходах блока 1 формируют для каждого канала 2 и 3 логики входные последовательности, соответствующие аргументам реализуемой функции, состоящие не менее, чем из п+2 временных интервалов (в нашем случае п максимальное количество входов логического элемента канала, равно двум у и количество временных интервалов выбраноравным 4).

Для случая, когда на выходах присутствует код 1011, характер последовательности изображен на фиг. 2 (диаграммы 7-10). Последовательности формируют теСким образом, чтобы в определяющем временном интертервале Т сигнал соответствовал значению аргумента функции, а хотя бы в одном из последующих временных интервалов подают контрольный сигнал, способный .беспрепятственно пройти к выходу соединенного с ним логического элемента. Например, выходы и блока 1 соединены со входами элемента И 2а1, поэтому в седьмой последовательности во временном интервале Тя, а в восьмой последовательности в интервале Т формируют сигнал О, способный беспрепятственно проследовать через элемент И . Контрольный сигнал в интервале Тл для седьмой последовательности формируют не совпадающим с контрольным сигналом Tj восьмой последовательности. В интервале Т для седьмой и восьмой последовательностей обеспечивают отсутствие контрольного сигнала О. На выходе элемента и получают 11-ю последовательность, которая является входной для элемента ИЛИ , так как в определяющем интервале f, сигнал на ее выходе соответствует функции ., а в контрольное время в интервале Т сформирован сигнал 1, который способен беспрепятственно проходить череэ элементы ИЛИ , . Поскольку на выходе блока 1 формируют контрольный 1 в интервале Т, Тл,, а в интер интервале Тл в 11-й и девятой посйеДовате - - -- .--- гельностях обеспечивают отсутствие контрольных сигналов 1, такие последовательности можно подавать на входы элементов ИЛИ , . На выходах элементов ИЛИ , получают 12-ю последовательность,которая совместно с 10-й последовательностью на выходе блока 1 может подаваться на входы элементов И 2 3, , на выходе которых получают 13-ю последова тельность, характеризующуюся тем, что винтервале . чение сигнала на выходе соответствует реализуемой функции. Учитывая, что сигналы на выходах блока 1 в оба канала поступают синхронно и синфазно,при нормальной работе сигналы на выходах соответствую щих логических элементов каналов также появляются синхронно и синфазно. С помощью элементов сравнения и блока б контроля постоянно фиксируют совпадение сигналов на выходах соответствующих логических элементов каналов и формируют очередные контро пирующие сигналы. Нарушение в работе однрго из каналов, вызванное обрывом проводов или пробоем логических элементов, неизбежно приводит либо к исчезновению контрольного сигнала на выходе логического элемента, либо к появлению сигнала, соответствующего контрольному, в интервалах времени, В которых контрольные сигналы появлятьс Яне должны. Например, обрыв выхода блока 1, соединенного с каналом 2, приводит к тому, что в интервале Т на выходе элемента И вместо сигнала появляется сигна,л 1. Так как в канале 2 аналогичная неисправность не произошла, с помощью элемента сравнения фиксируют несовпадение и с помощью блока 6 прекращают формирование очередных контролирующих сигналов. С помощью блока 1 прекращают поступление прследовательностей на его выходах, фиксируют сбой. Если в результате аварии на выходе , соединенном с каналом 2, появляется постоянный сигнал О, с помощью элемента фиксируют несовпадение сигналов на выходах элементов И , в интервале Т и переводят устройство в аварийное состояние. При нормальной работе устройства результат выполнений логической операции определяют по значению выходных сигналов элементов И , в определяюцем временном интервале Tf. Предлагаемый способ получения схемы безопасной логики позволяет во многих случаях при проектировании схем железнодорожной автоматики отказаться от использования громоздких уникашьных реле первого класса и Зс1менить их интегральными мик-, росхемами. Формула изобретения Способ получения комбинационных .логических схем с безопасным отказом, заключающийся в том, что каждую логическую функцию выполняют одновременно в двух каналах логики, соответствие работы которых покаскадно контролируют, формируют опорные и логические последовательности, которые в случае обнаружения несоответствия в работе каналов логики, прерывают, отличающийс я тем, что, с целью исключения необнаружи-ваемых отказов, для каждого входа логического элемента, входящего в состав комбинационной логической схемы, формируют последовательность, состоящую не менее, чем из п+2 временных интервалов (где п - максимальное количество входов логического элемента, входящего в состав комбинационной логической схемы), в первом из которых, определяющим подают сигнал, соответствующий значению аргумента функции, выполняемой комбинационной логической схемой,затем подают хотя бы в одном из п+1 оставшихся временных интервалов контрольный сигнал, беспрепятственно проходящий к выходу логического элемента и не совпадающий хотя бы в одном временном интервале с контрольными сигналами других входов комбинационной логической схемы, исключают хотя бы в одном из п+1, временных интервалов появление на входах логического элемента контрольных сигналов и определяпот результат выполнения,логической функции по значению выходных сигналов в определяющем временном интервале на выходах двух каналов логики.

Источники информации/ принятые во внимание при экспертизе

1. Модульная система с безопасным отказом. Экспресс информация ВИНИТИ ОП АСУП. М., 1979, 24, с. 16-26.

2, Дж.Лохмани. VRJL. Электронная логика с безопасным отказом в системах железнодорожной сигнализации, Procudlngs of Railway Signal. Перевод 72/77, 1974-75, с.133-146 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Способ получения комбинационных логических схем с безопасным отказом | 1982 |

|

SU1018253A1 |

| Способ получения надежных комбинационных логических структур | 1982 |

|

SU1061261A1 |

| СПОСОБ И УСТРОЙСТВО ДЛЯ КОНТРОЛЯ РАБОТОСПОСОБНОСТИ БЛОКА УПРАВЛЕНИЯ ДВИГАТЕЛЕМ ВНУТРЕННЕГО СГОРАНИЯ | 2007 |

|

RU2453903C2 |

| СИСТЕМА ВИБРАЦИОННОГО КОНТРОЛЯ | 2008 |

|

RU2371695C1 |

| Устройство для индикации отказов в трехканальной вычислительной системе | 1989 |

|

SU1721608A1 |

| Устройство автоматической защиты процесса нитрования | 1988 |

|

SU1685500A1 |

| РВИРОВЛННОЕ УСТРОЙСТВО | 1971 |

|

SU320812A1 |

| СПОСОБ ОПРЕДЕЛЕНИЯ СВОБОДНОСТИ ОТ ПОЕЗДА УЧАСТКА ЖЕЛЕЗНОДОРОЖНОГО ПУТИ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1995 |

|

RU2104894C1 |

| СИСТЕМА УПРАВЛЕНИЯ И КОНТРОЛЯ ПОЛОЖЕНИЯ ОРГАНОВ РЕГУЛИРОВАНИЯ ЯДЕРНОГО РЕАКТОРА | 2009 |

|

RU2412493C1 |

| Резервированное устройство | 1982 |

|

SU1059710A1 |

ft JTjJTJJl Lrb-rilriJ-rLJLrLiri Фиг. 2

Авторы

Даты

1981-12-23—Публикация

1980-04-02—Подача