Изобретение относится к электронике и может быть использовано на железнодорожном транспорте, где необнаруженный сбой в работе логических схем может привести к опасным ситуациям.

Известен способ получения логических структур, заключающийся в том, что каждую логическую функцию выполняют одновременно с помощью мажоритарных элементов двух каналов перестраиваемой логики, настройку которых по выполнению заданной функции выполняют с помощью сигна лов опорной частоты, а на входы подают логические сигналы 1 или О один из которых идентичен сигналам опорной частоты, а другой - ее инверсии. Сигналы с выхода логического элемента в зависимости от результата снимают либо в виде последовательности эквивалентной опорной частоты, либо в виде ее инверсии. Сигналы на выходах соответствующих элементов каналов контролируют на соответствие и формируют сигналы опорной частоты, которые в случае обнаружения несоответствия в работе логических схем каналов прерывают Г1.

Недостаток известного способа заключается в том, что встречающиеся на входах логического элемента комбинации входных сигналов не обра(Зуют набора, достаточного для контроля логического элемента. Из-за этого в составе логических схем элементов возможно появление необнаруживаемых неисправностей, способных привести к .опасным последствиям.

Известен способ получения надежных комбинационных логических структур, заключаю1чийся в том, что формируют, одновременно на входах каждого из двух каналов комбинационной логической структуры набор сигналов контролирукяцего теста и комбинацию сигналов, соответствующую аргументам выполняемой функции, контролируют идентичность выходных сигналов двух каналов и прерывают динамику их работы в случае обнаружения рассогласования. Согласно этому способ на входах канвшов формируют последовательности сигналов, состоящие из П временных интервалов, в одном из которых, опоеделяюшем, на входы каналов подают сигналы, соответствукшие значению аргументов Функции, а в остальных П-1 контрольных интервалах - комбинации сигналов набора сигналов контролирьдадего теста. Наборы сигнёшов контролирукицего теста чередуют с комбинациями си1 налов, соответствуювщх значениям аргументов выполняемой функции, и резуль, тат выполнения логической операции

определяют по значению выходного сигнала в определяющем временном интервале C2J.

Недостатком известного способа является сравнительно низкое быстродействие, вызванное необходимостью определять определяющие интервалы друг от друга П-1 контрольными интервалами. Учитывая, что значение функции можно прочитать только в определяющем интервале, максимальное время реакции логики на изменение контролируемого процесса может достигнуть (П-1)-Т, где Т - длительность одного временного интервала (в секундах).

Цель изобретения - повышение быстродействия комбинационных логических структур.

Для достижения поставленной цели согласно способу получения комбинационных логических структур о самоконтролем, заключающемуся в том,что формируют одновременно на входах каждого из двух каналов комбинационной логической структуры набор сигналов контролируемого теста и комбинацию сигналов, соответствующую аргументам выполняемой функции, контролируют идентичность выходных сигналов двух каналов и прерывают их работу в случае обнаружения рассогласования, формируют каждую комбинацию контролирующего теста из набора сигналов контролирующего теста поочередно с комбинацией сигналов, соответствующий аргументам выполняемой функции, причем после окончания набора формирование возобновляют. .

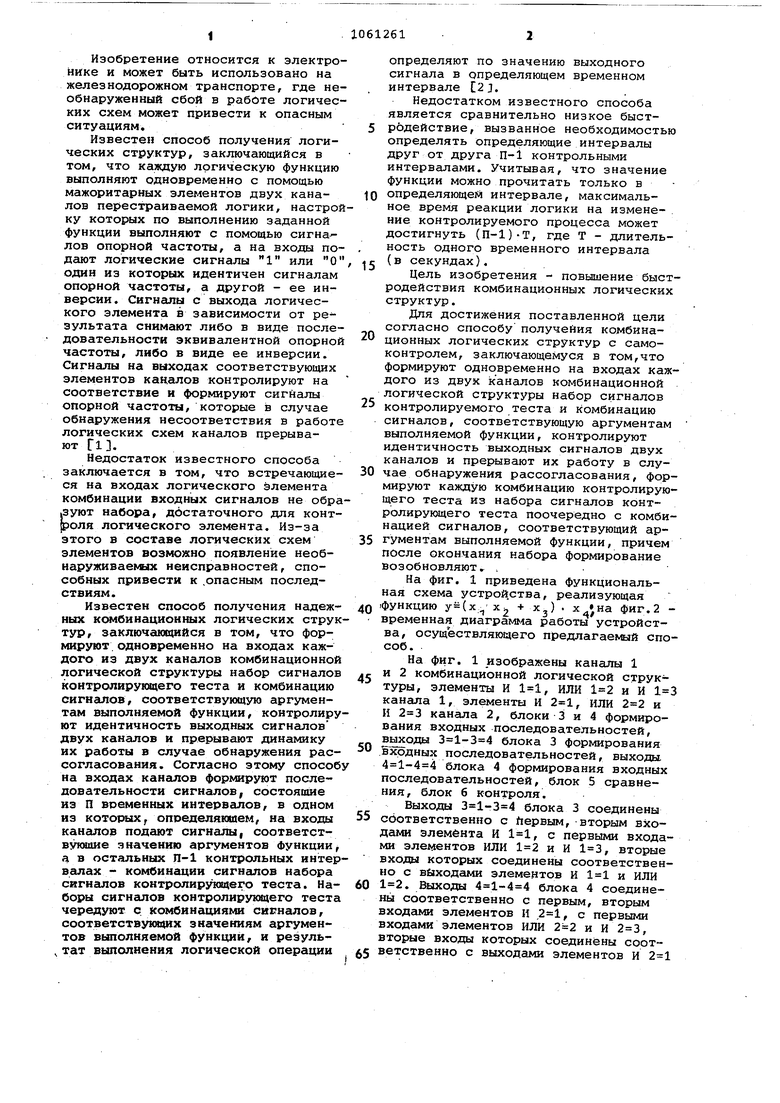

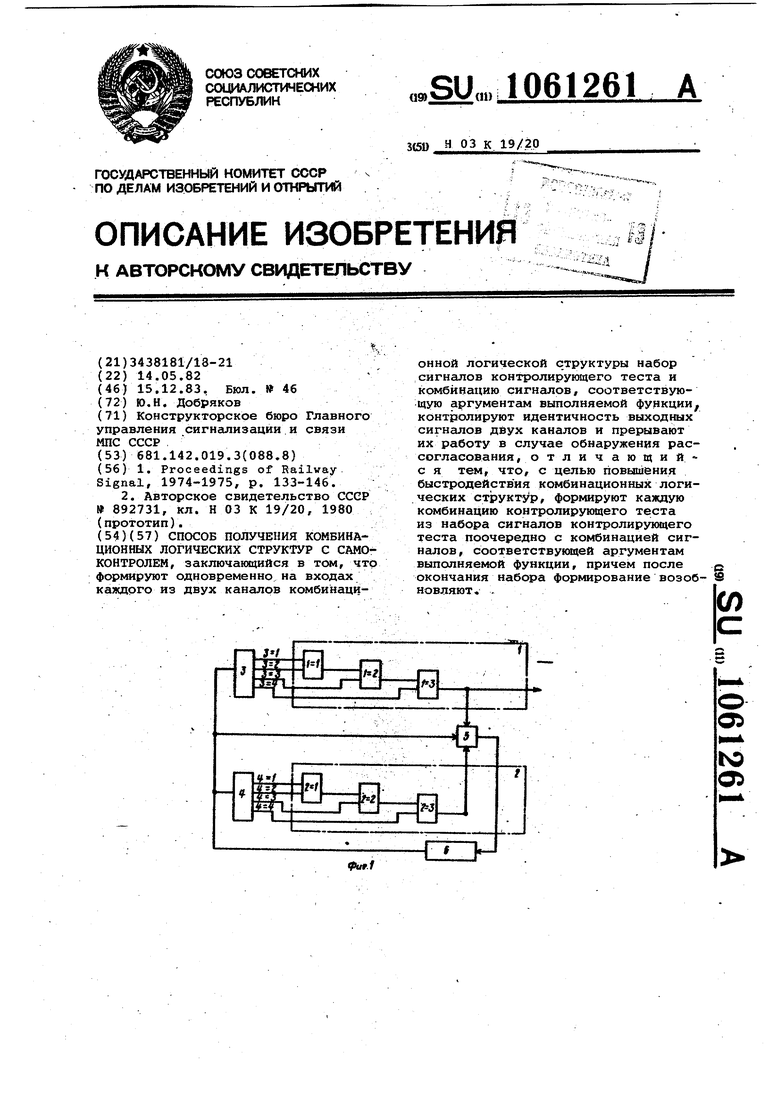

На фиг. 1 приведена функциональная схема устройства, реализующая .функцию у(х х + Xj) фиг.2 временная диаграмма работы устройства, осуществляющего предлагаемый способ.

На фиг. 1 изображены каналы 1 и 2 комбинационной логической структуры, элементы И , ИЛИ и И 1 канала 1, элементы И , ИЛИ и И канала 2, блоки 3 и 4 формирования входных последовательностей, выходы блока 3 формирования входных последовательностей, выходы: блока 4 формирования входных последовательностей, блок 5 сравнения, блок 6 контроля.

Выходы блока 3 соединены соответственно с йервым, вторым входами элемента И , с первыми входами элементов ИЛИ и И , вторые входы которых соединены соответственно с выходами элементов И и ИЛИ . Выходы блока 4 соединены соответственно с первым, вторым входами элементов и , с первыми входами элементов ИЛИ и и , вторые входы которых соединены соответственно с выходами элементов И 2

и ИЛИ , выходы элементов И ,. , являющиеся выходами каналов 1 и 2 соответственно, соединены с информационными входами блока 5 сравнения, выход которого соединен с входов блока 6 контроля, выход которого соединен с входами блоков 3 и 4 и с управлякядим входом- блока 5 сравнения. На фиг. 2 изображены диаграммы 7-10 напряжений на выходах соответственно и , и , и , диаграмма ,11. наптэяжений на выходах элементов И , ,диаграмма 12 напряжений на выходах элементов ИЛИ , , диаграмма 13 напряжения на выходах элементов И , , КИ - контрольный интервал, ОН - опре:деляющий интервал.

Последовательность выполнения действия следукадая.

В двух каналах 1 и 2 с помощью элементов - и - реализуют искомую функцию. С помощью блока 5 сравнения и блока 6 контроля контролируют факт совпадения сигналов на выходах логических схем каналов 1 и 2. В случае нарушения идентичности входных и выходных сигналов блока 6 контроля прекращают формирование сигналов на своем выходе. Под влиянием сигналов с выхода блока б контроля на выходах блоков 3 и 4 формирования выходных последовательностей независимо формируют комбинации сигналов - последовательности 7, 8, 9 и 10, в которых чередуют

комбинации сигналов, соответствующих аргументам выполняемой функции, с комбинациями сигналов контролирующего теста, причем после окончания набора комбинаций контролирующего теста его возобновляют.

Набор комбинаций контролирующего теста под|бирают таким образом, чтобы любая неисправность реализуемой комбинационной структуры проявлялась на

0 ее выходе в виде отклонения значения сигналов от их значений на выходе нормально работающей структуры;

Увеличения быстродействия структур, регшизованных согласно предлаггаемому способу, добиваются благода5:ря тому, что комбинации контролирую щего tecTa подают-на входы Комбинационных логических структур поочередно с определяющими комбинациями сигналов,, соответствующих аргумен0там выполняемой функции, в результате чего время ожидания очередного определяющего интервала не превышает времени Т, что в П-1 раз меньше, чем у прототипа.

5

Технический эффект становится особенно существенным, когда реализуется сложная многовходовая комбинационная структура, тест которой представляет собой длинный набор входных ком0бинаций.

Применение предлагаемого способа получения структур, исключающих появление необнаруживаемых отказов, позволяет повысить быстродействие логи5ческих блоков железнодорожной автоматики.

| название | год | авторы | номер документа |

|---|---|---|---|

| Способ получения комбинационных логических схем с безопасным отказом | 1980 |

|

SU892731A1 |

| Способ получения комбинационных логических схем с безопасным отказом | 1982 |

|

SU1018253A1 |

| Устройство для контроля логических блоков | 1986 |

|

SU1336011A2 |

| СПОСОБ И УСТРОЙСТВО СИНТЕЗА, ПЕРЕДАЧИ, ПРИЕМА, АНАЛИЗА И ОЦЕНКИ МНОГОВАРИАНТНЫХ ПО ФОРМЕ, МНОГОПОЗИЦИОННЫХ И ЛОКАЛЬНЫХ ПО СПЕКТРУ СИГНАЛОВ | 2000 |

|

RU2160509C1 |

| Систолическая структура для вычисления логических функций | 1989 |

|

SU1654809A1 |

| Способ передачи дискретных сообщений с шифрованием кодов и система для его осуществления | 2022 |

|

RU2819142C1 |

| Устройство для интерполяции аргумента гармонических функций | 1982 |

|

SU1019467A1 |

| Устройство для вычисления степенной функции | 1986 |

|

SU1348831A1 |

| Микропрограммное устройство для управления каналами ЭВМ | 1982 |

|

SU1068938A1 |

| Самокорректирующееся дискретное устройство | 1989 |

|

SU1716521A1 |

СПОСОБ ПОЛУЧЕНИЯ КОМБИНАЦИОННЫХ ЛОГИЧЕСКИХ СТРУКТУР С САМОКОНТРОЛЕМ, заключаницийся в тс, что формируют одновременно на входах каждого из двух каналов комбинационной логической структуры набор сигналов контролирующего теста и комбинацию сигналов, соответствующую аргументс1м выполняемой функции, контролируют идентичность выходных сигналов двух каналов и прерывают их работу в случае обнаружения рассогласования, отличающий- с я тем, что, с целью повышения быстродействия комбинационных логических структур, формируют каждую комбинацию контролирующего теста из набора сигналов контролирующего теста поочередно с комбинацией сигналов, соответствующей аргументам выполняемой функции, причем после окончания набора формирование возоб- € новляют. . (Л о: N) О) LT-j-i фиг

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Proceedings of Railway Signal, 1974-1975, p | |||

| Топочная решетка для многозольного топлива | 1923 |

|

SU133A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Способ получения комбинационных логических схем с безопасным отказом | 1980 |

|

SU892731A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1983-12-15—Публикация

1982-05-14—Подача