СХ) KD СЛ

00

10

Изобретение относится к электронике и может быть использовано на железнодорожном транспорте, где необнаруженный сбой в работе логических схем может привести к непоправимым последствиям.

Известен способ получения логических схем с безопасным отказом, заключающийся в том, что каждую логическую функцию выполняют элементами одновременно двух каналов перестраиваемой логики, перестройку которой с положительной на отрицательную и обратно выполняют с помощью специальных опорных последовательностей сигналов. Сигналы на выходах соответствующих элемент,рв каналов контролируют на соответствие и формируют опорные и логические последовательности, которые в случае обнаружения несоответствия в работе логических схем каналов прерывают LlJ.

Недостаток известного способа заключается в том, что если входные последовательности логического элемента, выполненного на основе мажоритарного элемента совпадают с опорной последовательностью, то возможные об рывы внутри мажоритарного элемента не всегда обнаруживаются схемой контроля, что может привести к опасной ситуации..

Известен способ получения комбинационных логических схем с безопасным отказом, заключающийся в формировании логической.1 и логического О на входах комбинационной логической схемой в виде последовательностей сигналов, один из которых определяет значение аргумента, а остальные конт ролируют исправность логической схемы, а также в обнаружении отклонений выходных сигналов, воздаваемых схемами различных каналов, от нормы и прерывами динамики работы, а результат выполнения логических операций определяют по значению выходного сигнала в определяющем временном интервале

Недостатками известного способа являются сравнительно большой объем оборудования, необходимый для реализации двух каналов обработки информации, и связанная с этим низкая надежность реализ емых схем.

Целью изобретения является сокращение объема необходимого оборудова.ния и повышение надежности схем.

Цель достигается тем, что согласно способа, заключающемуся в формировании логической 1 и логического О на входах комбинационной логической схемы в виде последовательностей сигналов, один из которых определяет значение аргумента, а остальные контролируют исправность логической схемы, а также в обнаружении отo клонений выходных сигналов от нормы и прерывании работы, требуемый набор комбинационных логических схем выполняют в одном канале, приводят к единому значению 1 или О выходные

5 сигналы кс 1бинационных логических схем в определяющем интервале, формируют от независимых источников последовательности сигналов, эквивалентные приведенным сигналам комбинацион0. ных логических схем, и контролируют наличие отклонений приведенных выходных последовательностей комбинационных логических схем от сформированных последовательностей .

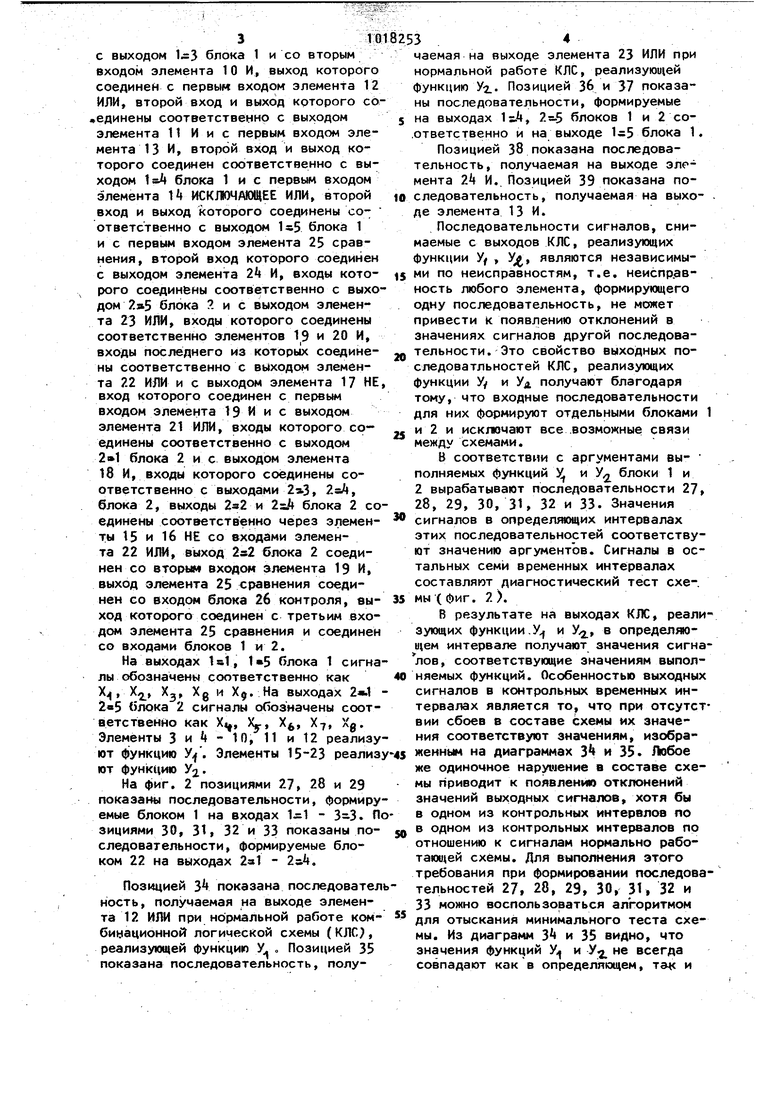

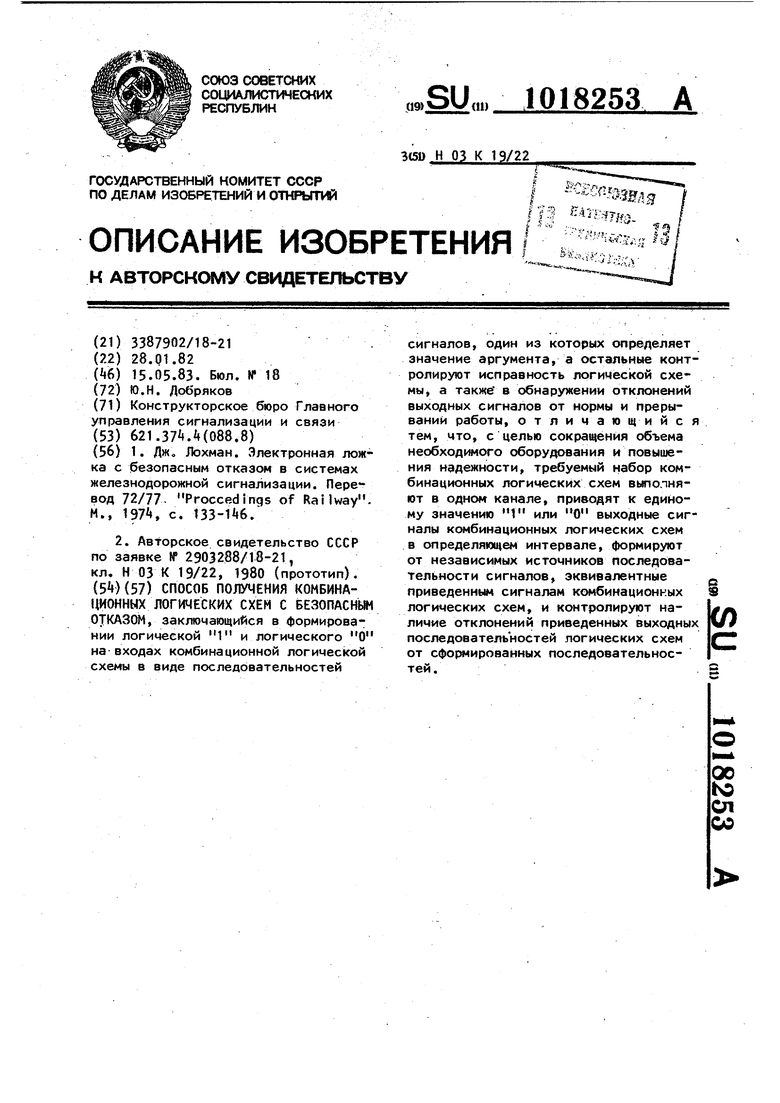

На фиг. 1 приведена реализация двух комбинационных логических схем, одна из которых соответствует функции у .®х 3 а другая фyнкJ.JИЯ

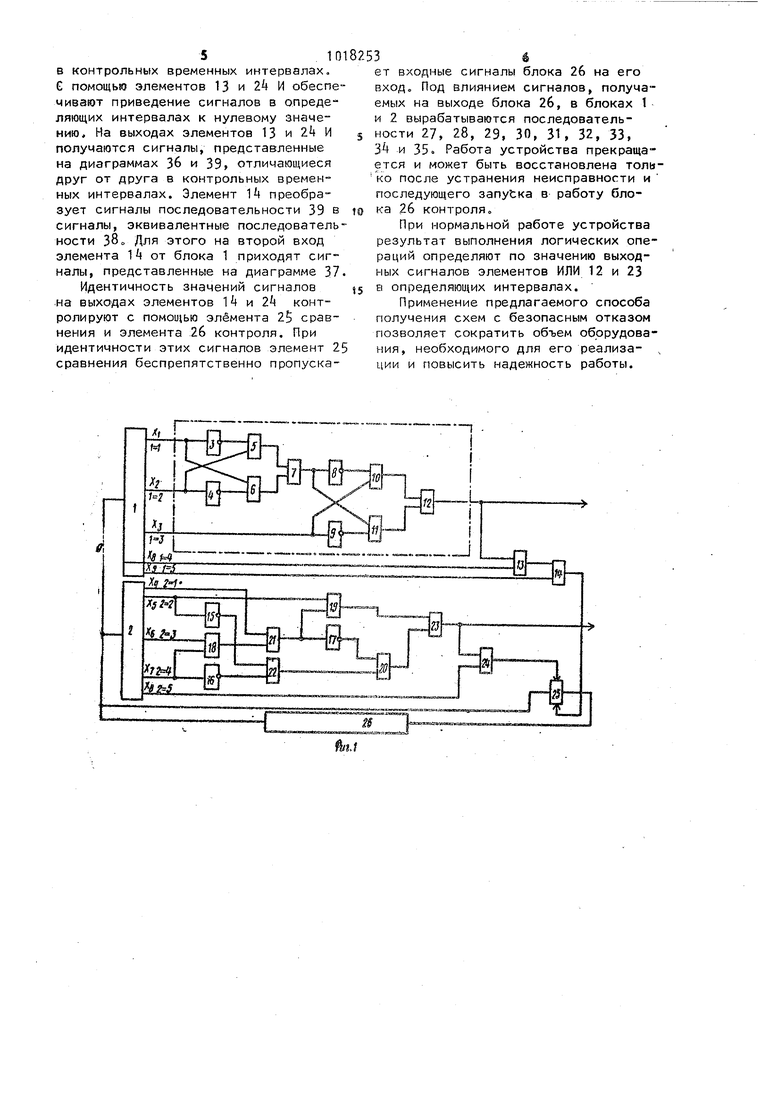

Уг 4) (5 Чна фиг. 2 приведены временные диаграммы работы устройства.

На фиг. 1 приняты следующие обозначения: блоки 1 и 2 формирования входных последовательностей, выходы , , , 1 и блока 1 формирования входных последовательностей, выходы - блока 2 формирования входных последовательностей, элементы 3 и it НЕ; 5 и 6 И; 7 ИЛИ; 8 и 9 НЕ; 10 и 11 И; 12 ИЛИ; элемент 13 И; элемент 1 i ИСКЛОЧАКЛЧЕЕ ИЛИ, элементы 15, 16 и 17 НЕ; элементы 18, 19 и 20 И; элементы 21 и 22, 23 ИЛИ;.элемент 2Л И, элемент 25 сравнения, блок 26 контроля.

Выходы , блока формирования входных последовательностей соединены соответственно со входами элементов 3 Ц НЕ, выходы которых соединены соответственно с первыми входами элементов 5 и 6 И, вторые входы которых соединены соответственно с выходами и блока 1; выходы элементов 5 и 6 И соединены со входа ми аемента 7 ИЛИ, выход которого соединен через элемент 8 НЕ с первым входом элемента 10 И и соединен с первым входом элемента 11 И, второй вход которого соединен с выходом элемента 9 НЕ, вход которого соединен с выходом 1-3 блока 1 и со вторым входом элемента 10 И, выход которого соединен с первый входом sneMeHta 12 ИЛИ, второй вход и выход которого со единены соответственно с выходом элемента 11 И и с первым входом элемента 1 3 И, второй вход и выход которого соединен соответственно с выходом 1вЛ блока 1 и с первым входом элемента U ИСКЛКНМЩЕЕ ИЛИ, второй вход и выход которого соединены соответственно с выходом IsS блока 1 и с первым входом элемента 25 сравнения, второй вход которого соединен с выходом элемента 2k И, входы которого соединены соответственно с выхо дом .5 блока . и с выходом элемента 23 ИЛИ, входы которого соединены соответственно элементов 19 и 20 И, входы последнего из которых соединены соответственно с выходом элемента 22 ИЛИ и с выходом элемента 17 НЕ вход которого соединен с первым входом элемента 19 И и с выходом элемента 21 ИЛИ, входы которого соединены соответственно с выходом 2 блока 2 и с выходом элемента 18 И, входы которого соединены соответственно с выходами 2аА, блока 2, выходы 2з2 и 2,4 блока 2 со единены соответственно через элементы 15 и 16 НЕ со входами элемента 22 ИЛИ, выход 2s2 блока 2 соединен со вторым вхсщон элемента 19 И, выход элемента 25 сравнения соединен со входом блока 26 контроля, выход которого соединен с третьим входом элемента 25 сравнения и соединен со входами блоков 1 и 2. На выходах 1а1, 1«5 блока 1 сигна лы обозначены соответственно как Х, Х, Х, Xg и Х. На выходах 2в.1 2в5 блока 2 сигналы обозначены соответственно как X Элементы 3 и t - 10, 11 и 12 реализу ют функцию . Элементы 15-23 реализ ют функцию У2. На фиг. 2 позициями 27, 28 и 29 показаны последовательности, формиру емые блоком 1 на входах - 3-3. П зициями 30, 31, 32 и 33 показаны последовагельности, формируемые блоком 22 на выходах 2а1 - 2s4. Позицией 3 показана последовател ность, получаемая на выходе элемента 12 ИЛИ при нормальной работе комбицационной логической схемы (КЛС, реализующей функцию У. о Позицией 35 показана последовательность, получаемая на выходе элемента 23 ИЛИ при нормальной работе КЛС, реализующей функцию УЗ.. Позицией 36 и 37 показаны последовательности, формируемые на выходах , 2&5 блоков 1 и 2 со.ответственно и на выходе Ijs5 блока 1. Позицией 38 показана последовательность, получаемая на выходе элемента Л И.. Позицией 39 показана последовательность, получаемая на выходе элемента 13 И. Последовательности сигналов, снимаемые с выходов КЛС, реализующих функции У , У, являются независимы и по неисправностям, т.е. неиспр,авность любого элемента, формирующего одну последовательность, не мсякет привести к появлению отклонений в значениях сигналов другой последовательности. Это свойство выходных последоватльностей КЛС, реализующих функции Уу и Уд, получают благодаря тому, что входные последовательности для них формируют отдельными блоками 1 и 2 и исключают все .возможные связи между схемами. 8 соответствии с аргументами выполняемых функций У и У блоки 1 и 2 вырабатывают последовательности 27, 28, 29, 30, 31, 32 и 33. Значения сигналов в определяющих интервалах этих последовательностей соответствуют значению аргументов. Сигналы в остальных семи временных интервалах составляют диагностический тест схе-. мы (фиг. 2). В результате на выходах КЛС, реализующих функции.У и У, в определяощем интервале получают значения сигналов, соответствующие значениям выполняемых функций. Особенностью выходных сигналов в контрольных временных интервалах является то, что при отсутствии сбоев в составе схемы их значения соответствуют знамениям, изобра«енным на диаграммах 3 и 35. Любое же одиночное нарушение в составе схемы приводит к появлению отклонений значений выходных сигналов, хотя бы в одном из контрольных интервлов ло в одном из контрольных интервалов по отношению к сигналам нормально работаюи ей схемы. Для выполнения этого требования при формировании последовательностей 27, 28, 29, 30, 31, 32 и 33 можно воспользоваться алгоритмом для отыскания минимального теста схемы. Из диаграмм 3 и 35 видно, что значения функций У и У. не всегда совпадают как в определяющем, и

в контрольных временных интервалах. С помощью элементов 13 и 24 И обеспечивают приведение сигналов в определяющих интервалах к нулевому значению. На выходах элементов 13 и 2 И получаются сигналы, представленные на диаграммах Зб и 39 отличающиеся друг от друга в контрольных временных интервалах. Элемент 14 преобразует сигналы последовательности 39 в сигналы, эквивалентные последовательности Для этого на второй вход элемента 14 от блока 1 приходят сигналы, представленные на диаграмме 37.

Идентичность значений сигналов на выходах элементов 14 и 24 контролируют с помощью элемента 25 сравнения и элемента 26 контроля. При идентичности этих сигналов элемент 25 сравнения беспрепятственно пропускает входные сигналы блока 2б на его вход. Под влиянием сигналов, получаемых на выходе блока 2б, в блоках 1 и 2 вырабатываются последовательности 27, 28, 29, 30, 31, 32, 33, 34 и 35. Работа устройства прекращается и может быть восстановлена толико после устранения неисправности и последующего запуЬка в работу блока 26 контроля.

При нормальной работе устройства результат выполнения логических операций определяют по значению выходных сигналов элементов ИЛИ 12 и 23 в определяющих интервалах.

Применение предлагаемого способа получения схем с безопасным отказом позволяет сократить объем оборудования, необходимого для его реализации и повысить надежность работы.

| название | год | авторы | номер документа |

|---|---|---|---|

| Способ получения надежных комбинационных логических структур | 1982 |

|

SU1061261A1 |

| Способ получения комбинационных логических схем с безопасным отказом | 1980 |

|

SU892731A1 |

| Преобразователь кода взаимоисключающих двоичных сигналов в импульсные широтно-модулированные сигналы | 1974 |

|

SU748865A1 |

| Самокорректирующееся дискретное устройство | 1989 |

|

SU1716521A1 |

| Устройство для сжатия информации | 1987 |

|

SU1474716A1 |

| Систолический автомат | 1990 |

|

SU1732340A1 |

| СПОСОБ ДИАГНОСТИКИ КОМБИНАЦИОННЫХ ЛОГИЧЕСКИХ СХЕМ | 1991 |

|

RU2017207C1 |

| Цифровой функциональный преобразователь | 1980 |

|

SU1099317A1 |

| Устройство для коррекции положения резца на станке с программным управлением | 1981 |

|

SU983651A1 |

| МНОГОПРОЦЕССОРНАЯ ВЕКТОРНАЯ ЭВМ | 1995 |

|

RU2113010C1 |

СПОСОБ ПОЛУЧЕНИЯ КОМБИНАЦИОННЫХ ЛОГИЧЕСКИХ СХЕМ С БЕЗОПАСНЫМ ОТКАЗСЖ, заключающийся в формировании логической 1 и логического О на входах комбинационной логической схемы в виде последовательностей сигналов, один из которых определяет значение аргумента, а остальные контролируют исправность логической схемы, а также в с наружении отклонений выходных сигналов от нормы и прерываний работы, отличающийся тем, что, с целью сокращения объема необход оборудования и повышения надежности, требуемый набор комбинационных логических схем выполняют в одном канале, приводят к единому значению 1 или О выходные сигналы комбинационных логических схем в определяющем интервале, формируют от независимых источников последовательности сигналов, эквивалентные приведенным сигналам комбинационных логических схем, и контролируют наличие отклонений приведенных выходных последовательностей логических схем от сформированных последовательностей.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Дж, Лохман | |||

| Электронная ложка с безопасным отказом в системах железнодорожной сигнализации | |||

| Термосно-паровая кухня | 1921 |

|

SU72A1 |

| М., 197, с | |||

| Топочная решетка для многозольного топлива | 1923 |

|

SU133A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Авторское свидетельство СССР по заявке № 2903288/18-21, кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1983-05-15—Публикация

1982-01-28—Подача