. - -1 ; . .

Изобретение относится к вычислиiТельной технике и предндзначено для ;преобразования прямоугольных координат а полярные и наоборот.

Известно устройство, которое содержит синусный и косинусный преобразователи, на одни входы которых подаются проекции вектора, а на вторые - код аргумента из регистра. Выходы синусного и косинусного преобразователей соединены со входами сумматора, выход которого через селектор знака подсоединен ко входу анализатора. Анализатор совместно с логическим блоком осуществляет поразрядное Сформирование кода в регистре аргу;мента. Происходит автоматическая отработка аргумента вектора, а напряжение на выходе сумматора соответствует значению модуля 1.

Недостатком этого устройства являются ограниченные функциональные .возможности.

Наиболее близким по технической сущности к изобретению является уст-, ройство, содержащее суммирующие и реверсивные счетчики, генератор импульсов, счетчик аргумента, соединенный с шифратором и различителем квадрантов, ключи, блок управления, схему переноса, блоки умножения, одни из входов которых соединены с шифратором, другие - через первый ключ с генератором импульсов и через реверсивный счетчик - со схемой переноса, подключенной к суммирующим счетчикам, а выходы блоковумножения соединены с одним из входов второго и третьего ключей, подключенных к суммирующим счетчикам и блоку управления, соединенному с реверсивным счетчиком, схемой переноса, счетчи-. JJJ ком аргумента и первым ключом, и компаратор, входы которого соединены с одним из выходов второго и третьего ключей, а выход - с блоком управле-, ния 2Э. Недостатком данного устройства является низкое быстродействие, обус ловленное используемым методом форми рования кодов результата, а также методом ввода исходных данных в умно жители. Например, ввод проекций X и Y вектора R в блок умножения осуществляется следующим образом. Код NX заносится в двоичный счетчик, находящийся в режиме вычитания, затем на счетный вход счетчика поступают импульсы с генератора импульсов, которые одновременно поступают на блоки умножения. Содержимое счётчика уменьшается и наконец полностью обнуляется, по этому сигналу устройств управления закрывает соответствующий ключ, и поступление импульсов прекра щается. Аналогичная операция повторя ется с кодом NU и далее при формировании кода N аргумента. При этом в каждом такте формирования кода , описанная процедура повторяется и так до окончательного формирования кода . Недостатком данного устройства является также зависимость врем ни преобразования от величины исходных данных. Целью изобретения является повышение быстродействия устройства. Поставленная цель достигается тем что в устройство для преобразования координат, содержащее блок управления , дешифратор квадрантов, первую схему сравнения, два коммутатора, дв блока умножения, первые входы которы соединены соответственно с выходами шифратора, выходы блоков умножения подключены соответственно к входам первого и второго коммутаторов, управляющие входы которых соединены с первым выходом блока управления, пер вый и второй входы дешифратора квадрантов являются первым и вторым управляющими входами устройства, введе ны вторая и третья схемы сравнения, третий, четвертый, пятый и шестой коммутаторы, сумматор, четыре регист ра, три распределителя, три цифроаналоговых преобразователя, первые ВХОДЫ которых соединены с входом опо

ного напряжения устройства, вторые входы подключены соответственно к выходам первого, второго и третьего регистров, входы которых соединены соответственно с выходами первого, второго и третьего распределителей, информационные входы первого, второго, третьего и четвертого регистров

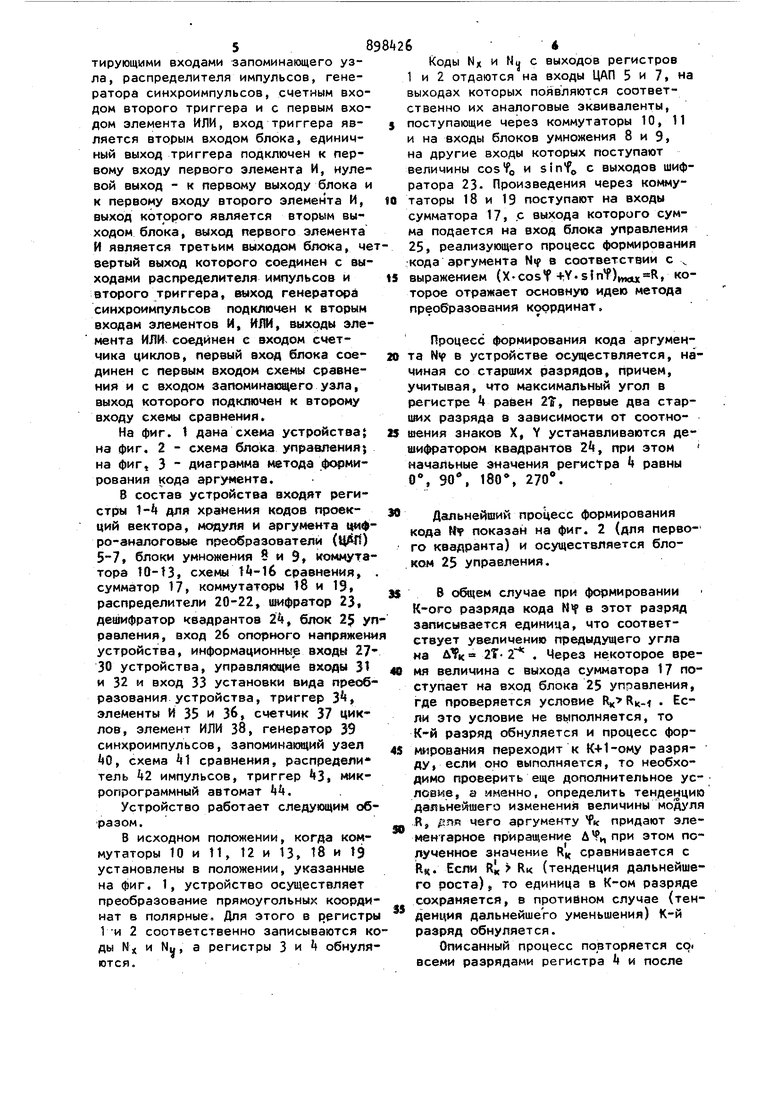

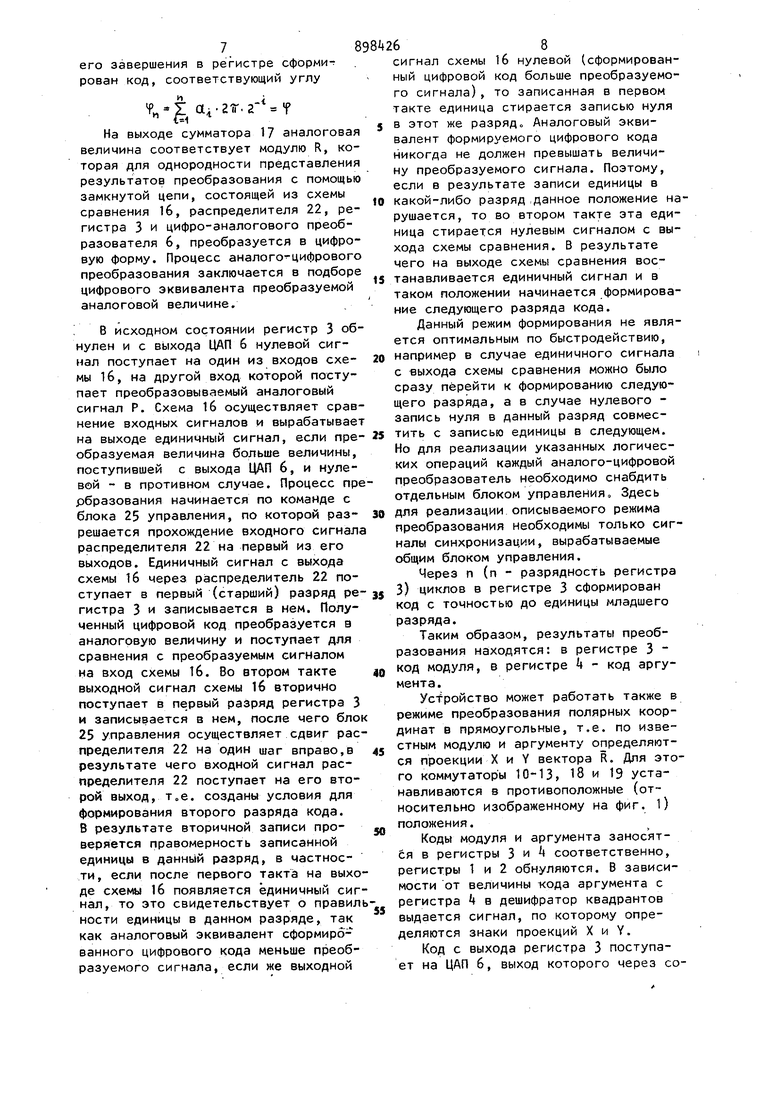

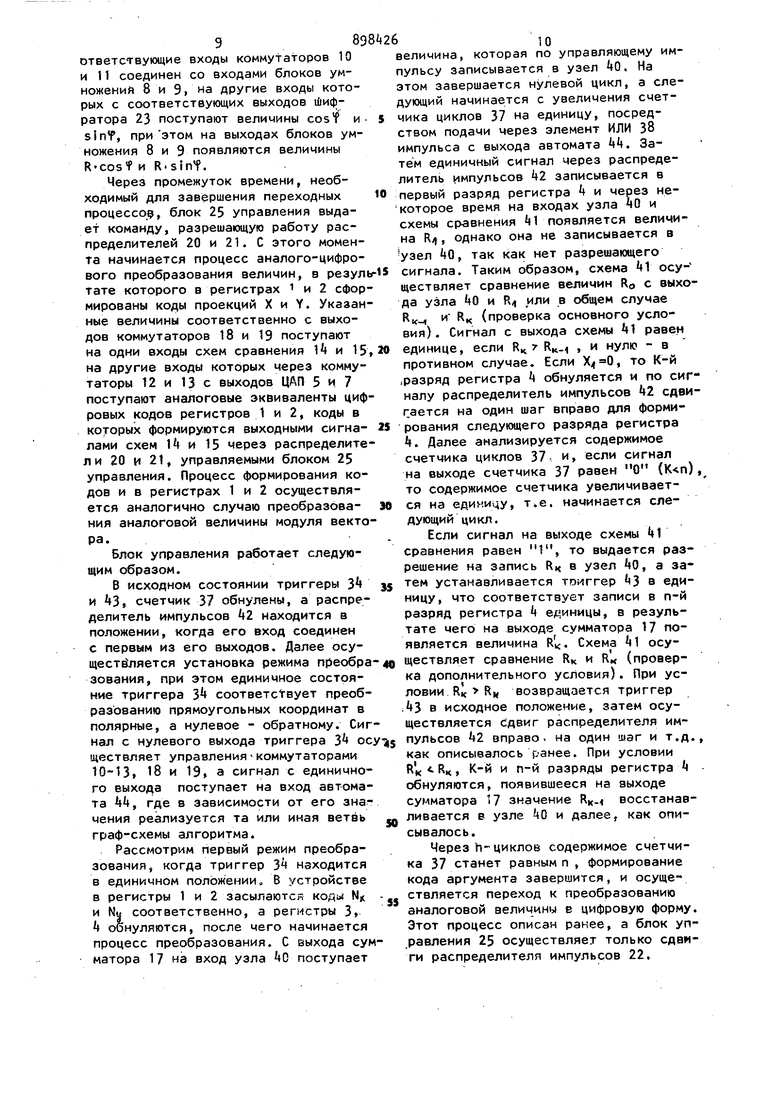

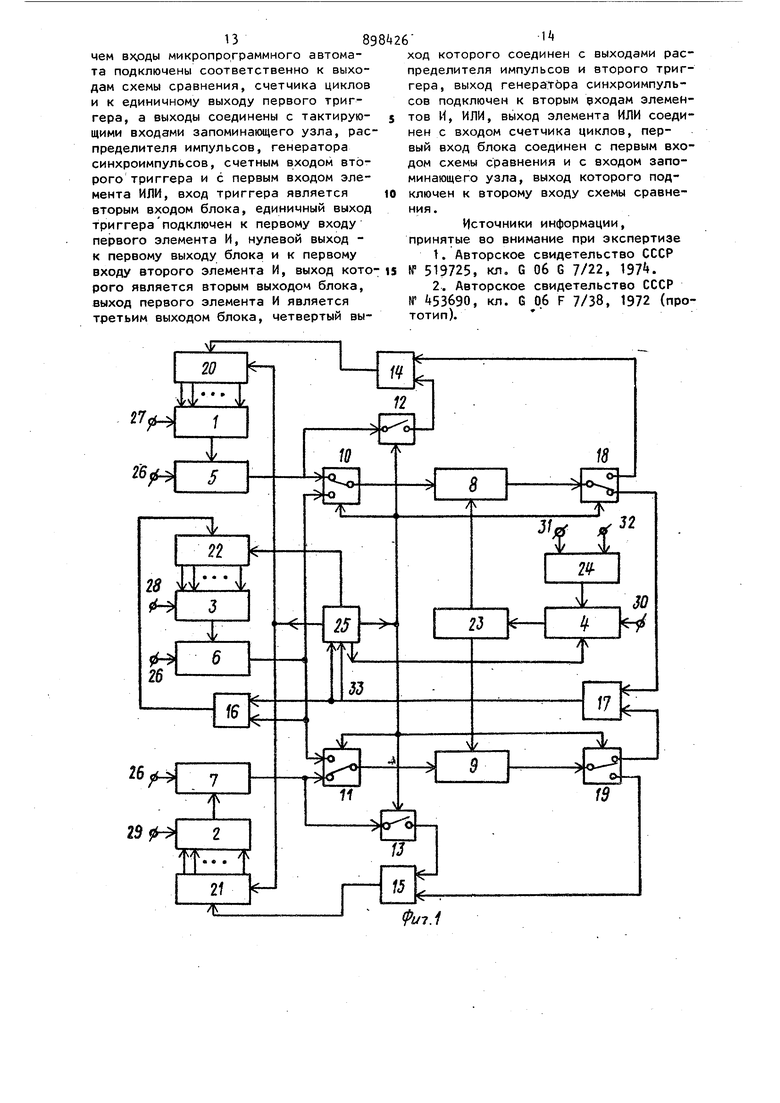

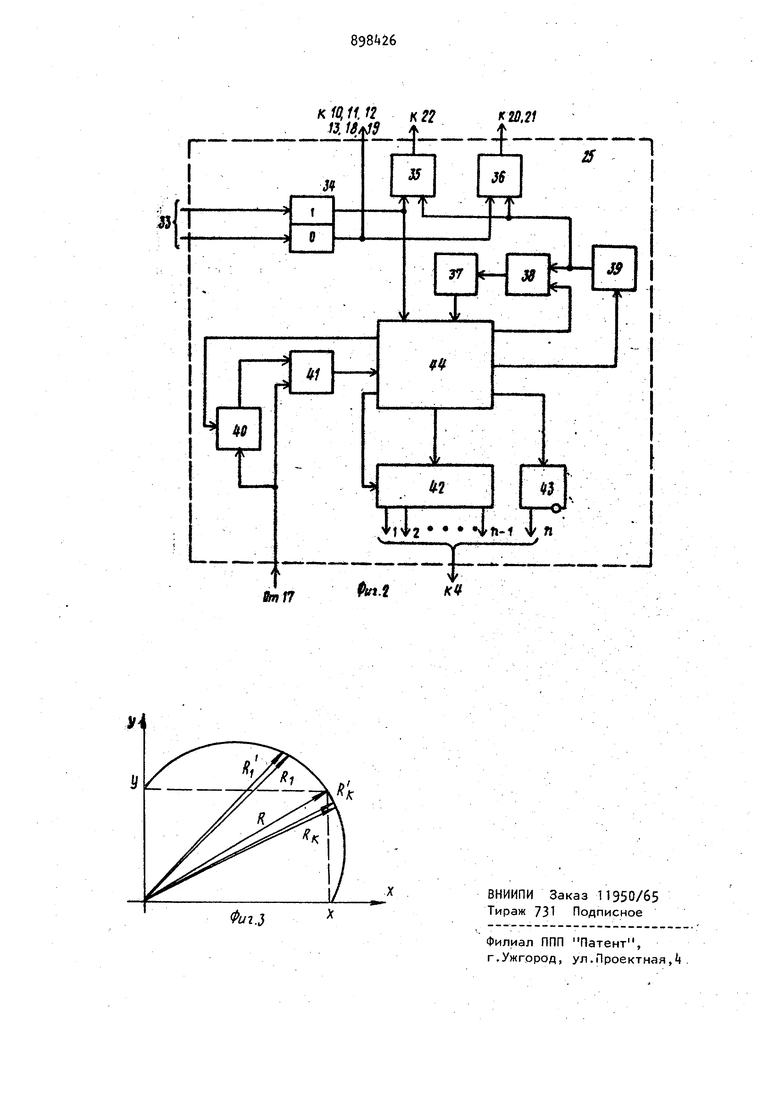

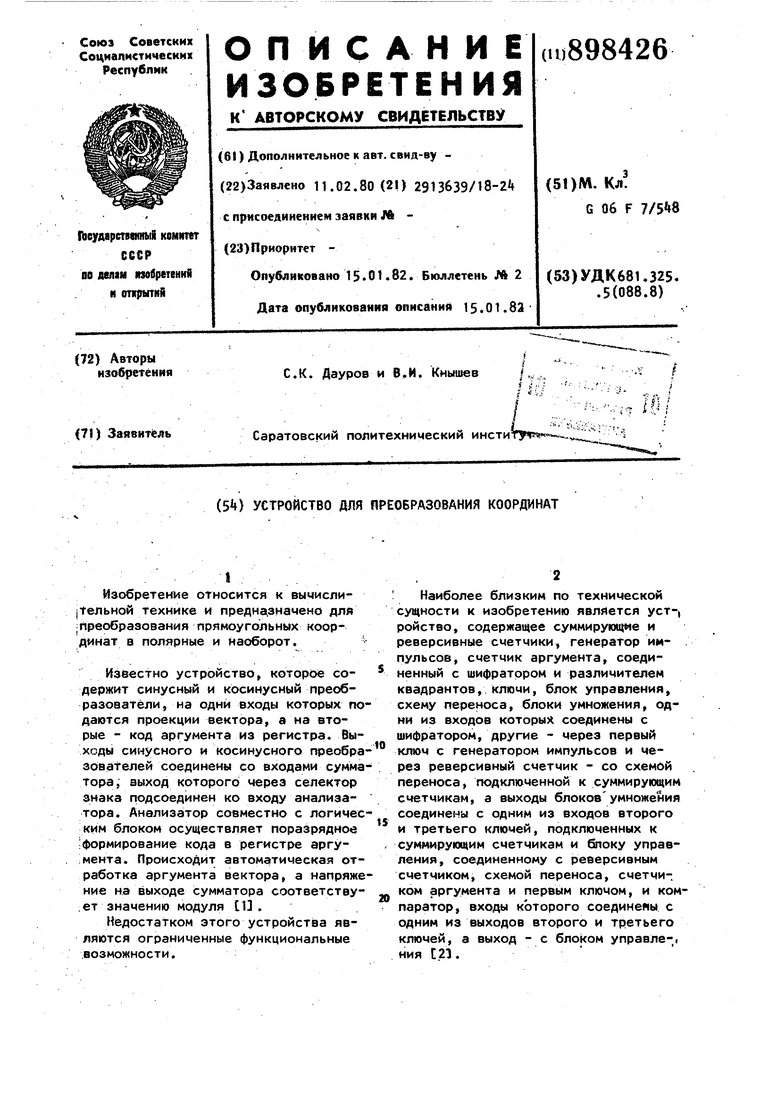

синхроимпульсов, запоминающий узел, схему сравнения, микропрограммный автомат и распределитель импульсов, причем входы микропрограммного автомата подключены соответственно к выходам схемы сравнения, счетчика циклов и к единичному выходу первого триггера, а выходы соединены с такЯВЛЯЮТСЯ соответственно первым, вторым, третьим и четвертым информационными входами устройства, выходы распределителей соединены соответственно с выходами первой, второй и третьей схем сравнения, выход первого цифро-аналогового преобразователя подключен к входу третьего коммутатора и к первому входу четвертого коммутатора, выход которого соединен с вторым входом первого блока умножения, выход второго цифро-аналогового преобразователя подключен к входу пятого коммутатора, к первому входу шестого коммутатора, выход которого соединен с вторым входом второго блока умножения, выход третьего цифро-аналогового преобразователя подключен к вторым входам четвертого и шестого коммутаторов и к первому входу третьей схемы сравнения, второй вход которой и первый вход блока управления соединены с выходом сумматора, входы первой схемы сравнения соединены соответственно с первым выходом первого коммутатора и с выходом третьего коммутатора, входы второй схемы сравнения соединены соответственно с первым выходом второго коммутатора и с выходом пятого коммутатора, входы сумматора соединены соответственно с вторыми выходами первого и второго коммутаторов, выход дешифратора квадрантов подключен к входу четвертого регистра, выход которого соединен с входом шифратора, управляющие входы третьего, четвертого, пятого и шестого коммутаторов подключены к первому выходу блока управления, второй выход которого соединен с управляющими входами первого и второго распределителей , третий и четвертый выходы блока управления подключены соответственно к управляющим входам третьего распределителя и четвертого регистра, второй вход блока управления являетя входом установки вида преобразования устройства. 1. Кроме того, в устройстве блок управления содержит триггеры, элементы и, ИЛИ, счетчик циклов, генератор 58 тирующими входами запоминающего узла, распределителя импульсов, генератора синхроимпульсов, счетным входом второго триггера и с первым входом элемента ИЛИ, вход триггера является вторым входом блока, единичный выход триггера подключен к первому входу первого элемента И, нулевой выход - к первому выходу блока и к первому входу второго элемента И, выход которого является вторым выходом блока, выход первого элемента И является третьим выходом блока, че вертый выход которого соединен с выходами распределителя импульсов и второго триггера, выход генератора синхроимпульсов подключен к вторым входам элементов И, ИЛИ, выходы элемента ИЛИ соединен с входом счетчика циклов, первый вход блока соединен с первым входом схемы сравнения и с входом запоминащего узла, выход которого подключен к второму входу схемы сравнения. На фиг. 1 дана схема устройства; на фиг. 2 - схема блока управления; на фиг, 3 диаграмма метода формирования кода аргумента. 8 состав устройства входят регистры 1-i для хранения кодов проекций вектора, модуля и аргумента цифро-аналоговые преобразователи (ЦДИ) 5-7, блоки умножения 8 и 9t коммутатора 10-t3, схемы сравнения, сумматор 17, коммутаторы 18 и 19, распределители 20-22, шифратор 23, дешифратор квадрантов 24, блок 2$ уп равления, вход 26 опорного напряжени устройства, информационные входы 27 30 устройства, управляющие входы 31 и 32 и вход 33 установки вида преобразования устройства, триггер 3, элементы И 35 и Зб, счетчик 37 циклов, элемент ИЛИ 38, генератор 39 синхроимпульсов, запоминакадий узел tO, схема 1 сравнения, распределитель k2 импульсов, триггер 3, микропрограммный автомат kk, Устройство работает следующим образом. В исходном положении, когда коммутаторы 10 и 11, 12 и 13, 18 и 19 установлены в положении, указанные на фиг. 1, устройство осуществляет преобразование прямоугольных координат в полярные. Для этого в регистры 1-и 2 соответственно записываются ко ды Njt и NU, а регистры 3 и обнуля6Коды NX и NU с выходов регистров 1 и 2 отдаются на входы ЦАП 5 и 7, на выходах которых появляются соответственно их аналоговые эквиваленты, поступающие через коммутаторы 10, 11 и на входы блоков умножения 8 и Э, на другие входы которых поступают величины cosfo и sinf с выходов шифратора 23- Произведения через коммутаторы 18 и 19 поступают на входы сумматора 17, с выхода которого сумма подается на вход блока управления 25, реализующего процесс формирования :кода аргумента Nif в соответствии с выражением (Х cosf- :Y.sfnH),,, которое отражает основную идею метода преобразования координат. Процесс формирования кода аргумента в устройстве осуществляется, начиная со старших разрядов, причем, учитывая, что максимальный угол в регистре k равен 2, первые два старших разряда в зависимости от соотношения знаков X, Y устанавливаются дешифратором квадрантов 2Ц при этом начальные значения peгиctpa t равны 0°, 90, 180, 270. Дальнейши 1 процесс формирования кода №т показан на фиг. 2 (для первого квадранта) и осуществляется блоком 25 управления. 8 о&цем случае при формировании К-ого разряда кода N в этот разряд записывается единица, что соответствует увеличению предыдущего угла на Д% 2Т- 2 . Через некоторое время величина с выхода сумматора 17 поступает на вход блока 25 управления, где проверяется условие R,( R. . Если это условие не выполняется, то К-й разряд обнуляется и процесс форм фования переходит к К- -1-ому разряду, если оно выполняется, то необходимо проверить еще дополнительное условие, а именно, определить тенденцию дальнейшего изменения величины мод1ля .R, пя чего аргументу fic придают элементарное приращение при этом по лученное значение R сравнивается с RK. Если Rl, RK (тенденция дальнейшего роста), то единица в К-ом разряде сохраняется, в противном случае (тенденция дальнейшего уменьшения) К-й разряд обнуляется. Описанный процесс повторяется со. всеми разрядами регистра и после его завершения в регистре сформи-г рован код, соответствующи11 углу a4-2ir. На выходе сумматора 17 аналоговая величина соответствует модулю R, которая для однородности представления результатов преобразования с помощью замкнутой цепи, состоящей из схемы сравнения 16, распределителя 22, регистра 3 и цифро-аналогового преобразователя 6, преобразуется в цифровую форму. Процесс аналого-цифрового преобразования заключается в подборе цифрового эквивалента преобразуемой аналоговой величине. . В исходном состоянии регистр 3 об нулен и с выхода ЦАП 6 нулевой CHI- нал поступает на один из входов схемы 16, на другой вход которой поступает преобразовываемый аналоговый сигнал Р. Схема 1б осуществляет срав нение входных сигналов и вырабатывае на выходе единичный сигнал, если пре образуемая величина больше величины, поступившей с выхода ЦАП 6, и нулевой - в противном случае. Процесс пр рбразования начинается по команде с блока 25 управления, по которой разрешается прохождение входного сигнал распределителя 22 на первый из его выходов. Единичный сигнал с выхода схемы 16 через распределитель 22 поступает в первый (старший) разряд ре гистра 3 и записывается в нем. Полученный цифровой код преобразуется в аналоговую величину и поступает для сравнения с преобразуемым сигналом на вход схемы 16. Во втором такте выходной сигнал схемы 1б вторично поступает в первый разряд регистра 3 и записывается в нем, после чего бло 25 управления осуществляет сдвиг рас пределителя 22 на один шаг вправо,в результате чего входной сигнал распределителя 22 поступает на его второй выход, т.е. созданы условия для Формирования второго разряда кода. В результате вторичной записи проверяется правомерность записанной единицы в данный разряд, в частности , если после первого такта на выхо появляется единичный сигде схемы нал, то это свидетельствует о правил ности единицы в данном разряде, так как аналоговый эквивалент сформиро- ванного цифрового кода меньше преобразуемого сигнала, если же выходной 68 сигнал схемы 1б нулевой (сформированный цифровой код больше преобразуемого сигнала) , то записанная в первом такте единица стирается записью нуля в этот же разряд о Аналоговый эквивалент формируемого цифрового кода никогда не должен превышать величину преобразуемого сигнала. Поэтому, если в результате записи единицы в какой-либо разряд .данное положение нарушается, то во втором такте эта единица стирается нулевым сигналом с выхода схемы сравнения. В результате чего на выходе схемы сравнения востанавливается единичный сигнал и в таком положении начинается формирование следующего разряда кода. Данный режим формирования не является оптимальным по быстродействию, например в случае единичного сигнала с выхода схемы сравнения можно было сразу перейти к формированию следующего разряда, а в случае нулевого запись нуля в данный разряд совместить с записью единицы в следующем. Но для реализации указанных логических операций каждый аналого-цифровой преобразователь необходимо снабдить отдельным блоком управления. Здесь для реализации описываемого режима преобразования необходимы только сигналы синхронизации, вырабатываемые общим блоком управления. Через п (п - разрядность регистра 3) циклов в регистре 3 сформирован код с точностью до единицы младшего разряда. Таким образом, результаты преобразования находятся: в регистре 3 код модуля, в регистре k - код аргумента. Устройство может работать также в режиме преобразования полярных координат в прямоугольные, т.е. по известным модулю и аргументу определяются проекции X и Y вектора R. Для этого коммутаторы 10-13, 18 и 19 устанавливаются в противоположные (относительно изображенному на фиг. 1) положения. Коды модуля и аргумента заносят6я в регистры 3 и 4 соответственно, регистры 1 и 2 обнуляются. В зависимости от величины кода аргумента с Ц в дешифратор квадрантов регистра выдается сигнал, по которому определяются знаки проекций X и Y. Код с выхода регистра 3 поступает на ЦАП 6, выход которого через соответствующие входы коммутаторов 10 и 11 соединен со входами блоков умножений 8 и 9, на другие входы которых с соответствующих выходов Шифратора 23 поступают величины cosl и sinf, приэтом на выходах блоков умножения 8 и 9 появляются величины RCosf и R.sirtf. Через промежуток времени, необходимый для завершения переходных процессор, блок 25 управления выдает команду, разрешающую работу распределителей 20 и 21. С этого момента наминается процесс аналого-цифрового преобразования величин, в резул тате которого в регистрах 1 и 2 сфор мированы коды проекций X и Y. Указан ные величины соответственно с выходов коммутаторов 18 и 19 поступают на одни входы схем сравнения Н и 15 на другие входы которых через коммутаторы 12 и 13 с выходов ЦАП 5 И 7 поступают аналоговые эквиваленты циф ровых кодов регистров J и 2, коды в которых формируются выходными сигналами схем И и 15 через распределите ли 20 и 2t, управляемыми блоком 25 управления. Процесс формирования кодов и в регистрах 1 и 2 осуществляется аналогично случаю преобразования аналоговой величины модуля векто ра. Блок управления работает следующим образом. В исходном состоянии триггеры 3 и 3, счетчик 37 обнулены, а распределитель импульсов Ц2 находится в положении, когда его вход соединен с первым из его выходов. Далее осуществляется установка режима п0еобра зования, при этом единичное состояние триггера 3 cooTBeTctsyeT преобразованию прямоугольных координат в полярные, а нулевое - обратному. Сиг нал с нулевого выхода триггера З oc ществляет управлениякоммутаторами 10-13f 18 и 19, а сигнал с единичного выхода поступает на вход автомата kk, где в зависимости от его значения реализуется та или иная ветвь граф-схемы алгоритма. Рассмотрим первый режим преобразования, когда триггер 3ч находится в единичном положении« В устройстве в регистры 1 и 2 засылаются коды М и NIJ соответственно, а регистры 3, k обнуляются, после чего начинается процесс преобразования. С выхода сум матора 17 на вход узла tO поступает еличина, которая по управляющему имульсу записывается в узел 0. На том завершается нулевой цикл, а слеующий начинается с увеличения счетчика циклов 37 на единицу, посредством подачи через элемент ИЛИ 38 импульса с выхода автомата . Затем единичный сигнал через распределитель импульсов k2 записывается в первый разряд регистра и чеоез некоторое время на входах узла ЧО и схемы сравнения il появляется величина R/I, однако она не записывается в узел 40, так как нет разрешающего сигнала. Таким образом, схема осуществляет сравнение величин RO с выхода узла 0 и R или в общем случае RK- и RK (проверка основного условия). Сигнал с выхода схемы tt равен единице, если R т- RK- , и нулю - в противном случае. Если , то К-й .разряд регистра обнуляется и по сигналу распределитель импульсов сдвигается на один шаг вправо для формирования следующего разряда регистра М. Далее анализируется содержимое счетчика циклов 37 и, если сигнал на выходе счетчика 37 равен О (), то содержимое счетчика увеличивается на едиии;4У, т.е. начинается следующий цикл. Если сигнал на выходе схемы 1 сравнения равен 1, то выдается разрешение на запись R| в узел , а затем устанавливается тоиггер в единицу, что соответствует записи в п-й разряд регистра единицы, в результате чего на выходе сумматора 17 появляется величина R. Схема k 1 осуществляет сравнение RK и RK (проверка дополнительного условия). При условим R R,, возвращается триггер 3 в исходное положение, затем осуществляется Сдвиг распределителя импульсов k2 вправо- на один шаг и т.д. как описывалось ранее. При условии RK , К-й и п-й разряды регистра i обнуляются, появившееся на выходе сумматора 17 значение R.f восстанавливается в узле 0 и далее, как описывалось. Через h циклов содержимое счетчика 37 станет равным п , формирование кода аргумента завершится, и осуществляется переход к преобразованию аналоговой величины е цифровую форму. Этот процесс описан ранее, а блок управления 25 осуществляет только сдвиги распределителя импульсов 22, Счетчик циклов 37 реализован так, что когда его содержимое становится равным п , на его выходе появляется сигнал, а следующий импульс, подавае мый на счетчик, обнуляет его. Запускается генератор синхроимпульсов 39, импульсы которого через элемент ИЛИ 38 поступают на вход сметчика 37, а также элемент И 35 разрешенный едини ным уровнем с триггера 3, на управляющий вход распределителя 22, содер жимое счетчика циклов станет равным п и микропрограммный автомат 4 останавливает генератор 39, затем, уве личивая счетчик 37 на единицу, обнуляет его и передает управление на за дание нового режима преобразования. Процесс преобразования полярных координат в прямоугольные проходит значительно проще, чем рассмотренный а блок управления осуществляет тольк сдвиг распределителей импульсов 20 и 21, управляющие импульсы на которые подаются .одновременно от генератора синхроимпульсов 39 через элемент И Зб разрешенный единичным уровнем нулевого выхода триггера 3. Формула изобретения 1. Устройство для преобразования координат, содержащее блок управления дешифратор квадрантов, первую схему сравнения, два коммутатора, два блока умножения, первые входы которых соединены соответственно с выходами шифратора, выходы блоков умножения подключены соответственно к информационным входам первого и второго коммутаторов, управляющие входы которых соединены с первым выходом блока управления, первый и второй входы дешифратора квадрантов являются первым и вторым управляющими входами устройства, отличающееся тем, что, с целью повышения быстродействия в него введены вторая и третья схемы сравнения, третий, четвертый, пятый и шестой коммутаторы, сумматор, четыре регистра, три распределителя, три цифро-аналоговых преобразователя, первые входы которых соединены с входом опорного напряжения устройства вторые входы подключены соответственего регистров, входы которых соединены соответственно с выходами первого, второго и третьего распределителей. информационные входы первого, второго, третьего и четвертого регистров являются соответственно первым, вторым, третьим и четвертым информационными входами устройства, входы распределителей соединены соответственно с выходами первой, второй и третьей схем сравнения, выход первого цифроаналогового преобразователя подключен к информационному входу третьего коммутатора и к первому информационному входу четвертого коммутатора, выход которого соединен с вторым входом первого -блока умножения, выход второго цифро-аналогового преобразователя подключен к информационному входу пятого коммутатора и к первому информационному входу шестого коммутатора, выход которого соединен с вторым входом второго блока умножения, выход третьего цифро-аналогового преобразователя подключен к вто рым информационным входам четвертого и шестого коммутаторов и к первому входу третьей схемы сравнения, второй вход которой и первый вход блока управления соединены с выходом сумматора, входы первой схемы сравнения соединены соответственно с первым выходом первого коммутатора и с выходом третьего коммутатора, входы второй схемы сравнения соединены соответственно с первым выходом второго коммутатора и.с выходом пятого коммутатора, входы сумматора соединены соответственно с вторыми выходами первого и второго коммутаторов, выход дешифратора квадрантов подключен к входу четвертого регистра, выход которого соединен с входом щифратора, управляющие входы третьего, четвертого, пятого и шестого коммутаторов подключены к первому выходу блока управления, второй выход которого соединен с управляющими входами первого и второго р.аспределителей, третий и четвертый выходы блока управления подключены соответственно к управляющим входам третьего распределителя и четвертого регистра, второй вход блока управления является входом установки йида преобразования устройства. 2. Устройство по п. 1, отли-и чающееся тем, что блок управения содержит триггеры, элементы И, ЛИ, счетчик циклов, генератор синроимпульсов, запоминаквдий узел, схеу сраанения, микропрограммный автоат и распределитель импульсов, причем ВХ.ОДЫ микропрограммного автомата подключены соответственно к выходам схемы сравнения, счетчика циклов и к единичному выходу первого триггера, а выходы соединены с тактирующими входами запоминающего узла, распределителя импульсов, генератора синхроимпульсов, счетным входом второго триггера и с первым входом элемента ИЛИ, вход триггера является вторым входом блока, единичный выход триггераподключен к первому входу первого элемента И, нулевой выход к первому выходу блока и к первому входу второго элемента И, выход кото рого является вторым выходом блока, выход первого элемента И является третьим выходом блока, четвертый выход которого соединен с выходами распределителя импульсов и второго три1- гера, выход генератора синхроимпульсов подключен к вторым входам элементов И, ИЛИ, выход элемента ИЛИ соединен с входом счетчика циклов, первый вход блока соединен с первым входом схемы сравнения и с входом запоминающего узла, выход которого подключен к второму входу схемы сравнения.

Источники информации, принятые во внимание при экспертизе

t. Авторское свидетельство СССР № 519725, кл, G Об G 7/22, 197.

2. Авторское свидетельство СССР N i 53690, кл. F 7/38, 1972 (прототип).

{

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой преобразователь координат | 1980 |

|

SU942004A1 |

| Устройство для вычисления элементарных функций | 1983 |

|

SU1160429A1 |

| Устройство для вычисления элементарных функций | 1983 |

|

SU1160454A1 |

| Обратимый преобразователь координат | 1982 |

|

SU1035617A1 |

| МНОГОКАНАЛЬНЫЙ АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 1973 |

|

SU384115A1 |

| Преобразователь угловых перемещений в код | 1985 |

|

SU1311024A1 |

| Устройство для преобразования полярных координат вектора в прямоугольные | 1978 |

|

SU771682A1 |

| Аппроксимирующий функциональный преобразователь | 1984 |

|

SU1205153A1 |

| Устройство для дискретного преобразования Фурье | 1984 |

|

SU1188751A1 |

| Функциональный преобразователь | 1982 |

|

SU1100621A1 |

ИтП

К

Авторы

Даты

1982-01-15—Публикация

1980-02-11—Подача