тий информационные входы которого соединены с выходами соответственно второго блока памяти и накапливающего сумматора, выход которого соединен с информационным входом выходного регистра, выход счетчика порядка соединен с адресным входом первого блока памяти, четвертый выход дешифратора циклов соединен с управляющим входом регистра функции, выход которого соединен с первым входом дешифратора признака, второй вход которого соединен с выходом входного регистра, управляющие входы регистра множителя, регистра множимого, сдвигателя множителя и мультиплексора соединены с выходами соответственно с первого по четвертый дешифратора признака, тактовый вход регистра сдвига соединен с тактовым входом устройства, выходы блоков памяти с третьего по шестой подключены к второму информационному входу накапливающего сумматора, выход мультиплексора подключен к информационному входу-регистра множителя, выход которого соединен с информационным входом сдвигателя множителя, выход которого соединен с первым входом матричного умножителя, второй вход которого соединен с выходом регистра множимого.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления элементарных функций | 1983 |

|

SU1160429A1 |

| Специализированный процессор | 1977 |

|

SU734705A1 |

| Специализированный процессор | 1983 |

|

SU1144117A1 |

| Специализированный процессор для вычисления элементарных функций | 1984 |

|

SU1265764A1 |

| Устройство для вычисления элементарных функций | 1984 |

|

SU1185329A1 |

| Специализированный процессор для вычисления элементарных функций | 1985 |

|

SU1330627A1 |

| Специализированный процессор | 1977 |

|

SU723581A1 |

| Специализированный процессор | 1981 |

|

SU1023339A1 |

| Преобразователь двоичных чисел в двоично-десятичные числа | 1980 |

|

SU941990A1 |

| Арифметическое устройство | 1978 |

|

SU687982A1 |

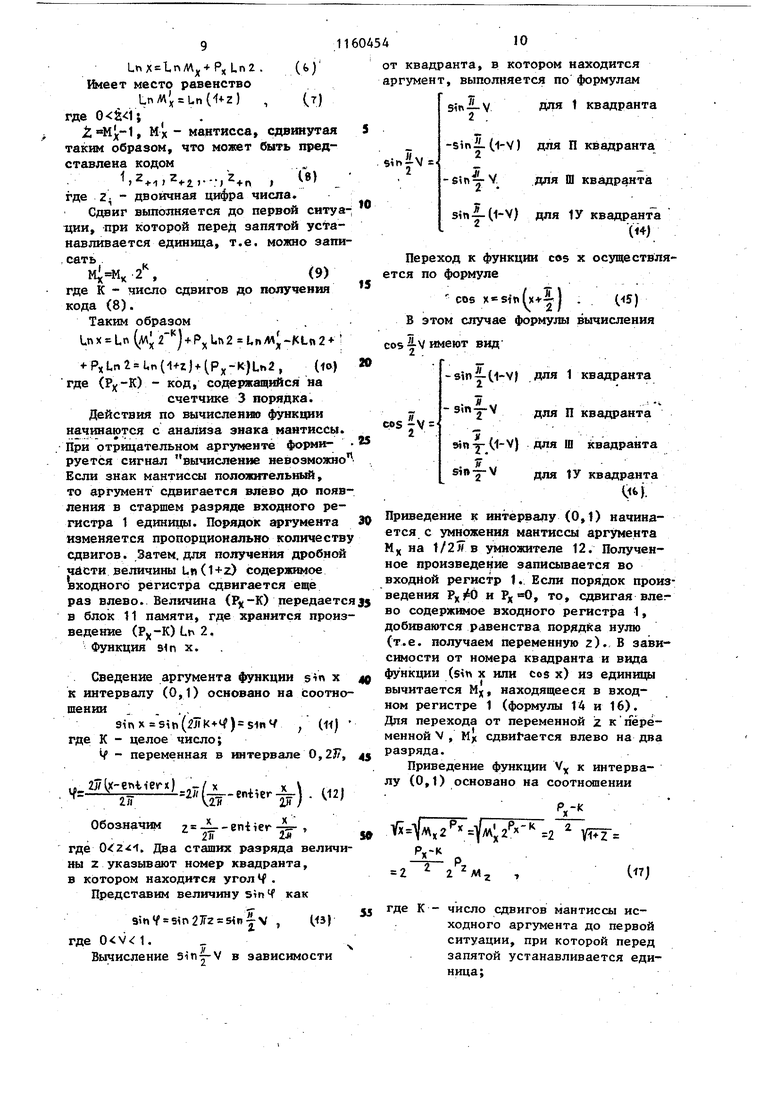

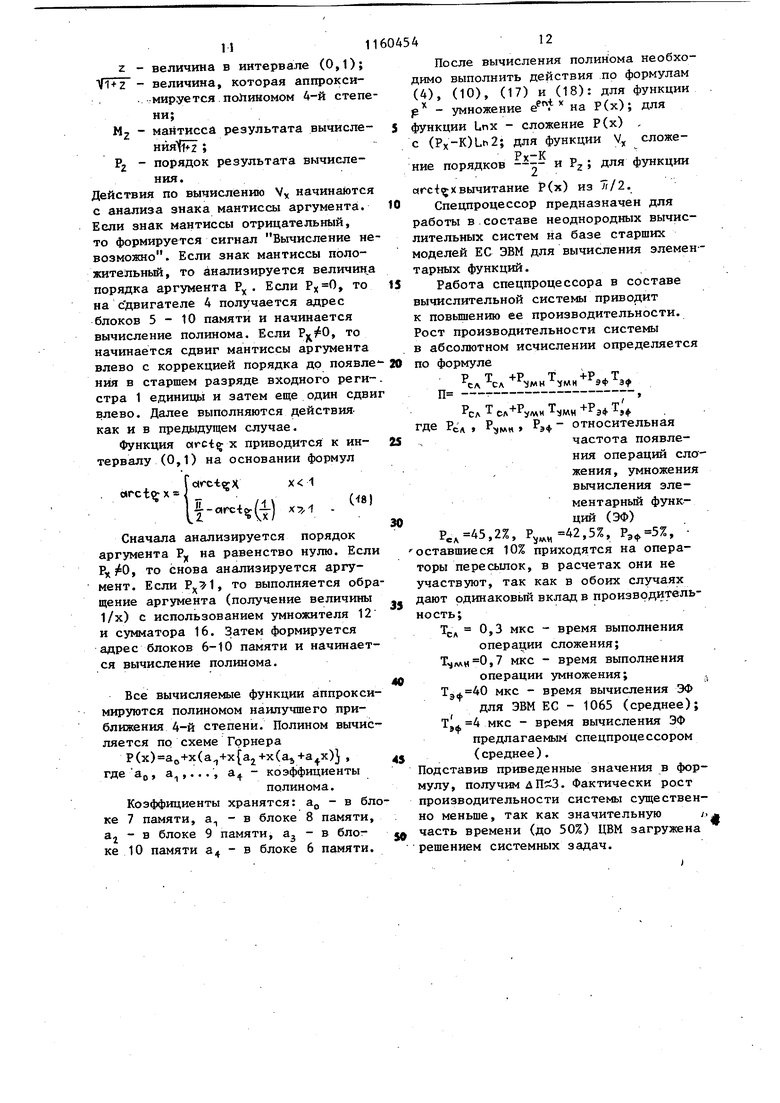

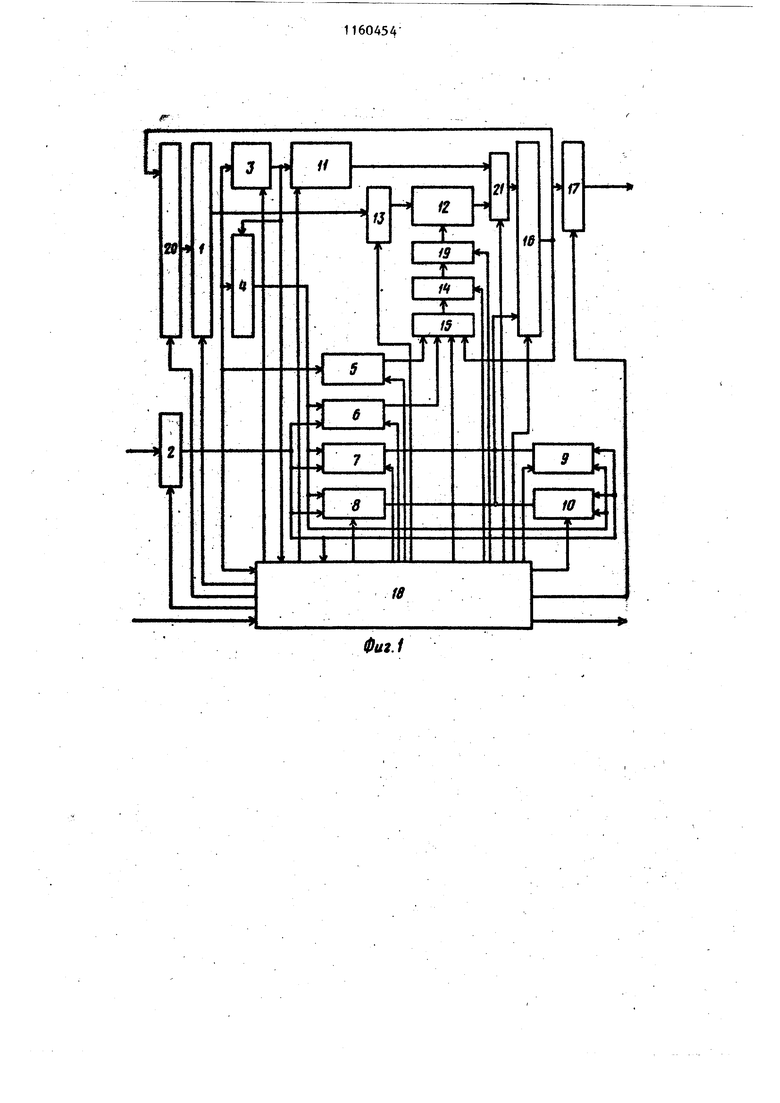

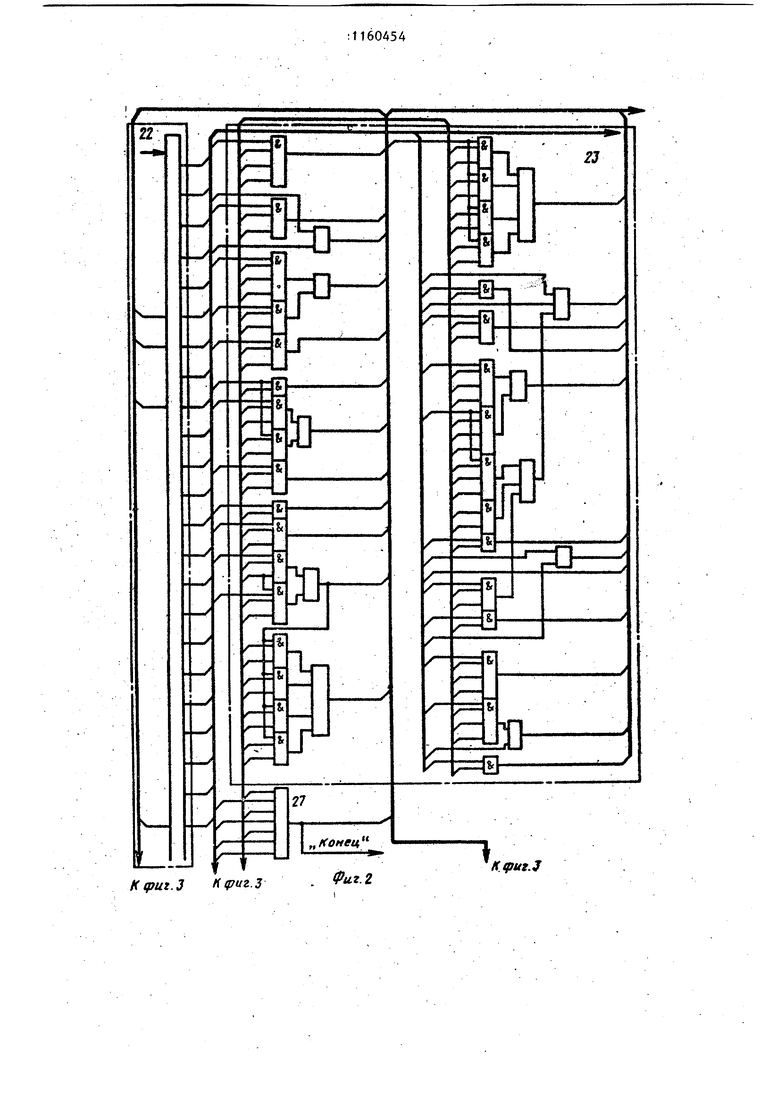

УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ЭЛЕМЕНТАРНЫХ ФУНКЦИЙ, содержащее два коммутатора, входной и выходной регистры, матричный умножитель, . накапливающий сумматор, сдвигатель мантиссы, счетчик порядка, первый блок памяти и блок управления, содержащий сдвиговый регистр, дешифратор циклов, дешифратор признака, распределитель импульсов и элемент ИЛИ, входы которого соединены с выходом разрядов сдвигового регистра и входом распределителя импульсов, выход .которого соединен с входом дешифратора циклов, выходы с первого по третий которого соединены с управляющими входами соответственно накапливающего сумматора, входного регистра и счетчика порядка выход которого соединен с информационным входом сдвигового регистра и управляющим входом сдвигателя мантиссы, информационный вход кото.рого соединен с выходом входного регистра, информационный вход которого соединен с выходом первого коммутатора, первый и второй информационные входы которого соединены соответственно с входом аргумента устройства и выходом накапливающего сумматора, первый информационный вход которого соединен с выходом второго комм5п:атора, первый и второй информационные входа которого соединены с выходами соответственно первого блока памяти и матричного умножителя, выход выходного регистра соединен с входом функции устройства, отличающее ся тем, что, с целью повышения быстродействия, в него введены регистр функции, регистр множимого, регистр множите- пя, мультиплексор сдвигатель множи(Л теля и с второго по седьмой блоки . памяти, причем в блок.управления введен шифратор режима, вход которого соединен с выходом сдвигового регистра, выходы с первого по седьмой шифратора режима соединены с управляющими входами соответственно а с первого по седьмой блоков памяти, выход элемента ШШ соединен с выходом о сигнала конца преобразования устрой4: СЛ 4 ства, вход задания функции которого соединен с информационным входом регистра функции, выход которого соединен с первыми адресными входами с второго по шестой блоков памяти, вторые адресные входы которых соединены с выходом сдвигателя мантиссы, выход входного регистра соединен. с информационными входами счетчика порядка, регистра множимого и сдвигового регистра и .ад ;реснь1м. входом седьмого блока памяти, выход которого соединен с первым информационным входом мультиплексора,второй и тре

Изобретение относится к вычислительной технике и может быть использовано в качестве периферийного процессора высокопроизводительных ЦВМ общего назначения для вычисления основных элементарных функций.

Известен специализированный процессор, содержащий входной регистр, первое множительное устройство, первый сумматор, основную память, регистр функции, счетчик порядка, вспомогательный регистр, дешифраторы сдвигатель, второй сумматор, второе и третье множительные устройства, дополнительную память. Первый выход Сумматора соединен с первым выходом регистра функции, второй вход которого подключен к первому выходу блока управления. Первый вход счетчика порядка соединен с входом процессора, первый выход входного регистра - с первым входом первого множительного устройства, первый выход которого соединен с первым входом первого сумматора. Второй вход процессора соединен с первым входом входного регистра, второй вход которого подключен к второму выходу блока управления. Третий выход блока управления соединен с третьим входом первого сумматора, четвертый и пятый выходы - соответственно с первыми входами основной и дополнительнойпамяти, шестой, седьмой и восьмой

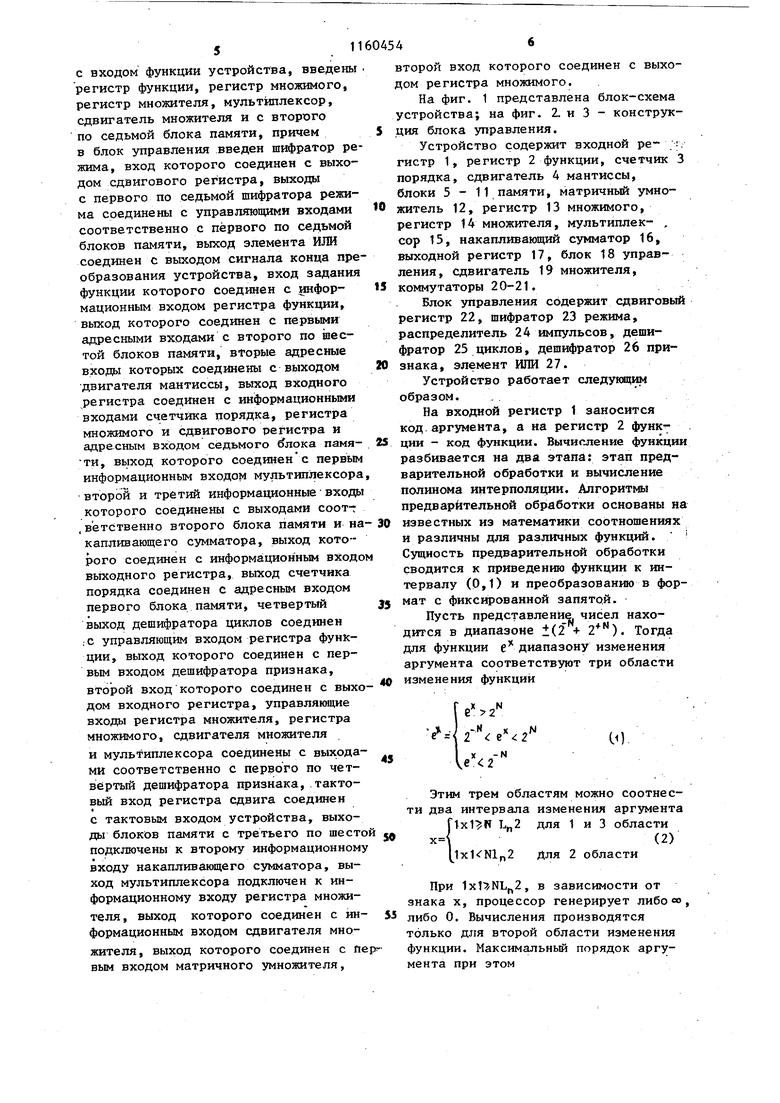

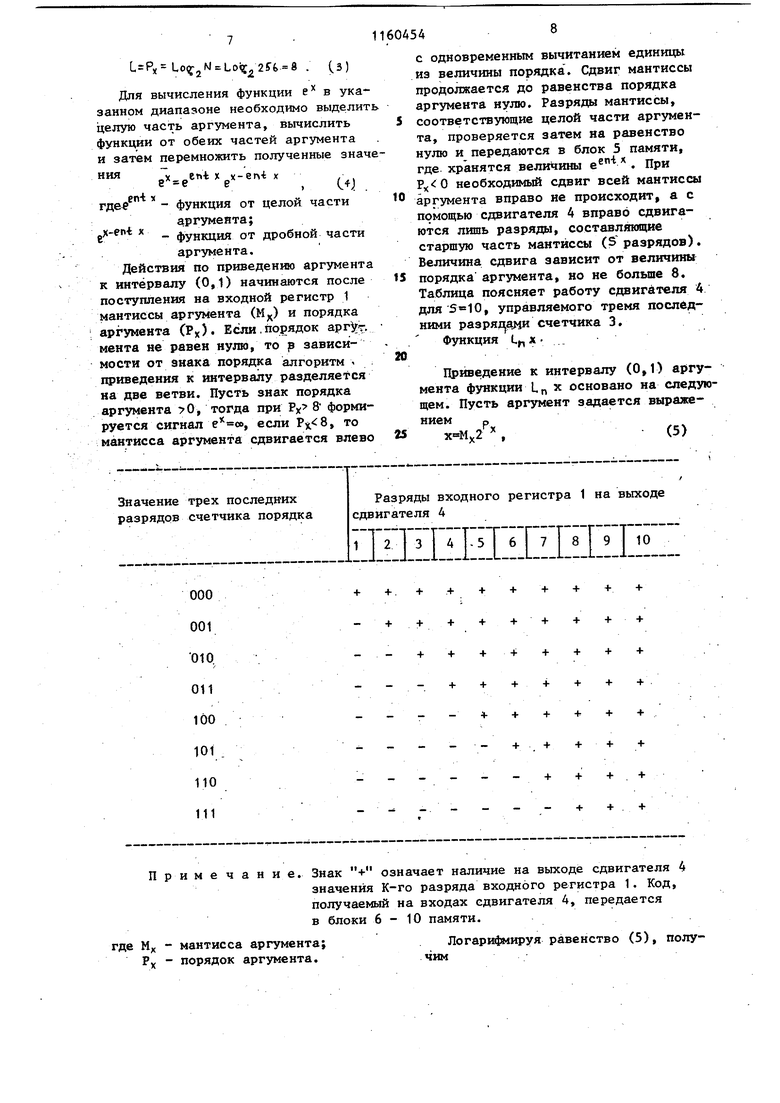

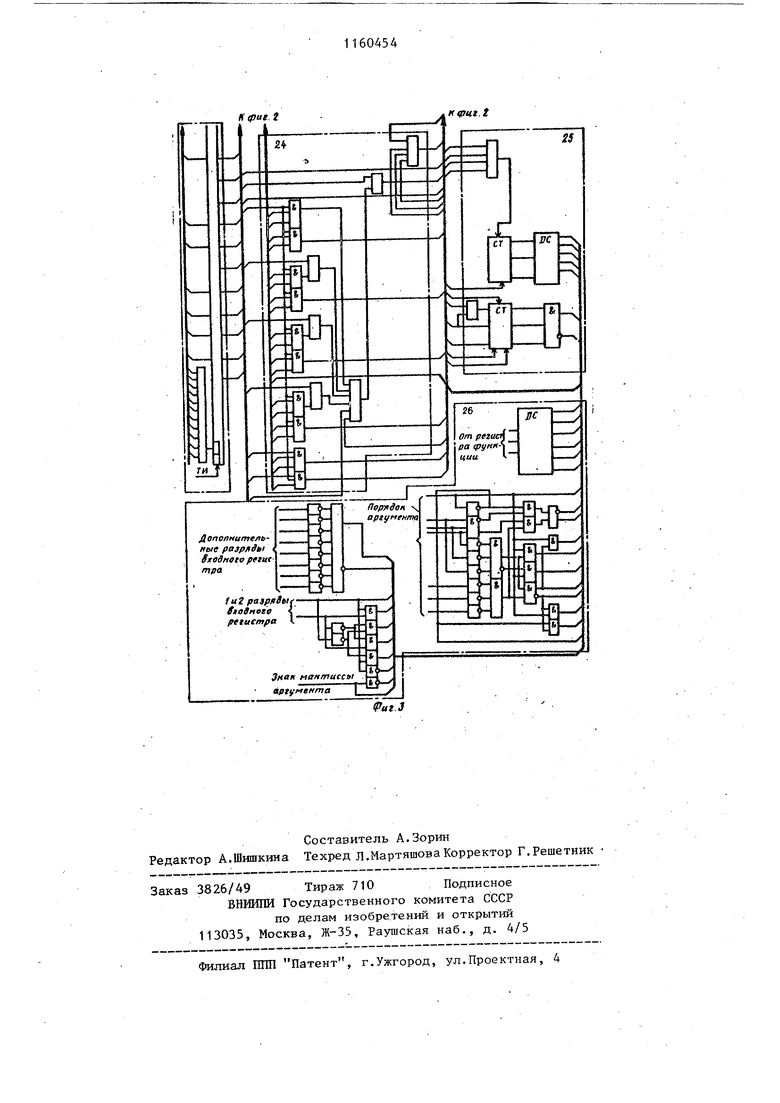

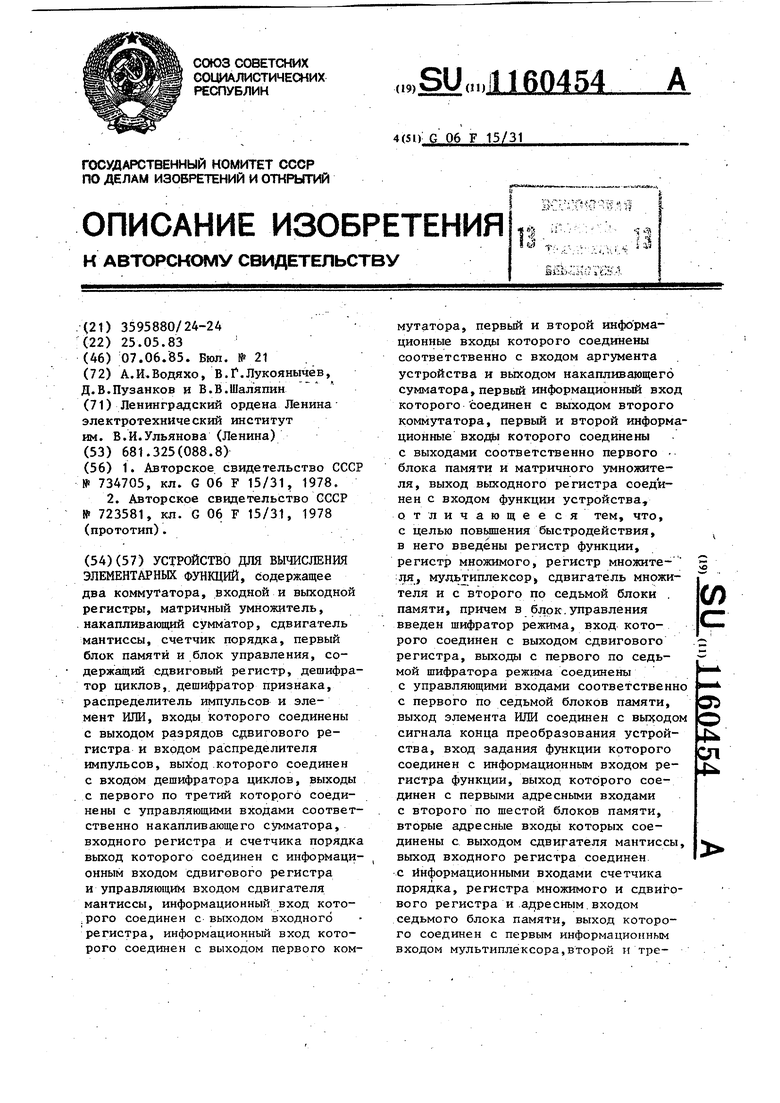

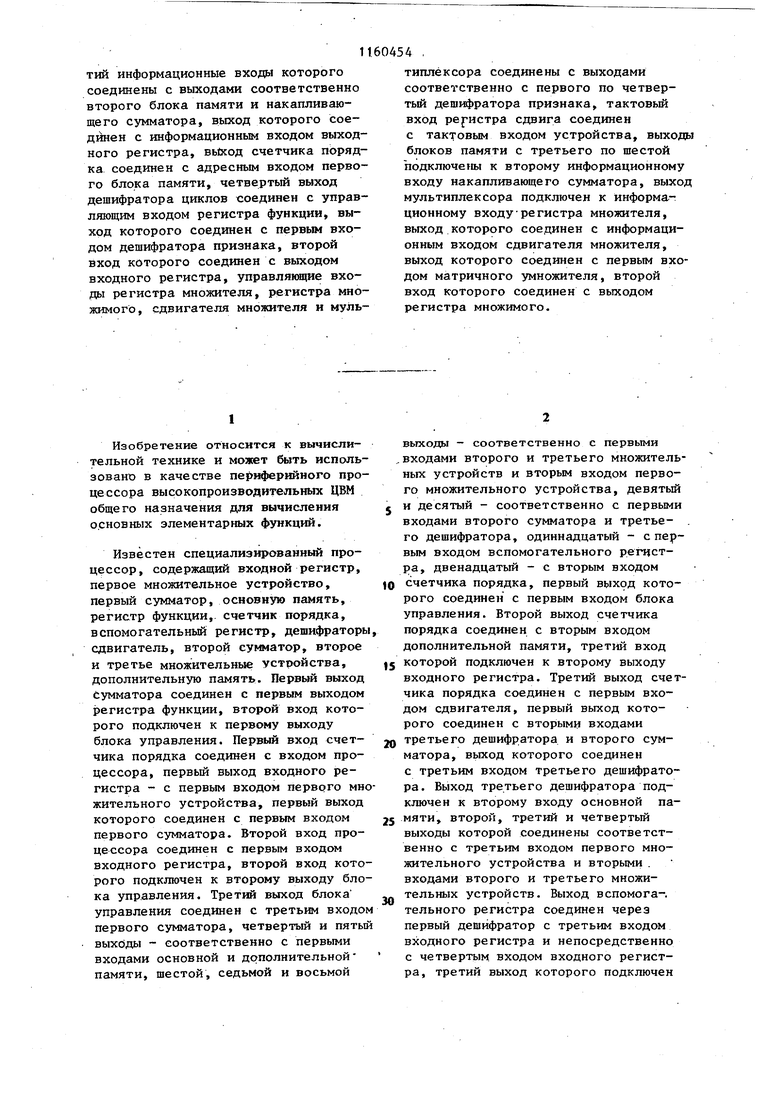

выходы - соответственно с первыми .входами второго и третьего множительных устройств и вторым входом первого множительного устройства, девятый и десятый - соответственно с первыми входами второго сумматора и третьего дешифратора, одиннадцатый - с первым входом вспомогательного регистра, двенадцатый - с вторым входом счетчика порядка, первый выход которого соединен с первым входом блока управления. Второй выход счетчика порядка соединен с вторым входом дополнительной памяти, третий вход которой подключен к второму выходу входного регистра. Третий выход счетчика порядка соединен с первым входом сдвигателя, первый выход которого соединен с вторыми входами третьего дешифратора и второго сумматора, выход которого соединен с третьим входом третьего дешифратора. Выход третьего дешифратора подключен к второму входу основной памяти, второй, третий и четвертый выходы которой соединены соответственно с третьим входом первого множительного устройства и вторыми . входами второго и третьего множительных устройств. Выход вспомога-. тельного регистра соединен через первый дешифратор с третьим входом входного регистра и непосредственно с четвертым входом входного регистра, третий выход которого подключен через второй дешифратор к второму входу блока управления. Четвертый выход входного регистра соединен с вторым входом сдвигателя, второй выход которого подключен к третьим входам второго сумматора и блока управления, а пятый выход входного регистра соединен с вторым входом jвспомогательного регистра. Первый :выход входного регистра соединен с четвертым входом первого сумматора, пятый и шертой входы которого соединены соответственно с выходами .второго и третьего множительных устройств, третьи входы которых соединены соответственно с вторым и третьим выходами первого множительного устройства. Первый и второй выхода дополнительной памяти соедин ны соответственно с четвертым вхо:дом первого множительного устройства и с седьмь1м входом первого сумма тора, второй выход которого подключен к пятому входу первого множител ного устройства, .четвертый выход ко торого соединен с пятым входом вход ного регистра, вход-выход которого подключен к выходу первого сумматор выход регистра функции соединен с выходом процессора . Недостатком данного устройства является его сложность. Наиболее близким к изобретению по технической сущности является специализированный процессор, содер жащий входной регистр, выход которо го соединен с входом блока умножите ля и входом сумматора. Выход суммат ра подключен К-входу регистра функции, выход которого счэединен с входом выходного регистра и входами элементов И группы, выходы которых подключены к входу блока умножения. Выход блока умножения соединен с вх дом сумматора, вход которого подклю чен к выходам элементов И второй группы, входы которых подключены к выходу постоянного запоминающего устройства. Выход блока управления подключен к входу выходного регистра и входам элементов И первой груп пы. Выходы блока управления соедине ны соответственно с входом регистра функции и с входами элементов И вто рой группы. Выход счетчика порядка подключен к входу блока умножения, выход блока умножения соединен с вх дом входного регистра, выход которо подключен к входу сдвигателя, а вход последнего.соединен с входом постоянного запоминающего устройства. Выход входного регистра подключен к входу запоминающего устройства, выход которого Соединен с входом блока умножения. Выход входного регистра подключен к входу блока управления, выход которого соединен с входом счетчика порядка. Выход последнего подключен к входу сдвигателя и входу блока управления, выход сумматора соединен с входом входного регистра. Вход счетчика порядка и вход входного регистра подключены к входам процессора, к выходу которого подключен выход выходного регистра С2Л. Недостатком известного устройства является низкое быстродействие. Цель изобретения - повьшение быстродействия. Поставленная цель достигается тем, что в устройство для вычисления элементарных функций, содержащее два коммутатора, входной и выходной регистры, матричный умножитель, накапливающий сумматор, сдвигатель мантиссы, счетчик порядка, первый блок haмяти и блок управления, содержащий сдвиговый регистр, дешифратор циклов, дешифратор признака, распределитель импульсов и элемент ЮШ, входы которого .соединены с выходом разрядов сдвигового регистра и входом распределителя импульсов, выход которого соединен с входом дешифратора циклов, выходы с первого по третий |соторого соединены с управляющими входами соот-. ветственно накапливающего сумматора, входного регистра и счетчика порядка, выход которого соединен с информационным входом сдвигового регистра и управляющим входом сдвигателя мантиссы, информационный вход которого соединен с выходом входного регистра, информационный вход которого соединен с выходом первого коммутатора, первый и второй информационные входы которого соединены соответственно с входом аргумента устройства и выходом накапливающего сумматора, первый информационный вход которого соединен с выходом второго коммутатора, первый и второй информационные входы которого соединены с выходами соответственно первого блока памяти и матричного умножителя, выход выходного регистра соединен С входом функции устройства, введены регистр функции, регистр множимого, регистр множителя, мультиплексор, сдвигareль множителя и с второго по седьмой блока памяти, причем в блок управления введен шифратор ре жима, вход которого соединен с выходом сдвигового регистра, выходы с первого по седьмой шифратора режима соединены с управляющими входами соответственно с первого по седьмой блоков памяти, выход элемента ИЛИ соединен с выходом сигнала конца пре образования устройства, вход задания функции которого соединен с информационным входом регистра функции, выход которого соединен с первыми адресными входами с второго по inecтой блоков памяти, вторые адресные входы которых соединены с выходом двигателя мантиссы, выход входного регистра соединен с информационными входами счетчика цорядка, регистра множимого и сдвигового регистра и адре сным входом седьмого лока памяти, выход которого соединенс первым информационным входом мультиплексора второй и третий информационныевходы которого соединены с выходами соот-г .ветственно второго блока памяти и на капливающего сумматора, выход которого соединен с информационным вход выходного регистра, выход счетчика порядка соединен с адресным входом первого блока памяти, четвертый выход дешифратора циклов соединен .с управляющим входом регистра функции, выход которого соединен с первым входом дешифратора признака, второй входкоторого соединен с выхо дом входного регистра, управляющие входы регистра множителя, регистра множимого, сдвигателя множителя и мультиплексора соединены с выхода ми соответственно с первого по четв ертый дешифратора признака, тактовый вход регистра сдвига соединен с тактовым входом устройства, выходы блоков памяти с третьего по шест подключены к второму информационном входу накапливающего сумматора, выход мультиплексора подключен к информационному входу регистра множителя, выход которого соединен с информационным входом сдвигателя множителя, выход которого соединен с пе вым входом матричного умножителя, второй вход которого соединен с выходом регистра множимого. На фиг. 1 представлена блок-схема устройства; на фиг. 2, и 3 - конструкция блока управления. Устройство содержит входной ре- :: гистр 1, регистр 2 функции, счетчик 3 порядка, сдвигатель 4 мантиссы, блоки 5 - 11 памяти, матричный умножитель 12, регистр 13 множимого, регистр 14 множителя, мультиплек- , сор 15, накапливающий сумматор 16, выходной регистр 17, блок 18 управления, сдвигатель 19 множителя, коммутаторы 20-21. Блок управления содержит сдвиговый регистр 22, шифратор 23 режима, распределитель 24 импульсов, дешифратор 25 циклов, дешифратор 26 признака, элемент ИЛИ 27. Устройство работает следунид образом. . На входной регистр 1 заносится код.аргумента, а на регистр 2 функ дни - код функции. Вычисление функции разбивается на два этапа: этап предварительной обработки и вычисление полинома интерполяции. Алгоритмы предварительной обработки основаны на известных из математики соотношениях и различны для различных функций. Сущность предварительной обработки сводится к приведению функции к интервалу (0,1) и преобразованию в формат с фиксированной запятой. Пусть представление чисел находится в диапазоне 1(2 + 2). Тогда для функции е диапазону изменения аргумента соответствуют три области изменения функции eS2 е гЭтим трем областям можно соотнести два интервала изменения аргумента 11х1Я для 1 и 3 области (2) 1xKN1 2 Для 2 области При , в зависимости от знака X, процессор генерирует либо, либо 0. Вычисления производятся только для второй области изменения функции. Максимальный порядок аргумента при этом L Lo9:, 8 . (з) Для вычисления функции е в указанном диапазоне необходимо выделит целую часть аргумента, вычислить функции от обеих частей аргумента и затем перемножить полученные знач е XgX-er X п4. гдее - функция от целой части аргумента; - функция от дробной части аргумента. Действия по приведению аргумента к интервалу (0,1) начинаются после поступления на входной регистр 1 мантиссы аргумента (М) и порядка аргумента (РХ). Если.порядок . мента не равен нулю, то р зависимости от знака порядка алгоритм . приведения к интервалу разделяется на две ветви. Пусть знак порядка аргумента 0, тогда при РХ 8 формируется сигнал , если P), то мантисса аргумента сдвигается влево

Значение трех последних разрядов счетчика порядка

000

001

011

100

101

110

111 Примечание.

где М - мантисса аргумента; РХ - порядок аргумента.

Разряды входного регистра 1 на выходе сдвигателя 4

1 1 2 3 I 4 Т-зТ 6 Г 7 8 Г 9 I 10

+ . +

+ + + + + + + - + + + + +

Логарифмируя равенство (5), получимЗнак + означает наличие на выходе сдвигателя 4 значения К-го разряда входного регистра 1. Код, получаемый на входах сдвигателя 4, передается в блоки 6 - 10 памяти. с одновременным вычитанием единицы из величины порядка. Сдвиг мантиссы продолжается до равенства порядка аргумента нулю. Разряды мантиссы, соответствующие целой части аргумента, проверяется затем на равенство нулю и передаются в блок 5 памяти, где хранятся величины е . При необходимый сдвиг всей мантиссы аргумента вправо не происходит, а. с помощью сдвигателя 4 вправо сдвигаются лишь разряды, составляющие старшую часть мантиссы (S разрядов). Величина сдвига зависит от величины порядка аргумента, но не больше 8. Таблица поясняет работу сдвигателя 4 для , управляемого тремя последними разрядами счетчика 3. Функция L,, X . Приведение к интервалу (0,1) аргумента функции L п основано на следующем. Пусть аргумент задается выражением р .2 (5) L« PX Ln2 . Ifrteer место равенство LnM rLnll z) где i: MJf-1, MX - мартисса сдвинутая таким образом, что может быть представлена кодом } -м ) t-i j- ; +t где 2. - двоичная цифра числа. Сдвиг выполняется до первой ситуа НИИ, при которой перед запятой устанавливается единица, т.е. можно запим; м 2 где К - число сдвигов до получения кода (8). Таким образом Ln (м; 2) ( l,n/M -KLn2+ PxLn2 l,n(1njt(Pjj-K)U2, (10) где () - код, содержащийся на счетчике 3 порядка. Действия по вычисленпо функции начитаются с анализа знака мантиссы При отрицательном аргументе фо1)ируется сигнал вычисление невозможно Бели знак мантиссы положительн, то аргумент сдвигается влево До появления в старшем разряде входного регистра 1 единицы. Порядок аргумента изменяется пропорционально количеству сдвигов. Затем, для получения дробной чисти величины Ln(1+2) содержимое входного регистра сдвигается еще раз влево. Величина () передаетс в блок 11 памяти, где хранится произведение (Pjj-K)Lrv2. Функция X. . Сведение аргумента функции sVn х к интервалу (0,1) основано на Соотношении . , 3inx siM(2JiK+) Sln/ , (И) где К - целое число; V - переменная в интервале 0,, () Обозначим 2L -4r-eniier 2li 2л где . Два сташих разряда величины Z указывают номер квадранта, в котором находится угол Ч. Представим величину Stn Ч как 3inV sin27r2 5invV где 1. Вычисление sitiy-V в зависимости от арг s. етс cos квадранта, в котором находится умент, выполняется по формулам S,-nfv для 1 квадранта -sin.(i-v) для П квадранта fv для Ш квадранта 5in|-(l-V) для 1У квадранта Переход к функции cos х осуществля я по формуле cos xesi«fx-f | . (15) В этом случае формулы вычисления 1-V имеют ВИД -sin|-(l-v) .для 1 квадранта - sin-|-V для П квадранта cos V tt . Ып -я- (.1-V) для Ш квадранта для 1У квадранта Приведение к интервалу (0,1) начинается с умножения мантиссы аргумента MX на 1/2W в уютожителе 12. Полученное произведе1|ие записывается во входной регистр 1. Если порядок произРХ О и РХ 0, то, одвигая влег х х во содержимое входного регистра 1, добиваются равенства порядка нулю (т.е. получаем переменную г)., В зависимости от номера квадранта и вида функции (sir X или cos х) из единицы вычитается М, находящееся в входном регистре 1 (формулы 14 и 16). Для перехода от переменной z кпеременной V , М;( cдви aeтcя влево на два разряда. Приведение функции V к интервалу (0,1) основано на соотношении , м;,2 2 где К - число сдвигов мантиссы исходного аргумента до первой ситуации, при которой перед запятой устанавливается единица;11 z - величина в интервале (0,1); тРнТ величина, которая аппроксимируется полиномом 4-й степ ни; мантисса результата вычисле ; порядок результата вычисления. Действия по вычислению Vy начинаютс с анализа знака мантиссы аргумента. Если знак мантиссы отрицательный, то формируется сигнал Вычисление не возможно. Если знак мантиссы положительный, то анализируется величин. порядка аргумента Р. Если , то на сдвигателе 4 получается адрес блоков 5-10 памяти и начинается вычисление полинома. Если , то начинается сдвиг мантиссы аргумента влево с коррекцией порядка до появле ния в старшем разряде входного регистра 1 единицы и затем еще один сдв влево. Далее выполняются действиякак и в предыдущем случае. Функция arct X приводится к ин тервалу (0,1) на основании формул jdrc-t X oirct X и-о-чШ Сначала анализируется порядок аргумента Pj, на равенство нулю. Если Р, , то снова анализируется аргумент. Если , то выполняется обр щение аргумента (получение величины 1/х) с использованием умножителя 12 и сумматора 16. Затем формируется адрес блоков 6-10 памяти и начинается вычисление полинома. Все вычисляемые функции аппрокси мируются полиномом наилучшего приближения 4-й степени. Полином вычис ляется по схеме Гррнера P(x)ao+x(a +x{aj+x()J , где ар, а,..., а - коэффициенты полинома. Коэффициенты хранятся: а, ке 7 памяти, а - в блоке 8 памяти, aj - в блоке 9 памяти, а - в блоке 10 памяти а в блоке 6 памяти. 4 После вычисления полинома необходимо выполнить действия по формулам (4), (10), (17) и (18): для функции - умножение е на Р(х); для функции Lnx - сложение Р(х) . с (Px-K) для функции V, сложеРх-Ки 2 , ДЛЯ функции ние порядков --«ГС-t xвычитание Р(х) из л/2. Спецпроцессор предназначен для работы в составе неоднородных вычислительных систем на базе старших моделей ЕС ЭВМ для вычисления элементарных функций. Работа спецпроцессора в составе вычислительной системы приводит к повьшению ее производительности. Рост производительности системы в абсолютном исчислении определяется по формуле р т +р т +р т мн ЭФ э р -г +р т +Р , т Сл С-и ylл -умм Э эф относительная СА я1л« частота появления операций сложения, умножения вычисления элементарный функций (ЭФ) 45,2%, Р,,,57„, ,, 10% приходятся на операоставшиесяторы пересылок, в расчетах они не участвуют, так как в обоих случаях дают одинаковый вклад в производительность;Тед 0,3 МКС - время выполнения операции сложения; Ту),7 МКС - время выполнения операции умножения; , МКС время вычисления ЭФ для ЭВМ ЕС - 1065 (среднее); МКС - время вычисления ЭФ предлагаемым спецпроцессором (среднее). Подставив приведенные значения в форулу, получим д Пс13. Фактически рост производительности системы существенно меньше, так как значительную л, часть времени (до 50%) ЦВМ загружена решением системных задач. . )

Фиг.1

31

г

23

Р

, Koнe

Фиг.г

Kipuz.S К1риг.З

K.ipuz.J

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Специализированный процессор | 1977 |

|

SU734705A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Специализированный процессор | 1977 |

|

SU723581A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-06-07—Публикация

1983-05-25—Подача