(54) УСТРОЙСТВО ДЛЯ ПРЕОБРАЗОВАНИЯ ПОЛЯРНЫХ КООРДИНАТ ВЕКТОРА В ПРЯМОУГОЛЬНЫЕ

1

Изобретение относится к области вычислительной техники и может быть использовано в составе вычислителей при решении задач, связанных с преобразованием координат.

Известно устройство для преобразования полярных координат в прямоугольные, содержащее блок формирования стробов, элементы И, блок умножения, блок памяти, потенциальными входами соединенный с шинами старших разрядов входного кода, коммутатор и переключатель квадрантов

IJ.

К недостатком такого устройства

следует отнести его сложность и недостаточно широкий диапазон изменения входной частоты.

Наиболее близким по технической сущности является устройство для преобразования полярных координат в прямоугольные, которое содержит коммутатор, первый и второй выходы которого соединены со входами делителей частоты, потенциальные входы которых подключены к знаковьм выходам переключателя квадрантов, ваход переключателя квадрантов соединен со входом коммутатора, потенциальным входом подключенного к управляющему выходу схемы формирования стробов, а импульсным - к выходу схемы ИЛИ

Недостатками устройства являются сложность обслуживания заданием ординат функции sines, в частотно-импульсной форме, что требует определенных аппаратурных затрат, а также узкий диапазон изменения .

10 входной частоты, что вызвано формированием значений sine и coscs за два последовательных такта.

Целью изобретения является расширение диапазона входных сигналов.

15

Цель достигается тем, что устройство для преобразования полярных координат вектора в прямоугольные, содержащее блок Памяти и коммутатор, первые ВХО.ЦЫ которых подключены к

20 выходу триггера интервгшов, первый вход которого соединен с импульсным входом устройства, первый и второй делители частоты, импульсные входы которых соединены с соответствуюсдими

25 выходами ко1имутатора, а управляющие входы - соответственно с первым и втopЬl выходами квадрантного переключателя, подключенного входом к шине кода квадранта, третий выход

30 квадрантного перек.шочателя соединен

с вторым входом коммутатора, содержит блок число-импульсного умножения, блок сравнения, счетчик элемент И, триггер запуска, выход которого подключен к первому входу элемента И, второй вход которого подключен к шине опорной частоты, а выход к импульсному входу блока число-импульсного умножения, потенциальный вход которого соединен с выходе блока памяти, потенциальный выход - с младшими разрядами первой группы входов блока сравнения, первый и второй импульсные выходы - соответственно с импульсным входом коммутатора и с входом счетчика, потенциальный выход которого связан с вторым входом блока памяти и со старшими разрядами первой группы входов блока сравнения, а импульсный вйход - с первым входом триггера запуска, второй вход которого соединен с импульсным входом устройства, вторая группа входов блока сравнения подключена к шине задания аргумента вектора, выход блок-а сравнения соединен с вторым входом триггера интервалов.

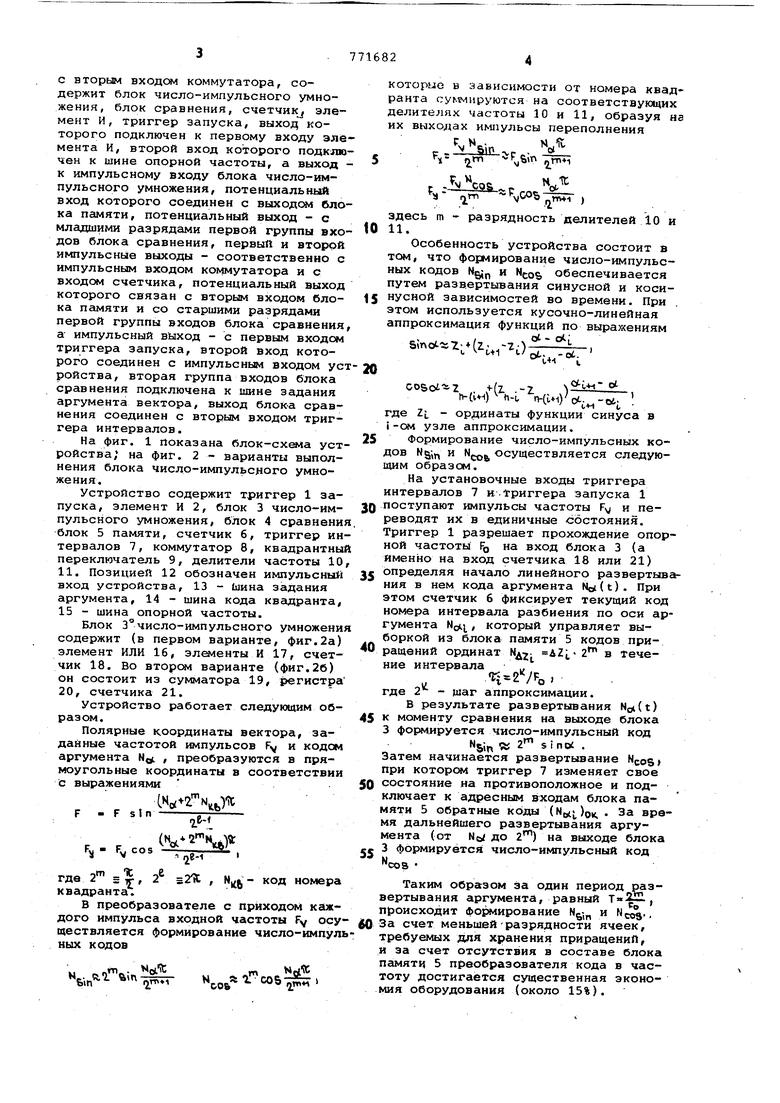

На фиг. 1 показана блок-схема устройства; на фиг. 2 - варианты выполнения блока число-импульсного умножения.

Устройство содержит триггер 1 запуска, элемент И 2, блок 3 число-импульсного умножения, блок 4 сравнения блок 5 памяти, счетчик 6, триггер интервалов 7, коммутатор 8, квадрантный переключатель 9, делители частоты 10 11. Позицией 12 обозначен импульсный вход устройства, 13 - Шина задания аргумента, 14 - шина кода квадранта, 15 - шина опорной частоты.

Блок 3°число-импульсного умножени содержит (в первом варианте, фиг.2а) элемент ИЛИ 16, элементы И 17, счетчик 18. Во втором варианте (фиг.2б) он состоит из сумматора 19, регистра 20, счетчика 21.

Устройство работает следующим образом.

Полярные координаты вектора, заданные частотой импульсов Fy и кодсм аргумента N , преобразуются в прямоугольные координаты в соответствии с выражениями

(,)4c

F . F sin

()

F - F cos

где 2 s, 2 2lC , - код номера квадранта.

В преобразователе с приходом ксШдого импульса входной частоты Fy осуществляется формирование число-импулных кодов

N(iK

ы,,.;п

,чП

KOTOpuo в аависимости от номера квадранта суммируются на соответствующих делителях частоты 10 и 11, образуя нз их выходах импульсы переполнения

N. N.

ot vjSin

. -bile

а (т . , ,

здесь m - разрядность делителей 10 и

0 11.

Особенность устройства состоит в том, что формирование число-импульсных кодов и NCOS обеспечивается путем развертывания синусной и косинусной зависимостей во времени. При этом используется кусочно-линейная аппроксимация функций по выражениям

ot- сЛ

SinoC Z-Ч аГ С)

Qt

2 -t-fz. -г

cosoi VUH) h-L )

где Zj, - ординаты функции синуса в i-см узле аппроксимации.

5 Формирование число-импульсных кодов , и осуществляется следующим образом.

На установочные входы триггера интервалов 7 и.триггера запуска 1

Q поступают импульсы частоты F и переводят их в единичные состояния. Триггер 1 разрешает прохождение опорной частоты FO на вход блока 3 (а именно на вход счетчика 18 или 21)

- определяя начало линейного развертывания в нем кода аргумента Nai(t). При этом счетчик 6 фиксирует текущий код номера интервала разбиения по оси аргумента NOH , который управляет выборкой из блока памяти 5 кодов приращений ординат Т в течение интервала ..

, .

где 2 - шаг аппроксимации.

В результате развертывания No((t)

5 х моменту сравнения на выходе блока 3 формируется число-импульсный код

Ngin W 2 sinU .

Затем начинается развертывание при котором триггер 7 изменяет свое

0 состояние на противоположное и подключает к адресным входам блока памяти 5 обратные коды (Nj )оц . За время дальнейшего развертывания аргумента (от NO/ до 2) на выходе блока

3 формируется число-импульсный код

cos

Таким образом за один период развертывания аргумента, равный , происходит фо Ж1ирование ,„ и N., За счет меньшей-разрядности ячеек, требуемых для хранения приращений, и за счет отсутствия в составе блока памяти 5 преобразователя кода в частоту достигается существенная экономия оборудования (около 15%).

Сокращение времени вычисления Н и Ncoft до одного такта развертывания Noi(t) от О до 2 (в прототипе требуется дважды развертьюать N(t) от О до 2) позволило в два раза расtimpHTb диапазон изменения входной частоты.

Формула изобретения

Устройство для преобразования полярных координат вектора в прямоуголные, содержащее блок памяти и коммутатор, первые входы которых подклйчены к выходу триггера интервалов, первый вход которого соединен с импульсным входом устройства, первый и второй делители частоты, импульсные входы которых соединены с соответствующими выходс1ми коммутатора, а управляющие входы - соответственно с первым и вторьм выходами квадрантног переключателя, подключенного входсм шине кода квсщранта,третий выход Квадрантного переключателя соединен вторым входом коммутатора,о т л и чающееся тем,что,с целью рас ширения диапазона входных сигнгшов, устройство содержит блок число-импульсного умножения, блок сравнения, счетчик, элемент И, и триггер запуска, выход которого подключен к первому входу элемента И, второй вход которого подключен к шине опорной частоты, а выход - к импульсному входу блока число-импульсного умножения, потенциальный вход которого соецинен с выходом блока памяти, потенциальный выход - с младшими разрядами первой группы входов блока сравнения, первый и второй импульсные выходы - соответственно с импульсным входом коммутатора и с входом счетчика, потенциальный выход которого связан с вторым входом блока памяти и со cTaixiDfMH разрядами первой группы входов блока сравнения, а импульсный выход - с первым входом триггеS pa запуска, второй вход которого соединен с импульсным входом устройства, вторая группа входов блока сравнения подключена к шине задания аргумента вектора, выход блока Сравнения соединен с вторым ВХОДСИ4 триггера интервалов.

Источники информации, принятые во внимание при экспертизе 1 Авторское свидетельство СССР 463986, кл-.С Об G 7/22, 197.

2. Авторское свидетельство СССР 596955, кл. G Об G 7/02, 1976 (прототип) .

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой преобразователь координат | 1980 |

|

SU942004A1 |

| Преобразователь полярных координат вектора в прямоугольные | 1976 |

|

SU596955A1 |

| Преобразователь полярных координат вектора в прямоугольные | 1974 |

|

SU463986A1 |

| Цифровой преобразователь координат | 1981 |

|

SU960834A1 |

| Цифровое устройство для формирования круговых разверток | 1978 |

|

SU746541A1 |

| Цифровой функциональный преобразователь | 1980 |

|

SU942034A1 |

| Устройство для определения модуля и аргумента вектора | 1981 |

|

SU972523A1 |

| Устройство для определения полярных координат осредненного вектора ветра | 1980 |

|

SU993282A1 |

| Устройство для поворота изображе-Ния СиМВОлОВ | 1979 |

|

SU841030A1 |

| Генератор сигналов сложной формы | 1980 |

|

SU983692A1 |

Т

fl NKt

.1

Авторы

Даты

1980-10-15—Публикация

1978-06-23—Подача