I

Изобретение относится к измерительной и вычислительной технике и может быть использовано в преобразователях напряжение-код при повышенных требованиях по быстродействию и точности.

Известны преобразователи напряжение-код (пик) поразрядного кодирования, выполненные на регистрах и логических элементах, осуществляющие параллельную и последователь 1ую коррекцию динамической ошибки ijj.

В таких ППК в общем случае в каждом разряде допускается внесение динамических погрешностей, меньших принятой дискретности преобразования, так как эти погрешности без ослабления входят в обш.ую погрешность преобразования. Поэтому длительность тактов таких ПИК поразрядного кодирования выбирается равной наибольшей длител1 ности, обеспечивающей допустимую ( меньшую дискретности динамическую погрешность преобразования.

ЧТО приводит к недостаточному быстродействию ПИК при небольшой точности преобразования.

Наиболее близким к изобретению по технической сущности и достигаемому результату является преобразователь напряжение-код с коррекцией динамической погрешности, содержащий регистры кода положительного и отрицательного числа, логические элементы,

10 сумматор, нуль-орган и биполярный преобразователь код-напряжение f 2 .

В этом устройстве быстродействие и точность преобразования находятся в противоречии, так как для обес15печения более точной коррекции требуется увеличение длительности такта.

Цель изобретения - повышени быстродействия и точности преобразования.

20

Цель достигается тем, что в преобразователе напряжение-код с коррекцией динамической погрешности, содержащем нуль-орган, эталонные источНИКИ -напряжений положительной и отрицательной полярностей, регистр кода положительного числа, регистр кода отрицательного числа, распределитель тактовых импульсов, логические элементы и биполярный преобразователь код-налряжение на резистивной матрице, имеющей для каждого разряда два входа, каждый из которых через соответствующий ключ соединен с эталонными источниками напряжения положительной и отрицательной полярности, один вход триггера каждого разряда регистра кода положительного числа соединен через элемент совпадения с выходом инвертора, вход которого подключен к выходу нуль-органа, и с шиной сигнала первого полутакта соответствующего разряда распределителя, тактовых импульсов, другой вход триггера каждого разряда кода положительного числа соединен через элемент совпаде шя с шиной сигнала второго полутакта соответствующего разряда распределителя тактовых импульсов и выходом нуль-органа, один вход триггера каждого разряда регистра кода отрицательного числа соединен через элемент совпадения с выходом нуль-органа и шиной сигнала первого полутакта соответствующего разряда распределителя тактовых импульсов, другой вход триггера каждого разряда регистра кода отрицательного числа подключен через элемент совпадения к выходу инвертора и шине сигнала второго полутакта соответствующего разряда распределителя тактовых HMnynbcoSj выход триггера каждого разряда регистра кода положительного числа соединен со входом управления первого ключа соответствующего разряда, а выход триггера каждого разряда регистра кода отрицательного числа соединен со входом управления второго ключ

соответствующего разряда преобразователя код-напряжение, при этом кодовые шины регистров кода положительного и отрицательного чисел, подключены к соответствующим входам сумматора.

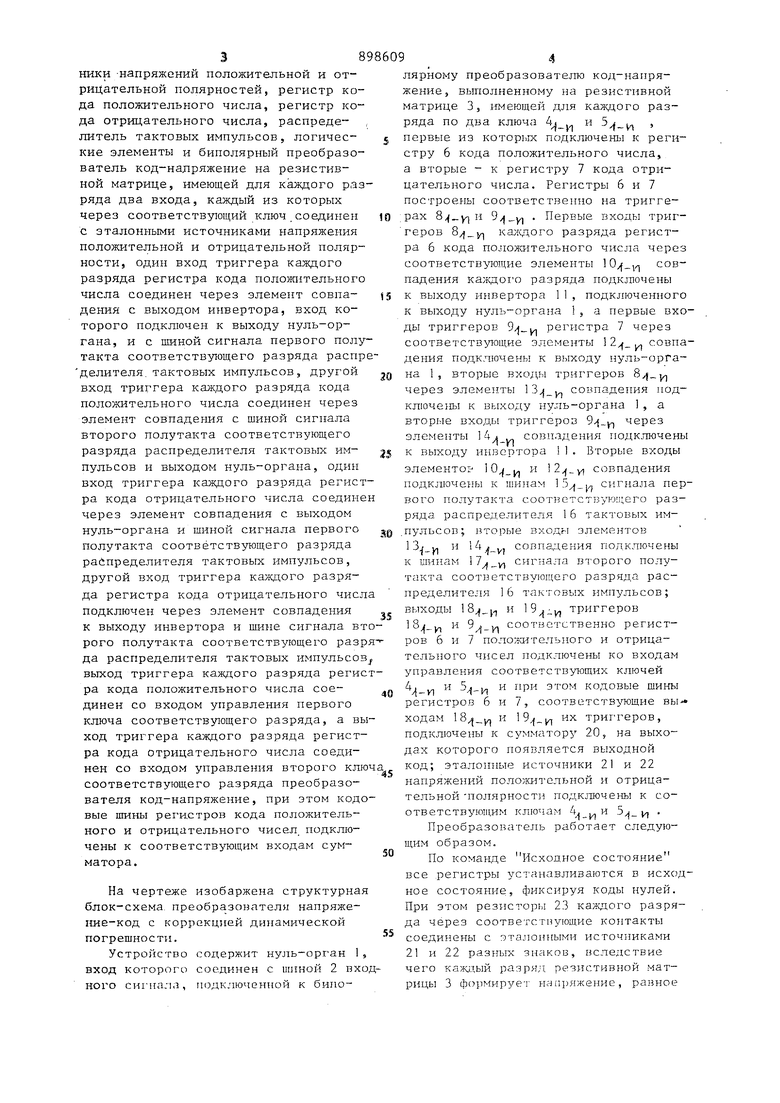

На чертеже изобаржена структурная блок-схема, преобразователя напряжение-код с коррекцией динамической погрешности.

Устройство содержит нуль-орган 1 , вход которого соединен с шиной 2 входного сигнала, гиздключенпой к биполярному преобразователю код-напряжение, выполненному на резистивной матрице 3, ш- еющей для каждого разряда по два ключа 4 и 5, , первые из которьгх подключешз к регистру 6 кода положительного числа, а вторые - к регистру 7 кода отрицательного числа. Регистры 6 и 7 построены соответственно на триггерах и , . Первые входы триггеров ка;{сдого разряда регистра 6 кода пололштельного числа через соответствт,пощие элементы 10, совпадения ка}кдо1о разряда подключены к выходу инвертора 11, подключенного к выходу нуль-органа 1, а первые входы триггеров , pen-iCTpa 7 через соответствующие элементы 12 совпадения подключены к В 1ходу нуль-органа 1, вторые входы триггеров через элементы совпадения подключены к выходу нуль-органа 1 , а вторые входы триггеров 9/( через элементы совпадения подключены к выходу нгпзертора 1 1 . Вторые входы элементор 10 и совпадения подключе Ш к ши}1ам сигнала первого полутакта соотвстствукщего разряда распределителя 16 тактовых им.пульсов; вторые входы элементов 1 , и 14 i ,, совпа,цения подключены к шинам , сигнала второго полутакта соответствующего разряда распределителя 16 тактовых импульсов; выходы 18 и ,у, триггеров

18 и 9

7 , соответственно регистров 6 и 7 пололштельпого и отрицательного чисел подключены ко входам управления соответствующих ключей 4, и 5 и при этом кодовые шины регистров 6 и 7, соответствз.тощие вы ходам и их тригтеров, подключены к сумматору 20, на выходах которого появляется выходной код; эталонные источники 21 и 22 напряжений поло/кительной и отрицательной -полярности подключены к соответствующим ключам 4( и 5 /, .

Преобразователь работает следующим образом.

По команде Исходное состояние все регистры устанавливаются в исходное состояние, фиксируя коды нулей. При этом резисторы 23 каждого разряда через соответствующие контакты соединены с эталонными источниками 21 и 22 разных знаков, вследствие чего каждый разря; резистивной матрицы 3 формирует напряжение, равное нулю. По команде Пуск начинается преобразование входного снгнала. Если на вход ПНК подано отрицательное напряжение, то нуль-орган 1 подает на элементы совпадеш-1я, связанные с входами включе1шя триггеров 9, разрядов регистра 7 кода отрицательного числа, сигнал разрешения на прохоясдение сигналов с шин 15 сигналов первых полутактов разрядов распределителя 16 тактовых импульсов. При этом в первом полутакте первого такта включается триггер 9j первого разряда регистра 7 кода отрицательного числа, который своим сигналом соединяет соответствующий резистор 23 первого разряда с эталонным источником 21 напряжения положительной полярности вследствие чего оба резистор 23 первого разряд матрицы 3 оказываются подключен1-1ыми в параллель к эталонному источнику 2 и формируют компенсирующее положительное напряжение, равное текущему значению веса старшего разряда, которое изменяется из-за переходных процессов, вызванных включением разрядов. К началу второго полутакта первого такта нуль-орган может находиться в двух состояниях: либо его состояние сохраняется, либо знак сиг нала на его выходе изменяется на обратный. В первом случае сигнал второ го полутакта первого такта не проходит на вход сброса триггера 9 перво го разряда регистра 7 кода отрицател ного числа в исходное состояние, так как он должен проходить через элемент 14i совпадения, один из входов которого подключен к выходу инве тора 1, соединенного своим входом с выходом нуль-органа 1, а сигнал на выходе инвертора 11 в этом случае имеет значение нуль. Сигнал второго полутакта проходит на вход сброса в исходное состояние триггера 8. пер вого разряда регистра 6 кода положительного числа, так как элемент 13 совпадения, соединенный с этим входом подключен к выходу нуль-органа Г имеющего состояние 1, но это не изменяет состояние триггера 8 . В этом случае триггер 9 первого разряда регистра 7 кода отрицательного числа зафиксирует код 1, а триггер 8 первого разряда регистра 6 кода положительного числа сохраняет-свое исходное состояние и фиксирует код О. Если к началу второго полутакта состояние нуль-органа 1 изменяется по сравнению с его состоянием в первом полутакте, то инвертор 11, подключеш-аш к выходу нуль-органа 1 , формирует сигнал, разрешающий прохождение сигналов вторых полутактов на входы сброса в исходное состояние триггеров , разрядов регистра 7 кода отрицательного числа. Тогда сигнал второго полутакта первого так та зстанавливает триггер 9, первого разряда регистра 7 кода отрицательного числа в исходное состояние, а триггер 8 первого разряда регистра б кода положительного числа сохраняет свое исходное состояние. В этом случае первые разряды регистров кодов отрицательного и пoлoжIiтeльнoгo чисел фиксируют коды О. В последующих тактах ПНК работает аналогичным образом: в начале первого полутакта каждого такта включается триггер 9j соответствующего разряда регистра 7 кода отрицательного числа, если нульорган 1 находится в состоянии 1, или регистра б кода положительного числа, естш инвертор П, соединенный с выходом нуль-органа 1,, имеет состояние при включении триггера соответствующего разряда регистра 7 кода отрицательного числа формируется положительное опорное напряжение данного разряда, а при включении триггера 8 , регистра 6 кода положительного числа форшфуется отрицательное опорное напряжение данного разряда , В результате преобразования формируется п-разрядный код отрицательного числа и п-разрядный код положительного числа, поступающие на сумматор 20. Моделирование процесса преобразования данного ПНК показывает, что при использовании одних и тех же элементов дан1-1ьш ПНК позволяет увеличить скорость преобразования в несколько раз без ухудшения точности преобразования. Формула изобретения Преобразователь напряжение-код с коррекцией .тщнамической погрешности, содержащий нуль-орган, эталонные источники напряжений положительной 7 и отрицательной полярности, регистр кода положительного числа, регистр кода отрицательного числа, распределитель тактовых импульсов, логические элементы и биполярный преобразователь код-напряжение на резистивной матрице, имеющей для каждого разряда два входа, каждый из которых через соответствующий ключ соединен с эталонными источниками напряжения положительной и отрицательной полярности otлич, ающийся тем, что, с целью повышения быстродействия и точности преобразования в нем, один вход триггера каждого разряда регист ра кода положительного числа соединен через элемент совпадения с выходом инвертора, вход которого подключен к выходу нуль-органа, и с шиной сигнала первого полутакта соответствующего разряда распределителя такто вых импульсов, другой вход триггера каждого разряда кода положительного числа соединен через элемент совпаде ния с шиной сигнала второго полутакта соответствующего разряда распреде лителя тактовых импульсов и выходом нуль-органа, один вход триггера кажд го разряда регистра кода отрицательн го числа соединен через элемент совпадения с выходом нуль-органа и ши09ной сигнала первого полутакта соответ- ству}ощего разряда распределителя тактовых импульсов, другой вход триггера каждого разряда регистра кода отррщательного числа подключен через элемент совпадения к выходу инвертора и шине сигнала второго полутакта соответствующего разряда распределителя тактовых импульсов, выход триггера каждого разряда регистра кода положительного числа соединен со входом управле1дая первого ключа соответствующего разряда, а выход триггера каждого разряда регистра кода отрицательного числа соединен со входом управления второго ключа соответствующего разряда преобразователя код-напряжение, при этом кодовые шины регистров кода положительного и отрицательного чисел подключены к соответствующим входам сумматора. Источники информации, принятые во внимание при экспертизе 1.Цифровые электроизмерительные приборы. Под ред. В.М. Шляндина, М.. Энергия, 1972, с. 336, рис. 9-8. 2.Островерхое В.В. Динамические погрешности аналого-цифровых преобразователей. Л., Энергия , 1975, с. 52, рис. 3-1 (прототип).

X

J9Э

&

k A

и%

ч

t

м

«

KJ

«

t-

i

--0 S

ie.

rraK

te

%3t

,tfi

t

CH

let

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналого-цифровой преобразователь | 1990 |

|

SU1720160A1 |

| Преобразователь напряжения в код | 1979 |

|

SU851767A1 |

| Устройство для считывания графической информации | 1987 |

|

SU1451742A1 |

| МНОГОМЕРНЫЙ СТАТИСТИЧЕСКИЙ АНАЛИЗАТОР ВЫБРОСОВ И ПРОВАЛОВ НЕСТАЦИОНАРНОГО НАПРЯЖЕНИЯ | 2000 |

|

RU2189631C2 |

| ПРЕОБРАЗОВАТЕЛЬ НАПРЯЖЕНИЯ В КОД С САЛ1ОКОНТРОЛЕМ | 1973 |

|

SU379051A1 |

| ПАРАЛЛЕЛЬНЫЙ ИДЕНТИФИКАТОР КРИТИЧЕСКИХ ВЫБРОСОВ И ПРОВАЛОВ ПРИ СТАЦИОНАРНОМ И НЕСТАЦИОНАРНОМ НАПРЯЖЕНИИ СЕТИ | 2001 |

|

RU2191427C1 |

| УСТРОЙСТВО для ЦИФРОВОГО РЕГУЛИРОВАНИЯ СКОРОСТИ | 1973 |

|

SU374580A1 |

| Аналого-цифровой преобразователь с коррекцией динамических погрешностей | 1976 |

|

SU744968A1 |

| Аналого-цифровой преобразователь | 1985 |

|

SU1297224A1 |

| Преобразователь напряжение-код | 1972 |

|

SU474103A1 |

Авторы

Даты

1982-01-15—Публикация

1975-10-22—Подача