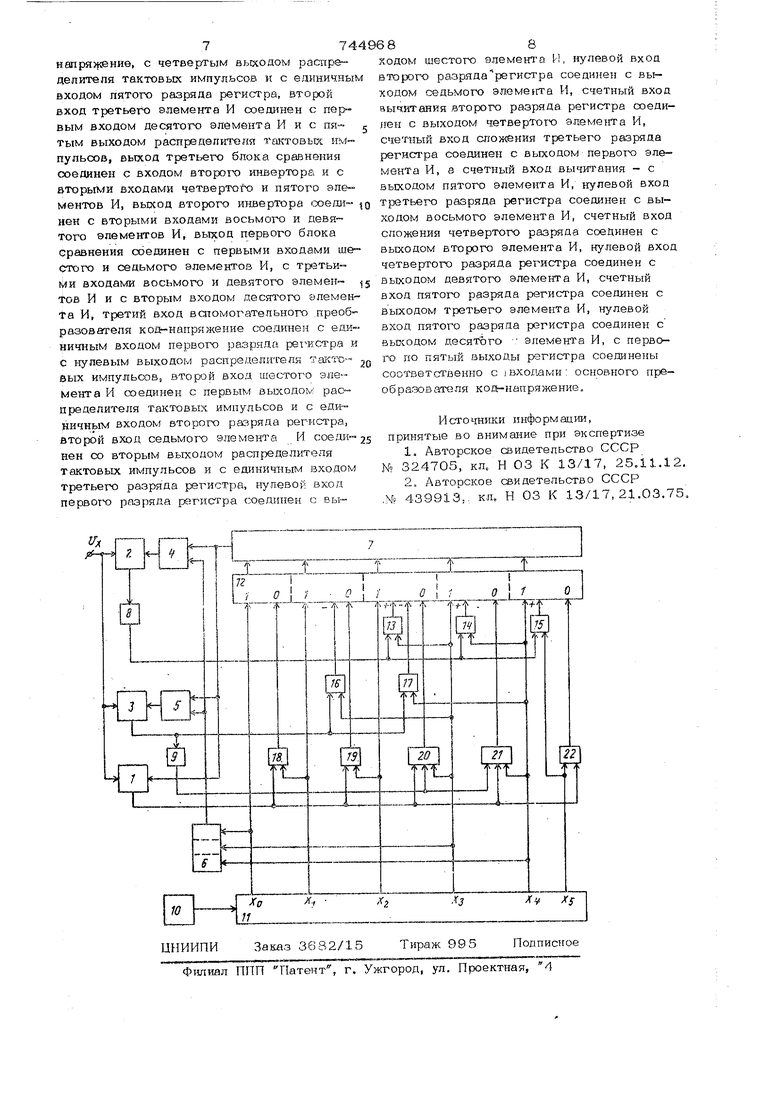

Изобретение относится к импульсной технике и может использоваться в анапого цифровых преобразоватепях, предназначенных для измерения изменяющихся напряжений, обеспечивая при простой технической реализации высокое быстродействие. Известен аналого-цифровой преобразова тель с проведением коррекции в процессе поразрядного уравновешивания, содержащий два сравнивающих устройства, два преобразоввггеля кода в напряжение, регистр триггеров, логические схемы, тактовый ге нератор, распределитель импульсов, в котором один вход второго сравнивающего устройства подключен к источнику измеряемого сигнала, второй вход соединен с схемой суммирования напряжений преобразователей кодов в напряжения, выходы сравнивающих устройств соединены с входами дополнительных схем совпадения, к другим входам которых подключены выходы распределителя тактовых импульсов, од ни входы дополнительных схем совпадения соединены с схемами сложения, а другие - С схемами вычитания единицы , включенными в младшие разряды регистра триггеров; управляющие входы второго преобразователя кода в напряжение соответственно соединены с шинами распределителя тактовых импульсов младщ1гх разрядов преобразователя JlJ . Однако импульсы с выходов схем совпадения одновременно поступают на установочный вход триггеров младших разрядов и в цепь переноса, в связи с чем нормальное функционирование регистравозможно только при включении в цепи переноса дополнительных схем задержек, что приводит к увеличению времени преобразования. Кроме того, область применения таких устройств ограничена невозрастающими натряжениями. Наиболее близким по технической сущности к предлагаемому является устройство, содержащее блоки сравнения преобразовЕггель кодов в напртжение, блок контрольных напряжений, блоки суммированиа напряжений, логические элементы, ге- нератор тактовых импульсов, распредепитепь тактовых импульсов, дополнительный преобразователь кода в напряжение, анало говый выход которого подключен к блоку суммирования компенснрунхцих нбпря;«ений а цифровой выход соединен с входом циф рового сумматора, на другой вход которого подключен цифровой выход основного преобразователя кода в напряжение 21 . В этом устройстве быстродействие определяется временем преобразования основ ного преобразователя коа-напряжение (ПК и временем суммирования цифрового сумма тора. Преобразователь может работать как рбласти возрастающих, так и в обласгги убывающих измеряемых напряжений. Увели Чение быстродействия и расширение област Применения достигается введением в устройство дополнительных узлов: блока конт рольных напряжений, схемы сравнения, ан логовой схемы суммирования, цифрового сумматора. Усложнение схемы для обеспечения повышенного быстродействия является главным недостатком этого устройства. Целью изобретения является упрощение работы устройства при сохранении высоко го быстродействия. Цель достигается тем, что в ана:1ого- цифровой преобразователь с коррекцией динамических погрешностей, содержащий первый блок сравнения, один вход которого соединен с щиной (Входного и первыми входами второго и третьего блоков Сравнения, второй вход первого бпока сравнения соединен с первыми входами блоков суммирования и вычитания н.апря жений и с выходом основного ПКН, второ вход второго блока сравнения соединен с выходом блока суммирования, а вто;рой вход третьего блока сравнения соединен с выходом блока вычитания напряж€ НЙй, вторые входы блоков суммирования и вычитания соединены с выходом вспомогательного ПКН, выход генератора тшсто вых импульсов соединен с входом распределителя тактовых импульсов (РТИ), введены инверторы, регистр, элементы И, причем вход первого инвертора соединен с выходом второго блока сравнения, а его выход соединен с первыми входами первого, второго и третьего элементов И, второй вход первого элемента И соединен с первыми входами четвертого и восьмого элементов И, с первым входом вспомогательного ПКН, с единичным входом четвертого разряда регистра и с третьим выходом РТИ, второй вход второго элемента И соединен с первыми входами пятого и девятого эпементов И, с вторым входом вспомогательного ПКН, с четве гTbiM выходом РТИ и с единичным вхопом пятого разряда регистра, второй вход третьего элемента И соегшиен с первым входом десятого элемента И и с пятым выходом РТИ, выход третьего бпока сравнения соединен с входом второго инвертора и с вторыми входами четвертого и пятого элементов И, выход второго инвертора соединен с вторыми входами восьмого и девятого элементов И, выход первого блока сравнения соединен с первыми входами шестого и седьмого эпементов И, с третьими входами восьмого и девятого элементов И и с вторым входом десятого элемента И, третий вход вспомогательного ПКН соединен с единичным входом первого разряда регистра и с нулевым выходом РТИ, второй вход шестого элемента И соединен с первым выходом РТИ и с единичным входом второго разряда регистра, второй вход седьмого элемента И соединен с вторым выходом РТИ и с единичным входом третьего разряда регистра, нулевой вход первого разряда регистра соединен с выходом шестого элемента И, нулевой вход второго разряда регистра соединен с выходом седьмого элемента И, счетный вход вычитания второго разряда регистра соединен с выходом четвертого элемента И, счетный вход сложения третьего разряда регистра соединен с выходом первого элемента И, а счетный вход вычитания - с выходом пятого элемента И, нулевой вход третьего разряда регистра соединен с выходом восьмого элемента И, счетньЕЙ вход сложения четвертого разряда регистра соединен с выходом второго элемента И, нулевой вход четвертого разряда регистра соединен с выходом девятого элемента И, счетный вход пятого разряда регистра соединен с выходом третьего элемента И, нулевой вход пятого разряда регистра соединен с выходом десятого элемента И, с первого по пятый выходы регистра соединены соответственно с входакти основного ПКН. На чертеже представлена структурная электрическая схема предлагаемого преобразователя. Преобразователь содержит блоки сравнения 1,2,3, аналоговые блоки суммирования 4 и вычитания 5 напряжений, вспомогательный 6 и основной 7 преобразователи код-напряжение, первый инвертор 8 и второй инвертор 9, генератор тяктовых импульсов Ю, распределитель тактовых импульсов 11, регистр 12, элемент, И 13-22. Преобразователь работает следующим образом. Импульсом Хдустанавливается начальное состояние, при этом включаются стар шие разряды преобразователей кодов 7 и 6 Затем с шин распределителя 11 поспедовательно выдаются импульсы Х и Х2 и производится ураврювешивание старшими разрядами ПКН 7 как в известных преобразователях. Блоки сравнения 1,2,3 вырабатывают сигнал I, если , , -, О, еспи , -v-U, U UQ-UJ соответственно. Будем считать первг 1ми старшие разр ды в преобразователях 6, 7 и регистре 12, тогда младший разряд в регистре 12 и преобразователе 7 будет пятым, а в npe образователе 6 - третьим. Импульс Х устанавливает в единичное состояние четвертый разряд регистра 12 и может пройти на один из трех входов регистра: установку нуля третьего разря- да, счетный вход сложения третьего разряда, либо счетный вход вычитания второго разряда. При UQ и DO+U,импульс Ко, проходит лишь в цепь установки единицы четвертого разряда Число в регистре увеличивается на 2 единицы младшего разряда, как и в обычном ПКН поразрядного сравнения. При УО К оимпульс кроме установки в единицу четвертого разряда проходит через элемент 18 в цеп установки нулевого состояния третьего разряда. В результате число в регистре уменьшается на 2 единицы, как и в обычном ПКН поразрядного сравнения. При Uy UQ-vU,импульс XT, кроме установки в единицу четвертого раз ряда (при этом число в регистре увеличивается на+2 единицы) через элемент 16 проходит на счетный вход сложения третьего разряда, чем увеличивает число в регистре на +4 единицы. В результате число в регистре увеличивается не на +2 единицы, как в обычном ПКН поразрядного Сравнения, а на+2 +4 +6. Таким образом происходит коррекция процесса преобразования на +4 единицы. При импульс Х-1 кроме установки в единицу четвертого разряда (при этом число в регистре увеличивается на+2 единицы), через элемент 14 проходит на счетный вход вычитания второго разряда, чем уменьшается числю 7 8 в регистре на -8 единиц. В результате число в регистре уменьшается +2 - единиц. Таким образом происходит коррекция процесса преобразования на -4 ед1ь ницы. Аналогично импульсом Х может быть проведена коррекция на+2 единицы мл. разряда. Импульсом Х, число в регистре может быть изменено на единицу в сторону увеличения через элемент 21 и в сторону уменьшения через элемент 22. Использование предлагаемого устройства позволит при высоком быстродействии упростить известное устройство, исключив из него наиболее сложные узлы, такие, как цифровой сумматор, аналоговый сумматор, блок контрольных напряжений. формула изобретения Аналого-цифровой преобразователь с коррекцией динамических погрешностей, содержащий первый блок сравнения, один вход которого соединен с шиной входного сигнала и первыми входами второго и третьего блоков сравнения, второй вход первого блока сравнения соединен с пер)выми входами блоков суммирования и вычитания напряжений и с выходом основного преобразователя код-непряжение, второй вход второго блока сравнения соединен с выходом блока суммирования,- а второй вход Третьего блока сравнения соединен с выходом блока вычитания напряжений, вторые входы блоков суммирования и Вычитания соединены с выходом вспомогательного преобразователя код-напряжение, выход генератора тактовых импульсов соединен со входом распределителя тактовых импульсов, отличающийся тем, что, с целью упрощения работы устройства при сохранении высокого быстродействия, в него дополнительно введены инверторы, регистр, элементы И, причем вход первого инвертора соединен с выходом второго блока сравнения, а его выход соеди- . нен с первыми входами первого, второго и третьего элементов И, второй вход первого элемента И соединен с первыми входами четвертого и восьмого элементов И, с первым входом вспомогательного преобразователя код-напряжение, с единичным входом четвертого разряда регистра и с Третьим выходом распределителя тактовых импульсов, второй вход второго элемента И соединен с первыми входами пятого и девятого элементов И, с вторым входом вспомогательного преобразователя код

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналого-цифровой преобразователь с коррекцией динамических погрешностей | 1979 |

|

SU782147A2 |

| Аналого-цифровой преобразователь с коррекцией динамических погрешностей | 1976 |

|

SU660240A1 |

| Аналого-цифровой преобразователь | 1988 |

|

SU1524178A1 |

| Преобразователь напряжения в код | 1979 |

|

SU851767A1 |

| Аналого-цифровой преобразователь поразрядного кодирования | 1976 |

|

SU657607A1 |

| Аналого-цифровой преобразователь | 1988 |

|

SU1589395A1 |

| Аналого-цифровой преобразователь | 1984 |

|

SU1270895A1 |

| Преобразователь напряжения в код | 1979 |

|

SU841111A1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 1991 |

|

RU2012132C1 |

| Устройство для вычисления показателя экспоненциальной функции | 1986 |

|

SU1335990A1 |

Авторы

Даты

1980-06-30—Публикация

1976-03-18—Подача