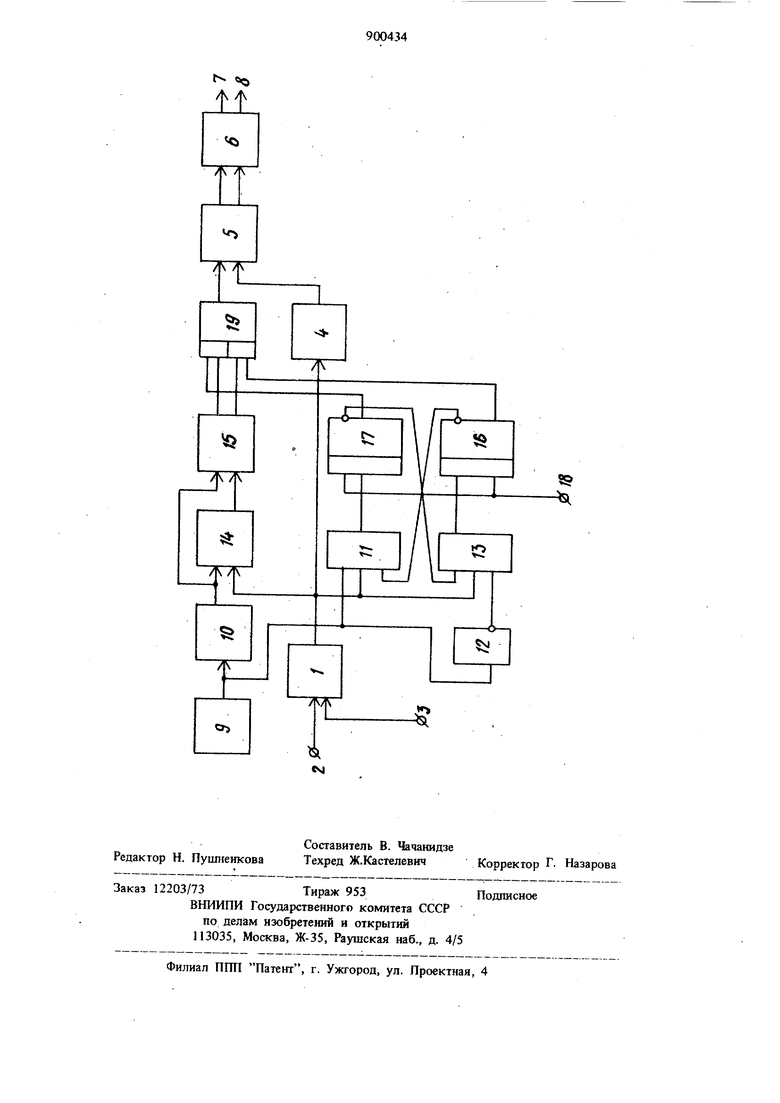

(54) ДЕШИФРАТОР ВРЕМЯ-ИМПУЛЬСНОГО Изобретение относится к автоматике. Наиболее близким техническим решением к предлагаемому является дешифратор вре.мя импульсного кода, содержащий основной ком паратор, входы которого соединены с входной цшной и шиной порогового напряжения, а выход через элемент задержки подключен к первому входу основного элемента И, выходы которого через блок анализа соединены с выходными шинами а также генератор тактовых импульсов {1 . Недостаток известного устройства низкая точность функционирования. Цель изобретения - повышенна точности дешифратора время-импульсного кода. Указанная цель достигается тем, что в дешифратор время-импульсного коя введены аналоговый блок памяти, генератор стробимпульсов, два триггера, инвертор, два допол нительных элемента И, дополнительный компа ратор и формирователь, вход которого соединен с выходом генератора тактовых импульсов, с первым входом первого дополниКОМтельного элемента И и через инвертор с первым входом второго дополнительного злемента И, а выход подключен к информационному входу аналогового блока памяти и первому входу допол1шгельного компаратора, второй вход которого соединен с выходом аналогового блока памяти, стробнрупщий вход которого nojiKjno4eH к выходу основного компаратора и вторым входам дополнительных элементов И, третий вход первого из которых соединен с нулевым выходом первого тртггер, а третий вход второго - с нулевьсм выходом второго триггера, единичный вход которого подключен к выходу первого допопнительпто элемента И, а нулевой вход - к шине установь и и нулевому входу первого триггера, едиргичный вход которого подключен к выходу второго дополнительного элемента И, при этом единичный выход первого триггера соединен t с первым входом генератора строб-импульсов, второй и третий входы которого подключены к выходам дополнительного компаратора, четвертый вход - к елиничиому выходу второго триггера, а выход соедннен со вторым входом основного элемента И. На чертеже представлена блок-схема дешифратора время-импуяьсного кода. Блок-схема содержит основной компаратор 1, входы которого соединены с входной шиной 2 и шиной 3 порогового напряжения, а выход через элемент 4 задержки подключен к первому входу основного элемента 5 И выходы которого через блок 6 анализа соединены с выходными шинами 7 и 8, генератор 9 тактовых импульсов, формирователь 10, вход которого соединен с выходом генератора 9 тактовых импульсов, с первым входом первого дополнительного элемента 11 И, и через инвертор 12 с первым входом второго дополнительного элемента 13 И, а выход поключен к информационному входу аналогового блока 14 памяти и первому вхоиу дополнительного компаратора 15, второй вход которого соединен с выходом аналогового блока 14. памяти, стробирующий вход которого подключен к выходу основного компаратора 1 и вторым входам дополнительных элементов 11 и 13 И, третий вход первого из которых соединен с нулевым выходом первого триггера 16, а третий вход второго - с нулевым выходом второго триггера 17, единичный вход которого подключен к выходу первого дополнительного элемента И И, а нулевой вход - к шине 18 установки и нулевому входу первого триггера 16, единичный вход которого подключен к выходу второго дополнительного элемента 13 И, единичный выход первого три гера 16 соединен с первым входом генератора 19 строб-импульсов, второй и третий выхо ды которого подключены к выходам дополни тельного компаратора 15, четвертый вход - к единичному выходу второго триггера 17, а выход соединен со вторым входом основно го элемента 5 И. .Дешифратор время-импульсного кода работает следующим образом. Генератор 9 тактовых импульсов работает, в непрерьшном режиме, и с его выхода тактовые импульсы с периодом, равным кодовому интервалу, подаются на вход формирователя 10, который вырабатьгеает непрерьшно пилообразное напряжение. По входной шине 2 видеоимпульсы поступают на первый вход компаратора 1, на второй вход которого подается уровень порогового напряжения. При превышении порогового уровня входным напряжением компаратор 1 вырабатьшает импул напряжения. При поступлении первого импульса хода на стробируюший вход аналогового блока 14 памяти последний запоминает значение напряжения на выходе формирователя 10 в момент поступления переднего фронта первого импульса. Запомненное напряжение с аналогового блока 14 памяти поступает на вход компаратора 15, на второй вход которого подается пилообразное напряжение с формирователя 10. Кроме того, при поступлении переднего фронта первого импульса кода триггерами 16 и 17 производится запоминание, на каком участке пилообразного напряжения возрастаюшем или падающем - пришел первый импульс. При появлении переднего фрон- та первого импульса на возрастаюшем участке пилообразного напряжения происходит срабатывание элемента 11 И, на вькоде которого появляется уровень логического нуля, устанавливаюший триггер 17 в единичное состояние, и уровень логической единицы поступает на четвертый вход генератора 19 строб-импульсов. На первый вход генератора 19 строб-импульсов поступает уровень логического нуля с единичного выхода триггера 16, так как этот триггер остается в первоначальном нулевом состоянии вследствие наличия в момент установки триггера 17 на входе элемента И 13 уровня логического нуля, проинвертированного инвертором 12 уровня логической единицы с выхода генератора 9 тактовых импульсов. После установки триггера 17 в единичное состояние с его нулевого выхода поступает на вход элемента 13 И уровень логического нуля, запрешающий установку триггера 16 в единичное состояние до окончания обработки данного кода. Аналогично работают элементы 11 и 13 И, инвертор 12 и триггеры 16 и 17 ПРИ попадании первого импульса кода во время формирования подаюшего пилообразного напряжения, но триггер 17 остается в исходном нулевом состоянии, а триггер 16 устанавливается в единичное состояние. Поступающий на четвертый вход генератора 19 строб-импульсов с единичного выхода триггера 17 уровень логической единицы приводит к формированию этим генератором 19 строб-импульсов, по положительным перепадам напряжения с соответствующего входа компаратора 15; длительность строб-импульсов выбирается из условия обеспечения приема импульсов кода при всех допустимых флуктуациях по времени. Строб-импульсы с генератора 19 строб-импульсов поступают на первый вход элемента 5 И, на второй вход которого постзшают задержанные с помощью элемента 4 задержки импульсы с выхода компаратора 1. Элемент задержки 4 обеспечивает некоторую небольшую задержку импульсов кода для попадания всех импульсов кода в строб-импульсы, что объясняется нестабильностью запуска дешифратора время-импульсного кода по первому импульсу за счет флуктуации положения этого импульса во времени.

Элемент 5 И вьщает по первому выходу импульсы единичного напряжения при попадании импульса в строб-импульс и по второму выходу импульсы единичного напряжения при отсутствии импульса кода в строб-импульс. Блюк б анализа пртиимает решение о соответствии пртнятого кода с одним из возможных и выдает на выход импульс расшифровки кода и номер этого кода в виде двоичной импульсной последовательности.

Таким образом, предложенный деишфратор время-ямпульс1юго кода по сравнению с язвестшлм обеспечивает тачную селекцию импульсе кода при использовашш элементной базы с относительно низким быстродействием

Формула изобретення

Дешифратор время-импульсного кода, со- 20 держащий основной компаратор, входы которого соедииены с вхошюй ишной и шиной порогового напряжения, а выход юрез элемент задержки подключен к пе{тому входу основного злемента И, вьосоды которого через блок 25 анализа соедаиены с выxoдны(И шинами, а также генератор тактовых импульсов, отличающийся тем, что, с целью повьпоения то «ости, введены аналоговый бл1ж памяти, генератор строб-имт льсов, два тртггера, зо нтвертор, два дополяительшдх элементов И, Д(шолш1тельный компаратор и формирователь.

вход которого соединен с выходом г.енераторй тактовых импульсов, с первым входом перво го дополнительного элемента И и через инвертор с первым входом второго дополнительного элемента И, а выход подключен к информадионному входу аналогового блока памяти и первому входу дополнительного компаратора, второй вход которого соединен с выход(ни аналогового блока памяти, стробнрующий вход которого подключен к выходу основного компаратора и вторым входам дополнительных -элементов И, третий вход первого из которых соединен с нулевым выходом первого триггера, а третий вход второго с нулевьп« выход(м второго триггера, единичный вход которого подключен к выходу первого дополнительного злемента И, а нулевой вход - к шине установки и нулевому входу первого триггера, единичный вход которого подключен к выходу второго дополнительного элемента И, при этом единичный выход первого тртггера соединен с первым входом генератора строб-импульсов, второй и третий входы которого подключены к выходам дополнительного компаратора, четвертый вход - |К единичному выходу второго триггера, а выход соединен со вторым входом Ъсновного элемента И.

Источники информации, пртшятые во внимание при экспертизе 1. Радиоэлектроника за рубежом, 1972, вып. 47, с. 18, рис. 8 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальный аналого-цифровой преобразователь | 1980 |

|

SU993468A1 |

| Декодирующее устройство | 1990 |

|

SU1783612A1 |

| МНОГОКАНАЛЬНОЕ УСТРОЙСТВО КОНТРОЛЯ ТЕМПЕРАТУРЫ | 2015 |

|

RU2631018C2 |

| Устройство для контроля электрических параметров цифровых узлов | 1984 |

|

SU1260974A1 |

| Многоканальная стабилизирующая система электропитания | 1987 |

|

SU1444736A1 |

| СТАТИСТИЧЕСКИЙ АНАЛИЗАТОР ФУНКЦИИ МОМЕНТОВ ЕРМАКОВА В.Ф. | 1994 |

|

RU2092897C1 |

| Устройство для ввода информации | 1984 |

|

SU1247855A1 |

| БЫСТРОДЕЙСТВУЮЩИЙ ПРЕОБРАЗОВАТЕЛЬ ПЕРЕМЕННОГО НАПРЯЖЕНИЯ В ЦИФРОВОЙ КОД ОТКЛОНЕНИЯ | 1992 |

|

RU2074396C1 |

| Устройство для считывания графической информации | 1989 |

|

SU1635203A1 |

| РЕГИСТРАТОР ПАРАМЕТРОВ АВАРИЙНЫХ СИТУАЦИЙ В ЭЛЕКТРИЧЕСКИХ СЕТЯХ ПОВЫШЕННОЙ ТОЧНОСТИ (ВАРИАНТЫ) | 2008 |

|

RU2376625C1 |

Авторы

Даты

1982-01-23—Публикация

1980-04-04—Подача