Выход

-ч оо со о

ю

Изобретение относится к технике электросвязи и может быть использовано в волоконно-оптических цифровых системах передачи информации, использующих в качестве линейного сигнала код СМ1.

Цель изобретения - повышение помехоустойчивости устройства.

Предлагаемое изобретение позволяет осуществить декодирование кода СМ1 по минимуму эвклидова расстояния, что в случае аддитивного белого Гауссовского шума эквивалентно декодированию по максимуму правдоподобия. Достижение поставленной цели осуществляется за счет того, что минимальное эвклидово расстояние опре

деляется не путем подсчета эвклидовых расстояний для всех разрешенных кодовых слов с последующим их сравнением, а используя структуру и симметрию кода СМ1,

количество операций необходимых для определения минимального эвклидова расстояния резко сокращено. При этом появляется вероятность исправлять все обнаруживаемые ошибки, не требуются

аналого-цифровые преобразователи, что позволяет достичь поставленной цели в высокоскоростных цифровых системах передачи. Достижение поставленной цели проиллюстрировано следующим образом.

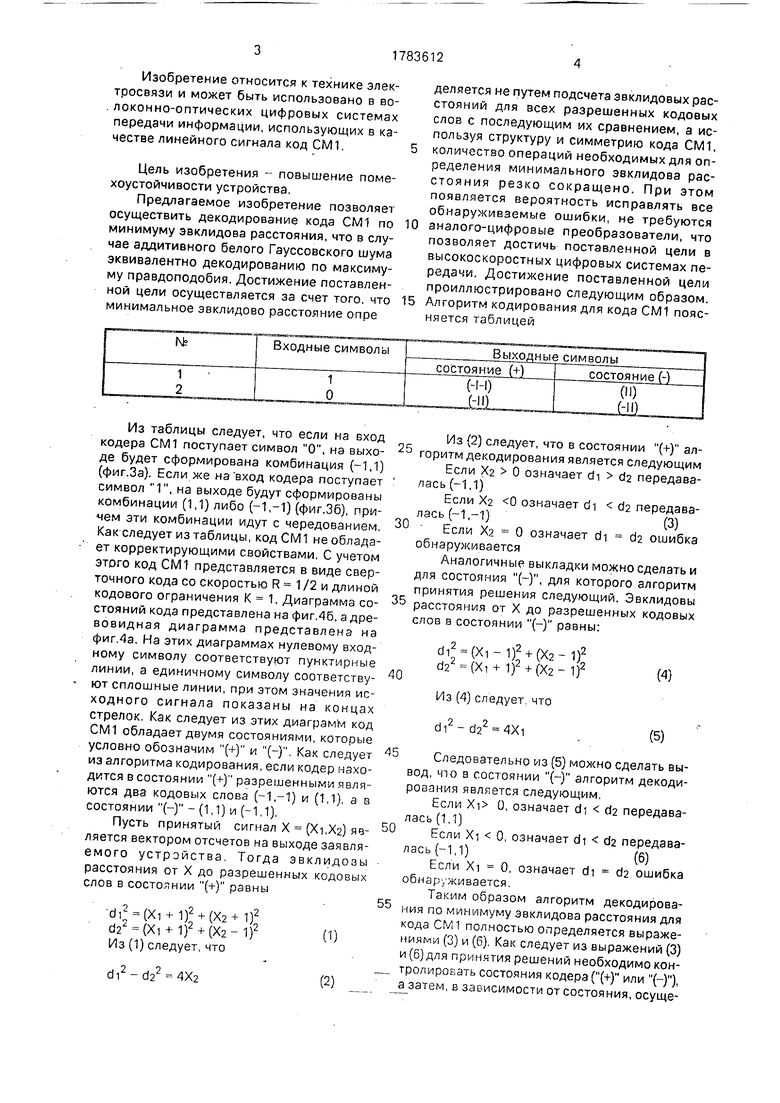

Алгоритм кодирования для кода СМ1 поясняется таблицей

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для ввода-вывода полутоновой информации | 1984 |

|

SU1164717A1 |

| Устройство для мажоритарного декодирования в целом | 1989 |

|

SU1688415A1 |

| Устройство регенерации трехуровневого биполярного сигнала | 1989 |

|

SU1800648A1 |

| УСТРОЙСТВО БУФЕРИЗАЦИИ И СИНХРОНИЗАЦИИ ДЛЯ ОБРАБОТКИ НЕПРЕРЫВНОГО СИГНАЛА | 1990 |

|

SU1812885A1 |

| Устройство для регенерации биимпульсных сигналов | 1989 |

|

SU1688413A1 |

| Устройство для регенерации биимпульсных сигналов | 1987 |

|

SU1594707A1 |

| Устройство управления коммутацией сообщений | 1980 |

|

SU955018A1 |

| Устройство для мажоритарного декодирования | 1987 |

|

SU1517137A1 |

| УСТРОЙСТВО КОДИРОВАНИЯ-ДЕКОДИРОВАНИЯ ИНФОРМАЦИИ | 1994 |

|

RU2115231C1 |

| Устройство для диагностики неисправностей технических объектов | 1988 |

|

SU1536357A1 |

Изобретение относится к технике электросвязи и может быть использовано в во- л оконно-оптических цифровых системах передачи информации, использующих в качестве линейного сигнала код CMI. Цель изобретения - повышение помехоустойчивости устройства. Устройство содержит два входных усилителя 1, 2, блок 3 аналоговой памяти, умножитель 4, три элемента НЕ 5,10, 11, блок управления 6, блок коммутации 7, компаратор 8, дешифратор 9, два элемента 2И 12,13, элемент 2 ИЛИ 14, два триггера 15, 16, В предлагаемом изобретении декодирование линейного кода СМ I осуществляется по минимуму эвклидова расстояния, что в случае аддативного белого Гоауссовского шума эквивалентно декодированию по максимуму правдоподобия, причем поставленная цель достигается без использования аналого-цифровых преобразователей, что существенно сокращает время обработки сигнала и позволяет использовать предлагаемое устройство в высокоскоростных в олоконно-оптических цифровых системах передачи информации. 1 табл. 16 ил. сл с

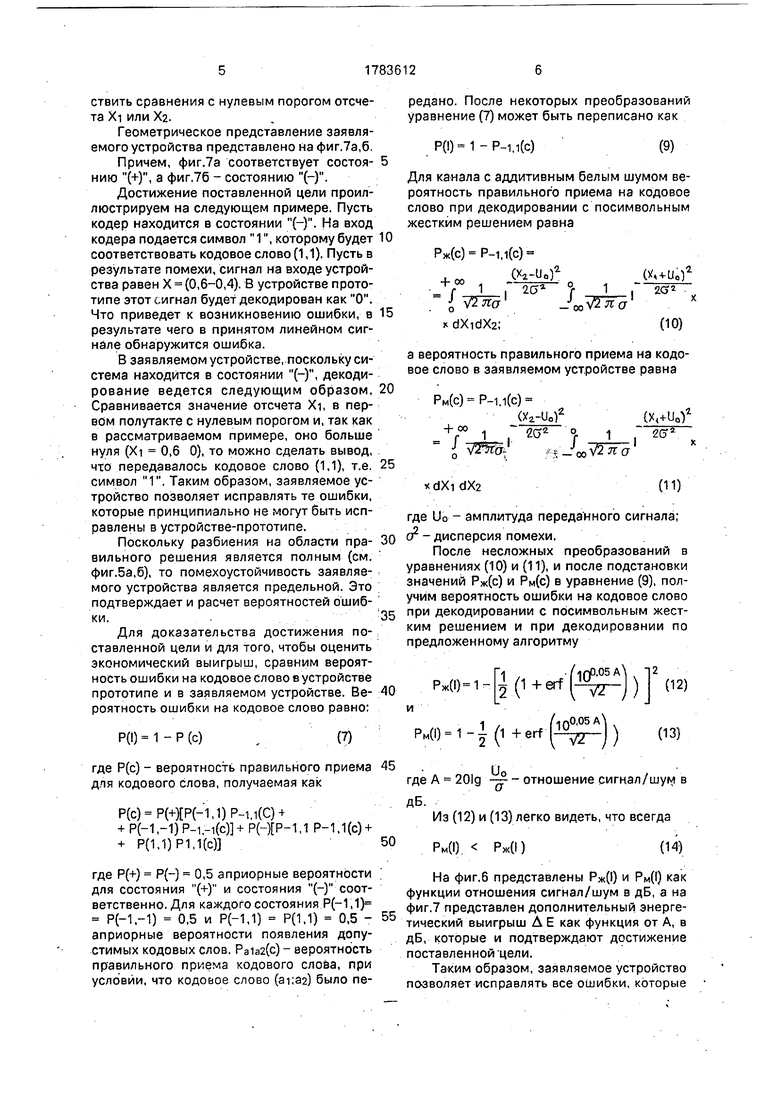

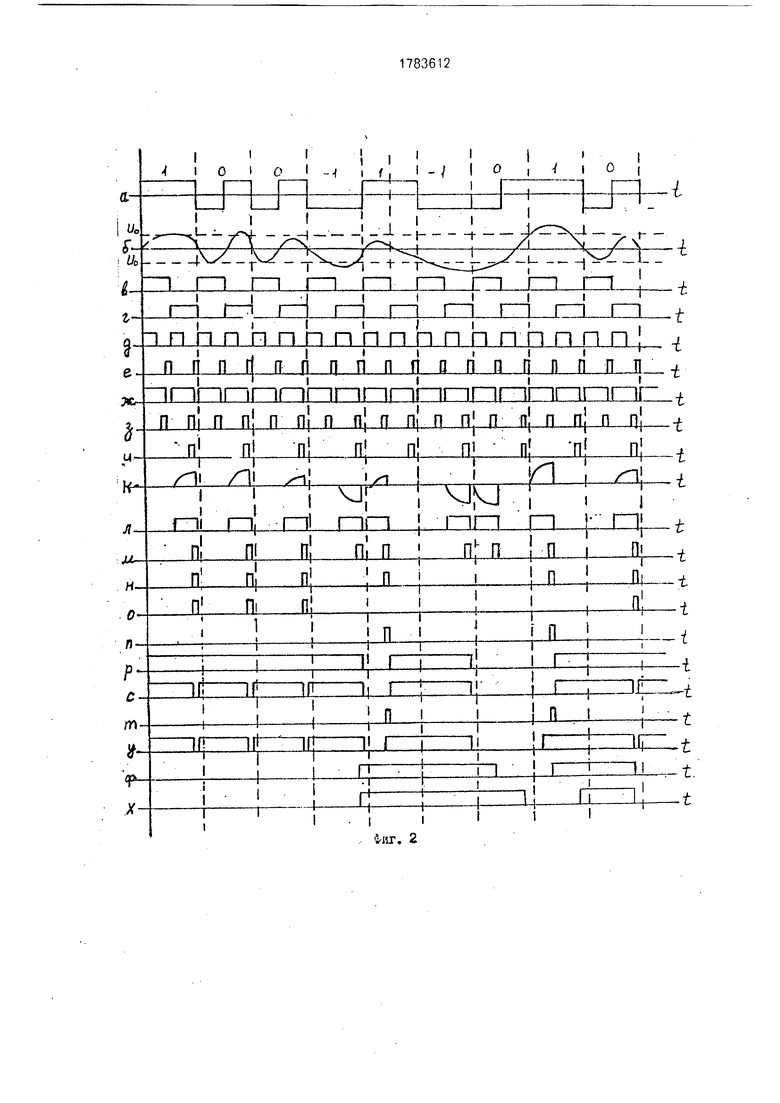

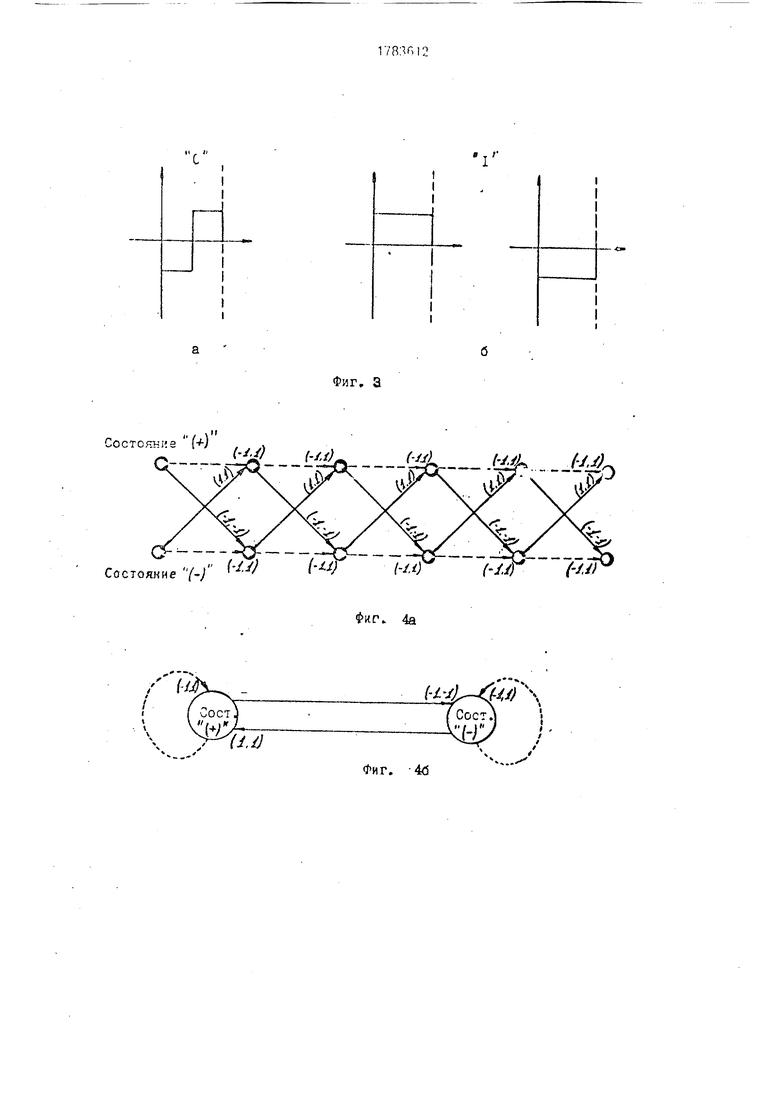

Из таблицы следует, что если на вход кодера СМ1 поступает символ О, на выходе будет сформирована комбинация (-1,1) (фиг.За). Если же на вход кодера поступает символ 1, на выходе будут сформированы комбинации (1,1) либо (-1.-1) (фиг.Зб), причем эти комбинации идут с чередованием. Как следует из таблицы, код СМ 1 не обладает корректирующими свойствами, С учетом этого код СШ представляется в виде свер- точного кода со скоростью R 1/2 и длиной кодового ограничения К 1. Диаграмма состояний кода представлена на фиг.4б, а древовидная диаграмма представлена на фиг.4а. На этих диаграммах нулевому входному символу соответствуют пунктирные линии, а единичному символу соответствуют сплошные линии, при этом значения исходного сигнала показаны на концах стрелок. Как следует из этих диаграмм код СМ1 обладает двумя состояниями, которые условно обозначим (+) и (-), Как следует из алгоритма кодирования, если кодер находится в состоянии () разрешенными являются два кодовых слова (-1.-1) и (1,1), а в состоянии (-) - (1,1) и (-1,1).

Пусть принятый сигнал X (Xi,X2) является вектором отсчетов на выходе заявляемого устройства Тогда эвклидозы расстояния от X до разрешенных кодовых слов в состоянии (+) равны

di; (Xi + D2 + (x2+i)2

«12 (ХИ 1)2 + (X2-1)2 Из (1) следует, что

di2-d22-4X2

Из (2) следует, что в состоянии (+) алгоритм декодирования является следующим

Если Х2 0 означает di d2 передавалась (-1,1)

Если Х2 0 означает сН d2 передавалась (-1.-1)(3)

Если Хг О означает di d2 ошибка обнаруживается

Аналогичные выкладки можно сделать и

для состояния (-), для которого алгоритм

принятия решения следующий. Эвклидовы

расстояния от X до разрешенных кодовых

спов а состоянии (-) равны:

40

di2 (Xi 1)2 + (Хг- 1)2 d22-(Xi + 1)2 + (X2- 1)2

(4)

Из (4) следует что

di2-d22 4Xi

(5)

45

50

55

Следовательно из (5) можно сделать вывод, что в состоянии (-) алгоритм декодирования является следующим.

Если Xi 0, означает di d2 передавалась (1,1)

Если Xi 0, означает di d2 передавалась (-1,1)(6)

Если Xi 0, означает dt d2 ошибка обнаруживается.

Таким образом алгоритм декодирования по минимуму эвклидова расстояния для кода С№1 полностью определяется выражениями (3) и (6) Как следует из выражений (3) и (6) для принятия решений необходимо контролировать состояния кодера ((+) или (-)), а затем, в зависимости от состояния, осуществить сравнения с нулевым порогом отсчета Xi или Ха.

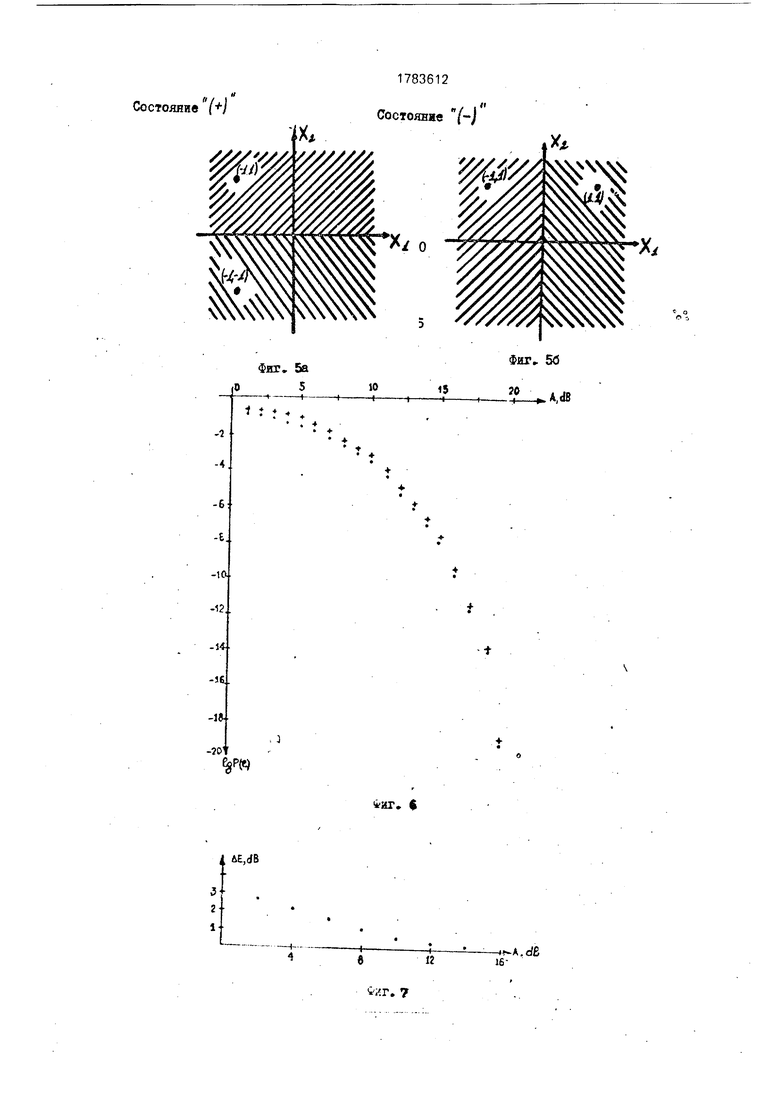

Геометрическое представление заявляемого устройства представлено на фиг.7а,б.

Причем, фиг.7а соответствует состоя- нию (+), а фиг.7б - состоянию (-).

Достижение поставленной цели проиллюстрируем на следующем примере. Пусть кодер находится в состоянии (-). На вход кодера подается символ 1, которому будет соответствовать кодовое слово (1,1). Пусть в результате помехи, сигнал на входе устройства равен X (0,6-0,4). В устройстве прототипе этот сигнал будет декодирован как О. Что приведет к возникновению ошибки, в результате чего в принятом линейном сигнале обнаружится ошибка,

В заявляемом устройстве, поскольку система находится в состоянии (-), декодирование ведется следующим образом. Сравнивается значение отсчета Xi, в первом полутакте с нулевым порогом и, так как в рассматриваемом примере, оно больше нуля (Xi 0,6 0), то можно сделать вывод, что передавалось кодовое слово (1,1), т.е. символ 1. Таким образом, заявляемое устройство позволяет исправлять те ошибки, которые принципиально не могут быть исправлены в устройстве-прототипе.

Поскольку разбиения на области пра- аильного решения является полным (см. фиг.5а,б), то помехоустойчивость заявляемого устройства является предельной. Это подтверждает и расчет вероятностей ошибки.

Для доказательства достижения поставленной цели и для того, чтобы оценить экономический выигрыш, сравним вероятность ошибки на кодовое слово в устройстве прототипе и в заявляемом устройстве. Be- роятность ошибки на кодовое слово равно:

Р(1) 1 - Р (с)

(7)

где Р(с) - вероятность правильного приема для кодового слова, получаемая как

Р(с)Р(+ХР(-1,1)Р-1.1(С) +

+ P(-1,-1)P-i-i(c)+P(-XP-1,1 P-1.1(c) +

+ Р(1.1)Р1.1(с)

где Р(+) Р(-) 0,5 априорные вероятности для состояния (+) и состояния (-) соответственно. Для каждого состояния Р(-1,1) Р(-1.-1) 0,5 и Р(-1,1) Р(1,1) 0,5 - априорные вероятности появления допустимых кодовых слов. Ра1а2(с) - вероятность правильного приема кодового слова, при условии, что кодовое слово (ai;aa) было передано. После некоторых преобразований уравнение (7) может быть переписано как

Р(1)-1-Р-1.1(с)

(9)

Для канала с аддитивным белым шумом вероятность правильного приема на кодовое слово при декодировании с посимвольным жестким решением равна

Рж(с) Р-и(с)

4-00(Xi-Uof

+Г°° 1 . о

dXidX2;

(Ю)

а вероятность правильного приема на кодовое слово в заявляемом устройстве равна

Рм(с)Р-1.1(с)

(Уг-Uc)2 + 1 - о1

J ЖЦ1 tiJtoWnb

dXi dX2

где Uo - амплитуда переданного сигнала;

о2 - дисперсия помехи.

После несложных преобразований в уравнениях (10) и (11), и после подстановки значений Рж(с) и Рм(с) в уравнение (9), получим вероятность ошибки на кодовое слово при декодировании с посимвольным жестким решением и при декодировании по предложенному алгоритму

(

1 +erf

710р.05А

г

(12)

1 // l00 05M v

Рм( (1 + erf ) (13) где А - 20lg - - отношение сигнал/шум в

ДБ.

Из (12) и (13) легко видеть, что всегда

Рм() Рж()(14)

На фиг.6 представлены Рж(1) и PM(t) как функции отношения сигнал/шум в дБ, а на фиг.7 представлен дополнительный энергетический выигрыш А Е как функция от А, в дБ, которые и подтверждают достижение поставленной-цели.

Таким образом, заявляемое устройство позволяет исправлять все ошибки, которые

обнаруживаются (но не исправляются) в устройстве-прототипе. Это позволяет повысить помехоустойчивость устройства-прототипа до предельно достижимой, При этом поставленная цель достигается без введения дополнительной избыточности, без введения аналого-цифрового преобразователя, что позволяет его использовать в высокоскоростных волоконно-оптических цифровых системах передачи.

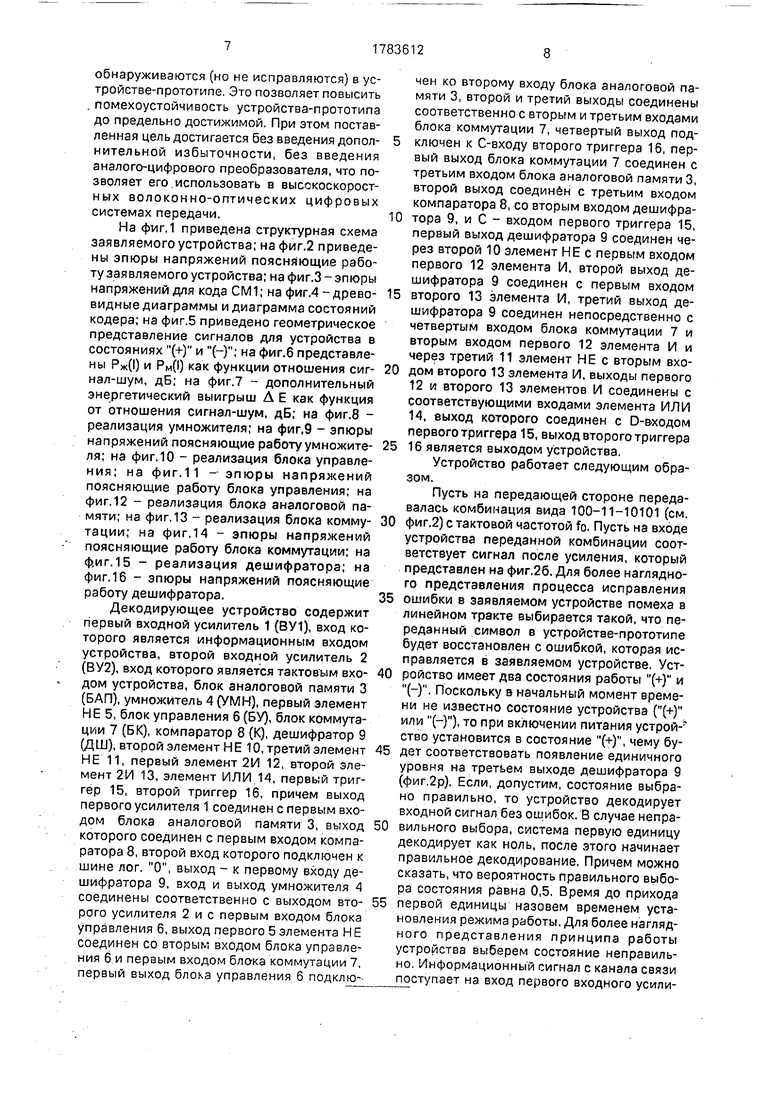

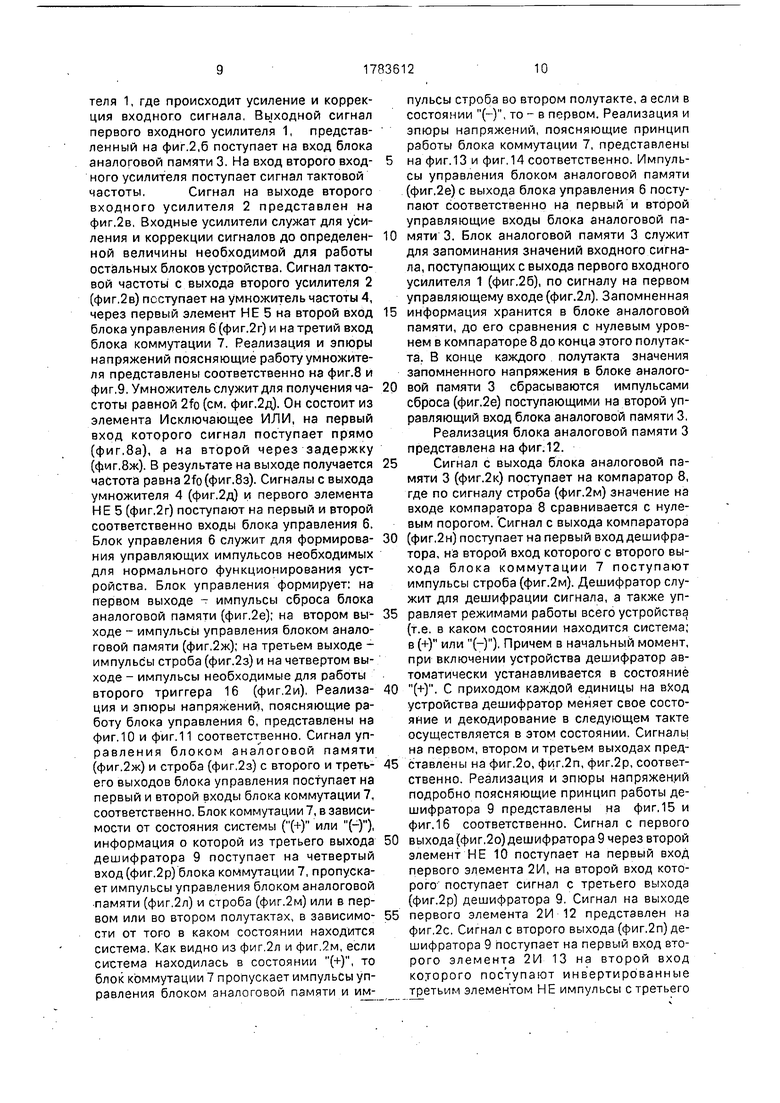

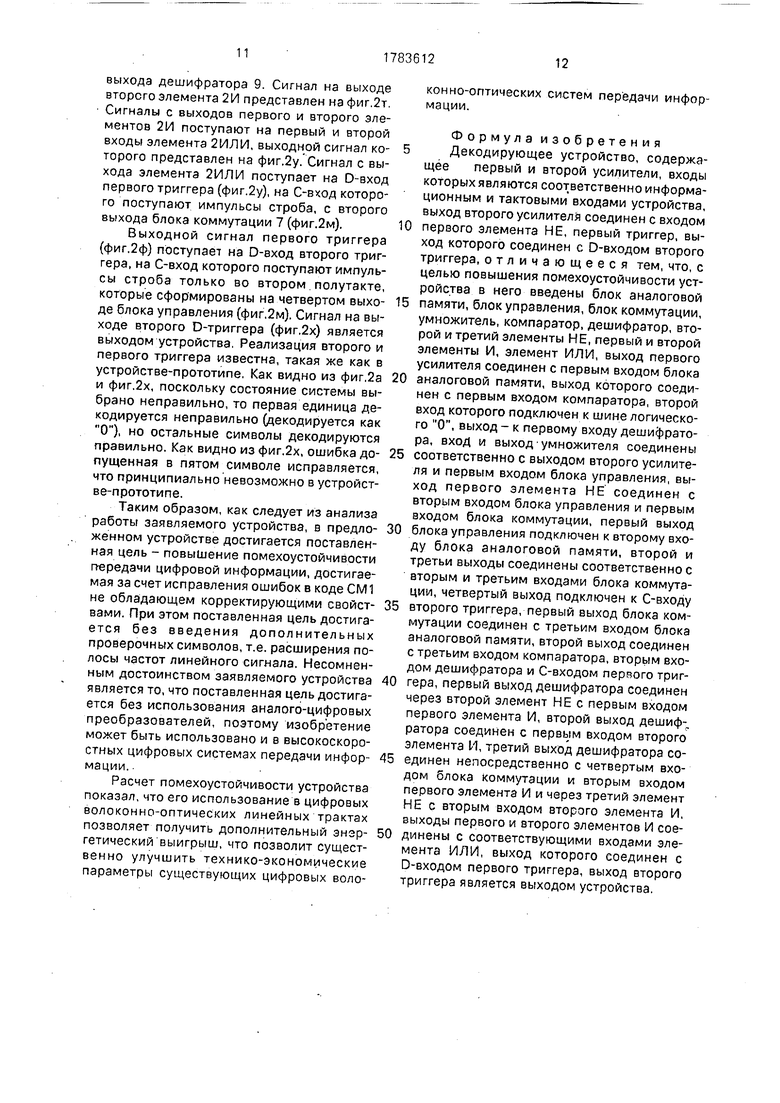

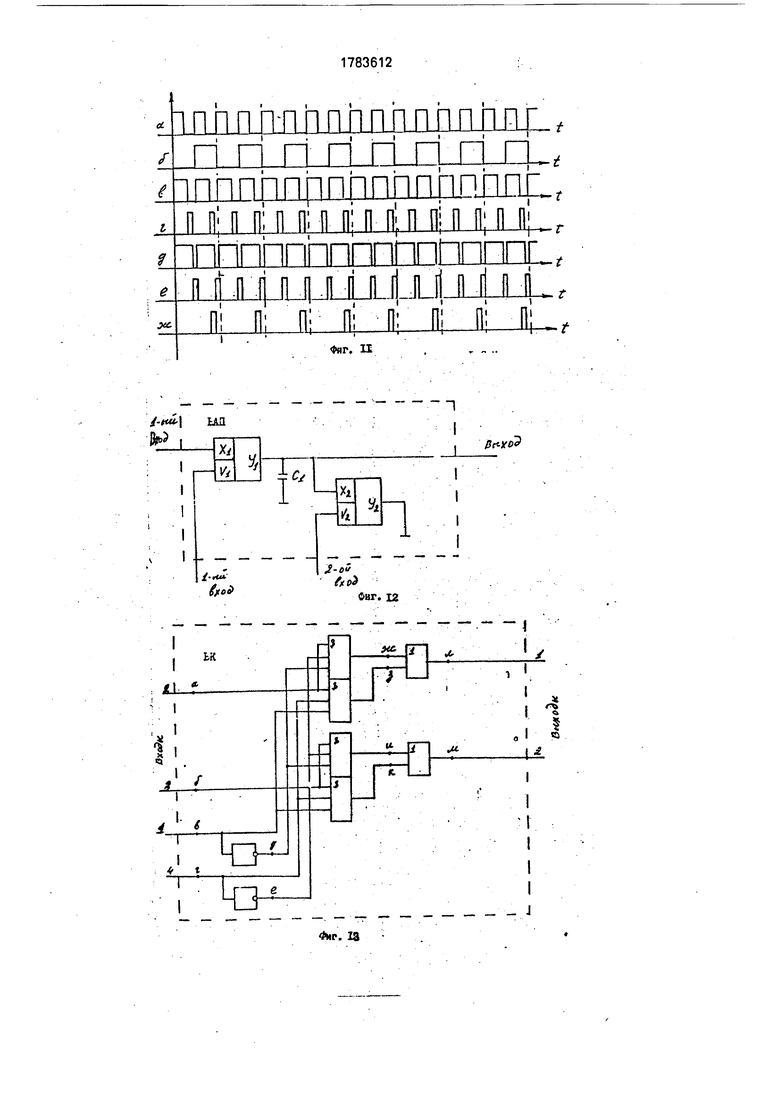

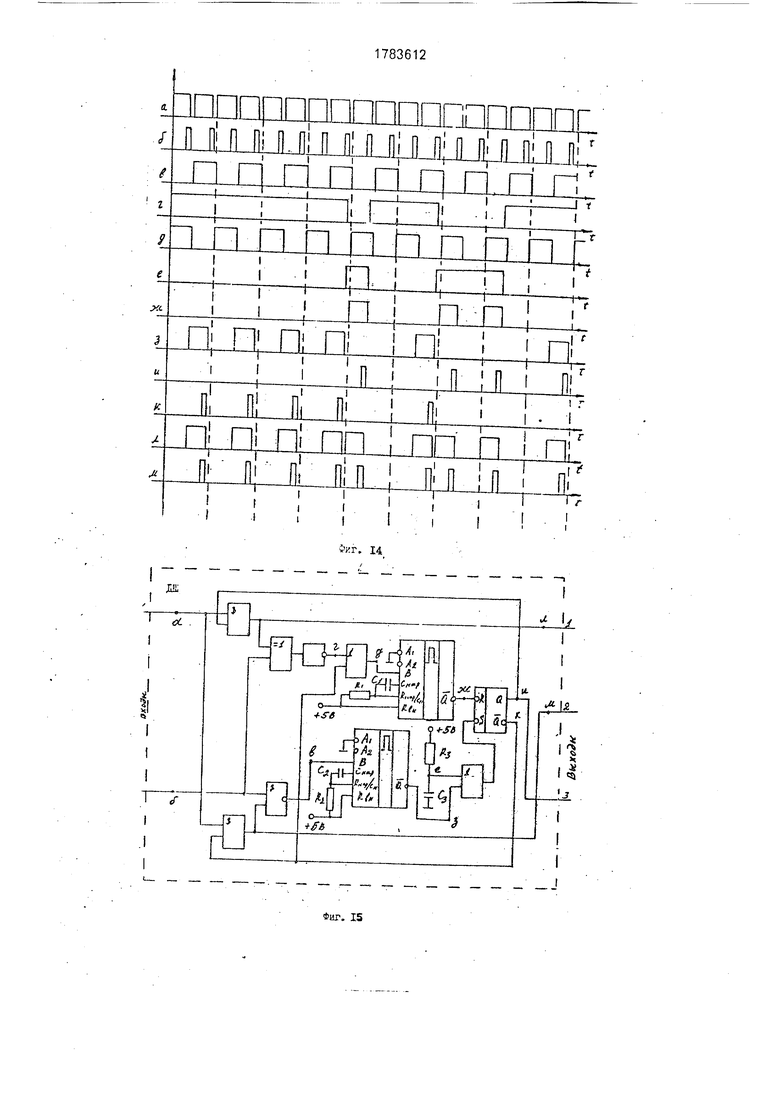

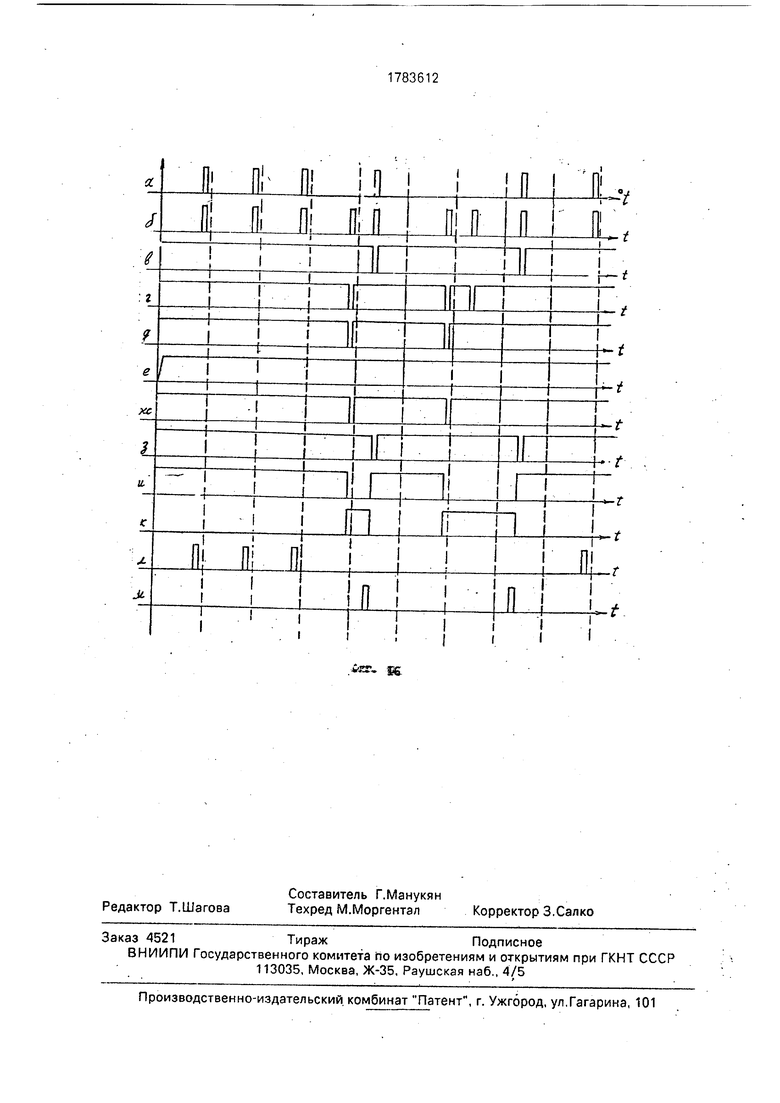

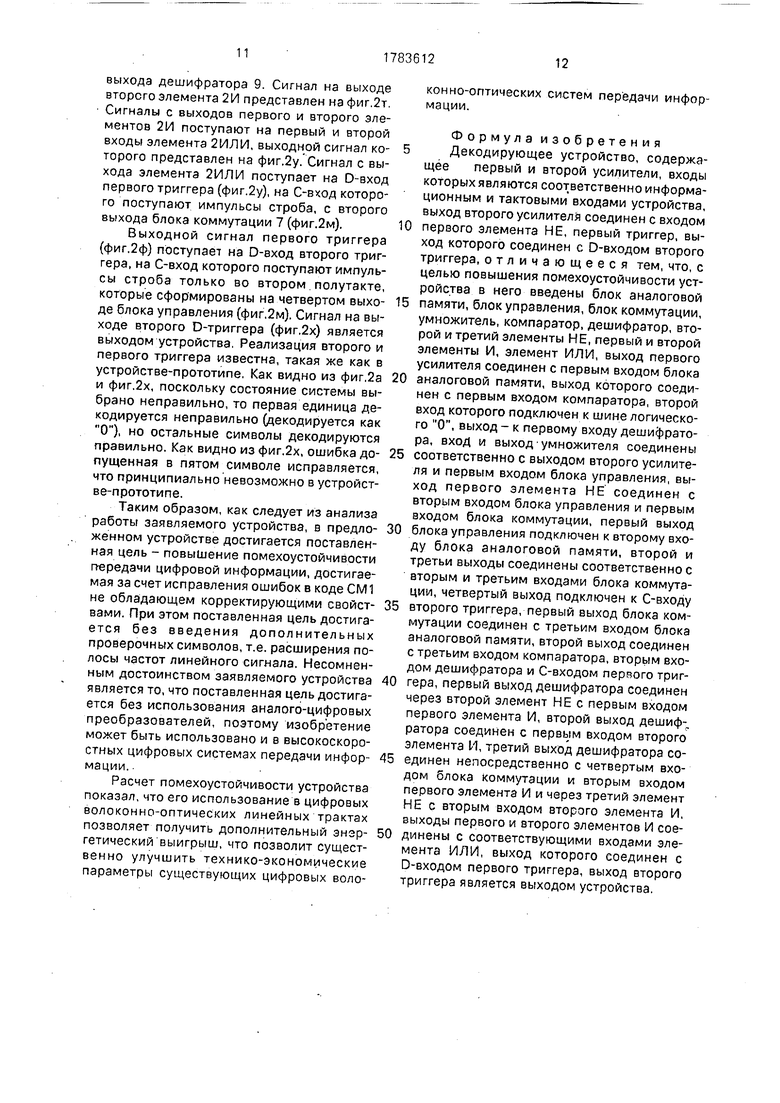

На фмг.1 приведена структурная схема заявляемого устройства; на фиг.2 приведены эпюры напряжений поясняющие работу заявляемого устройства; на фиг.З-эпюры напряжений для кода СМ1; на фиг .4 -древовидные диаграммы и диаграмма состояний кодера; на фиг.5 приведено геометрическое представление сигналов для устройства в состояниях (+) и (-); на фиг.б представлены Рж() и Рм(1) как функции отношения сигнал-шум, дБ; на фиг.7 - дополнительный энергетический выигрыш А Е как функция от отношения сигнал-шум, дБ; на фиг.8 - реализация умножителя; на фиг,9 - эпюры напряжений поясняющие работу умножителя; на фиг. 10 - реализация блока управления; на фиг.11 - эпюры напряжений поясняющие работу блока управления; на фиг. 12 - реализация блока аналоговой памяти; на фиг. 13 - реализация блока коммутации; на фиг.14 - эпюры напряжений поясняющие работу блока коммутации; на фиг. 15 - реализация дешифратора; на фиг. 16 - эпюры напряжений поясняющие работу дешифратора.

Декодирующее устройство содержит первый входной усилитель 1 (ВУ1), вход которого является информационным входом устройства, второй входной усилитель 2 (ВУ2), вход которого является тактовым входом устройства, блок аналоговой памяти 3 (БАП), умножитель 4 (УМН), первый элемент НЕ 5, блок управления б (БУ), блок коммутации 7 (БК), компаратор 8 (К), дешифратор 9 (ДШ), второй элемент НЕ 10, третий элемент НЕ 11, первый элемент 2И 12, второй элемент 2И 13, элемент ИЛИ 14, первый триггер 15, второй триггер 16, причем выход первого усилителя 1 соединен с первым входом блока аналоговой памяти 3, выход которого соединен с первым входом компаратора 8, второй вход которого подключен к шине лог. О, выход - к первому входу дешифратора 9, вход и выход умножителя 4 соединены соответственно с выходом второго усилителя 2 и с первым входом блока управления 6, выход первого 5 элемента НЕ соединен со вторым входом блока управления 6 и первым входом блока коммутации 7, первый выход блока управления 6 подключен ко второму входу блока аналоговой памяти 3, второй и третий выходы соединены соответственно с вторым и третьим входами блока коммутации 7, четвертый выход подключей к С-входу второго триггера 16, первый выход блока коммутации 7 соединен с третьим входом блока аналоговой памяти 3, второй выход соединён с третьим входом компаратора 8, со вторым входом дешифра0 тора 9, и С - входом первого триггера 15, первый выход дешифратора 9 соединен через второй 10 элемент НЕ с первым входом первого 12 элемента И, второй выход дешифратора 9 соединен с первым входом

5 второго 13 элемента И, третий выход дешифратора 9 соединен непосредственно с четвертым входом блока коммутации 7 и вторым входом первого 12 элемента И и через третий 11 элемент НЕ с вторым вхо0 дом второго 13 элемента И, выходы первого 12 и второго 13 элементов И соединены с соответствующими входами элемента ИЛИ 14, выход которого соединен с О-в-ходом первого триггера 15, выход второго триггера

5 16 является выходом устройства.

Устройство работает следующим образом.

Пусть на передающей стороне передавалась комбинация вида 100-11-10101 (см.

0 фиг.2) с тактовой частотой fo. Пусть на входе устройства переданной комбинации соответствует сигнал после усиления, который представлен на фиг.26. Для более наглядного представления процесса исправления

5 ошибки в заявляемом устройстве помеха а линейном тракте выбирается такой, что переданный символ в устройстве-прототипе будет восстановлен с ошибкой, которая исправляется в заявляемом устройстве. Уст0 ройство имеет два состояния работы (+) и (-). Поскольку в начальный момент времени не известно состояние устройства ((+) или (-}), то при включении питания устрой- ство установится в состояние (+), чему бу5 дет соответствовать появление единичного уровня на третьем выходе дешифратора 9 (фиг.2р). Если, допустим, состояние выбрано правильно, то устройство декодирует входной сигнал без ошибок, В случае непра0 вильного выбора, система первую единицу декодирует как ноль, после этого начинает правильное декодирование, Причем можно сказать, что вероятность правильного выбора состояния равна 0,5. Время до прихода

5 первой единицы назовем временем установления режима работы. Для более наглядного представления принципа работы устройства выберем состояние неправильно. Информационный сигнал с канала связи поступает на вход первого входного усилителя 1, где происходит усиление и коррекция входного сигнала, Выходной сигнал первого входного усилителя 1, представленный на фиг.2,б поступает на вход блока аналоговой памяти 3. На вход второго входного усилителя поступает сигнал тактовой частоты.Сигнал на выходе второго

входного усилителя 2 представлен на фиг.2в, Входные усилители служат для усиления и коррекции сигналов до определенной величины необходимой для работы остальных блоков устройства. Сигнал тактовой частоты с выхода второго усилителя 2 (фиг.2в) поступает на умножитель частоты 4, через первый элемент НЕ 5 на второй вход блока управления 6 (фиг.2г) и на третий вход блока коммутации 7. Реализация и эпюры напряжений поясняющие работу умножителя представлены соответственно на фиг.8 и фиг.9. Умножитель служит для получения частоты равной 2fo (см. фиг.2д). Он состоит из элемента Исключающее ИЛИ, на первый вход которого сигнал поступает прямо (фиг.8а), а на второй через задержку (фиг.Вж). В результате на выходе получается частота равна 2то(фиг.8з). Сигналы с выхода умножителя 4 (фиг.2д) и первого элемента НЕ 5 (фиг,2г) поступают на первый и второй соответственно входы блока управления 6. Блок управления 6 служит для формирования управляющих импульсов необходимых для нормального функционирования устройства. Блок управления формирует: на первом выходе - импульсы сброса блока аналоговой памяти (фиг.2е); на втором выходе - импульсы управления блоком аналоговой памяти (фиг.2ж); на третьем выходе - импульсы строба (фиг.2з) и на четвертом выходе - импульсы необходимые для работы второго триггера 16 (фиг.2и), Реализация и эпюры напряжений, поясняющие работу блока управления 6, представлены на фиг.10 и фиг.11 соответственно. Сигнал управления блоком аналоговой памяти (фиг.2ж) и строба (фиг.2з) с второго и третьего выходов блока управления поступает на первый и второй входы блока коммутации 7, соответственно. Блок коммутации 7, в зависимости от состояния системы ((+) или ()). информация о которой из третьего выхода дешифратора 9 поступает на четвертый вход (фиг.2р) блока коммутации 7, пропускает импульсы управления блоком аналоговой памяти (фиг.2л) и строба (фиг.2м) или в первом или во втором полутактах, в зависимости от того в каком состоянии находится система. Как видно из фиг 2л и фиг.2м, если система находилась в состоянии (+), то блок коммутации 7 пропускает импульсы управления блоком аналоговой памяти и импульсы строба во втором полутакте, а если в состоянии (-), то - в первом. Реализация и эпюры напряжений, поясняющие принцип работы блока коммутации 7, представлены 5 на фиг.13 и фиг,14 соответственно. Импульсы управления блоком аналоговой памяти (фиг.2е) с выхода блока управления 6 поступают соответственно на первый и второй управляющие входы блока аналоговой па0 мяти 3. Блок аналоговой памяти 3 служит для запоминания значений входного сигнала, поступающих с выхода первого входного усилителя 1 (фиг.2б), по сигналу на первом управляющему входе (фиг.2л). Запомненная

5 информация хранится в блоке аналоговой памяти, до его сравнения с нулевым уровнем в компараторе 8 до конца этого полутакта. В конце каждого полутакта значения запомненного напряжения в блоке аналого0 вой памяти 3 сбрасываются импульсами сброса (фиг.2е) поступающими на второй управляющий вход блока аналоговой памяти 3. Реализация блока аналоговой памяти 3 представлена на фиг. 12.

5 Сигнал с выхода блока аналоговой памяти 3 (фиг.2к) поступает на компаратор 8, где по сигналу строба (фиг.2м) значение на входе компаратора 8 сравнивается с нулевым порогом. Сигнал с выхода компаратора

0 (фиг,2н) поступает на первый вход дешифратора, на второй вход которого с второго выхода блока коммутации 7 поступают импульсы строба (фиг.2м). Дешифратор служит для дешифрации сигнала, а также уп5 равляет режимами работы всего устройства (т.е. в каком состоянии находится система; в (+) или (-)). Причем в начальный момент, при включении устройства дешифратор автоматически устанавливается в состояние

0 (+). С приходом каждой единицы на вход устройства дешифратор меняет свое состояние и декодирование в следующем такте осуществляется в этом состоянии. Сигналы на первом, втором и третьем выходах пред5 ставлены на фиг.2о, фиг.2п, фиг.2р, соответственно. Реализация и эпюры напряжений подробно поясняющие принцип работы дешифратора 9 представлены на фиг.15 и фиг.16 соответственно. Сигнал с первого

0 выхода (фиг.2о) дешифратора 9 через второй элемент НЕ 10 поступает на первый вход первого элемента 2И, на второй вход которого поступает сигнал с третьего выхода (фиг.2р) дешифратора 9. Сигнал на выходе

5 первого элемента 2И 12 представлен на фиг.2с. Сигнал с второго выхода (фиг.2п) дешифратора 9 поступает на первый вход второго элемента 2И 13 на второй вход которого поступают инвертированные третьим элементом НЕ импульсы с третьего

выхода дешифратора 9. Сигнал на выходе второго элемента 2И представлен на фиг.2т Сигналы с выходов первого и второго элементов 2И поступают на первый и второй входы элемента 2ИЛИ, выходной сигнал которого представлен на фиг.2у. Сигнал с выхода элемента 2ИЛИ поступает на D-вход первого триггера (фиг.2у), на С-вход которого поступают импульсы строба, с второго выхода блока коммутации 7 (фиг.2м).

Выходной сигнал первого триггера (фиг,2ф) поступает на D-вход второго триггера, на С-вход которого поступают импульсы строба только во втором полутакте, которые сформированы на четвертом выходе блока управления (фиг.2м), Сигнал на выходе второго D-триггера (фиг,2х) является выходом устройства. Реализация второго и первого триггера известна, такая же как в устройстве-прототипе, Как видно из фиг.2а и фиг.2х, поскольку состояние системы выбрано неправильно, то первая единица декодируется неправильно (декодируется как О), но остальные символы декодируются правильно. Как видно из фиг.2х, ошибка допущенная в пятом символе исправляется, что принципиально невозможно в устройстве-прототипе.

Таким образом, как следует из анализа работы заявляемого устройства, в предложенном устройстве достигается поставленная цель - повышение помехоустойчивости передачи цифровой информации, достигаемая за счет исправления ошибок в коде СМ1 не обладающем корректирующими свойствами. При этом поставленная цель достигается без введения дополнительных проверочных символов, т.е. расширения полосы частот линейного сигнала. Несомненным достоинством заявляемого устройства является то, что поставленная цель достигается без использования аналого-цифровых преобразователей, поэтому изобретение может быть использовано и в высокоскоростных цифровых системах передачи информации.

Расчет помехоустойчивости устройства показал, что его использование в цифровых волоконно-оптических линейных трактах позволяет получить дополнительный энергетический выигрыш, что позволит существенно улучшить технико-экономические параметры существующих цифровых волоконно-оптических систем передачи информации.

Формула изобретения

Декодирующее устройство, содержащее первый и второй усилители, входы которых являются соответственно информационным и тактовыми входами устройства, выход второго усилителя соединен с входом

первого элемента НЕ, первый триггер, выход которого соединен с D-входом второго триггера, отличающееся тем, что, с целью повышения помехоустойчивости устройства в него введены блок аналоговой

памяти, блок управления, блок коммутации, умножитель, компаратор, дешифратор, второй и третий элементы НЕ, первый и второй элементы И, элемент ИЛИ, выход первого усилителя соединен с первым входом блока

аналоговой памяти, выход которого соединен с первым входом компаратора, второй вход которого подключен к шине логического О, выход - к первому входу дешифратора, вход и выход умножителя соединены

соответственно с выходом второго усилителя и первым входом блока управления, выход первого элемента НЕ соединен с вторым входом блока управления и первым входом блока коммутации, первый выход

блока управления подключен к второму входу блока аналоговой памяти, второй и третьи выходы соединены соответственно с вторым и третьим входами блока коммутации, четвертый выход подключен к С-входу

второго триггера, первый выход блока коммутации соединен с третьим входом блока аналоговой памяти, второй выход соединен с третьим входом компаратора, вторым входом дешифратора и С-входом первого триггера, первый выход дешифратора соединен через второй элемент НЕ с первым входом первого элемента И, второй выход дешиф-„ ратора соединен с первым входом второго элемента И, третий выход дешифратора соединен непосредственно с четвертым входом блока коммутации и вторым входом первого элемента И и через третий элемент НЕ с вторым входом второго элемента И, выходы первого и второго элементов И соединены с соответствующими входами элемента ИЛИ, выход которого соединен с D-входом первого триггера, выход второго триггера является выходом устройства.

С

Фиг, 3

Состоянла (+)

М (- Л

Состояние (-)

- и

it.fi

V

Л//А М

Л//Г

№Г

фис1 4а

Фиг. -46

m

Q. on

oS 3

-i

0-. .

N Ч

€ P

&

L

i

5

enjk о

M

i Я

t i

S1

. v

4

f

t« I

&

a

/

ГУ Г Г Г Г /Л /Я f

г. J

А XV А А ПА

1

1ПППППППППППППГ., .

чг. ГО

Г

4 -

J

jIT U U ;Г -U IU 11ТТТП 1 ТПГ1П1Г1ПГ1Г

iГгГiiч

JULJLJL LJUUULOJLiau

У У -О U ill U ;U U ill II1U 0 :ll И Jin JUIJUUUUUUULJULJUUUL

JLJUUUUUUUUUU.UUUU

Я дио

ИП -mt-/

П J

ж

9 &

Т

Zt9C8iL

ШС9а

| Заявка № 4194706/24 положит, решение от 28.8.87 | |||

| Monolithic integrated CMI coder and decoder for Gigabit optical links, Electronics letters, and 2nd January 1982, v | |||

| Машина для добывания торфа и т.п. | 1922 |

|

SU22A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1992-12-23—Публикация

1990-08-09—Подача