(5) УСТРОЙСТВО ДЛЯ СИНХРОНИЗАЦИИ ЧАСОВ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для синхронизации часов | 1977 |

|

SU632981A1 |

| Устройство для синхронизации часов | 1983 |

|

SU1170419A1 |

| Устройство для синхронизации часов | 1978 |

|

SU732793A2 |

| Цифровой частотомер | 1981 |

|

SU1068834A1 |

| Формирователь импульсов | 1985 |

|

SU1257813A1 |

| Устройство для анализа формы однократных электрических импульсов | 1983 |

|

SU1095103A1 |

| Устройство для передачи временной информации | 1986 |

|

SU1446639A1 |

| Программное устройство для фиксации и документирования времени | 1989 |

|

SU1677691A1 |

| Способ магнитной записи асинхронных потоков цифровой информации и устройство для его осуществления | 1990 |

|

SU1788520A1 |

| Умножитель частоты следования импульсов | 1986 |

|

SU1403356A1 |

I

Изобретение относится к приборостроению и предназначено для использования в электронных часах с синхронизацией.

Известны часы с синхронизацией 113Однако известные устройства не обеспечивают надежной синхронизации.

Наиболее близким к предлагаемому является устройство для синхронизации часов, содержащее последовательно соединенные кварцевый генератор, делитель частоты, выполненный в виде многоразрядного двоичного счетчика, и дешифратор, первый выход которого соединен со входом триггера, выходы которого соединены с первыми входами первого и второго элементов И, вторые входы которых соответственно подключены ко входу внешней синхронизации и к выходу первого элемента ИЛИ, при этом выходы элементов И соединены со входами второго элемента ИЛИ,

Недостаток данного устройства состоит в недостаточно высокой надежности, так как при пропадании импульсов внешней синхронизации на выходе устройства формируются счетные импульсы, неидентичные импульсам внешней синхронизации. Длительность сформированных импульсов равняется времени обнуления делителя частоты и может быть недостаточной для надежной работы синхронизируемых часов.

Цель изобретения - стабилизация длительности счетных импульсов на выходе устройства.

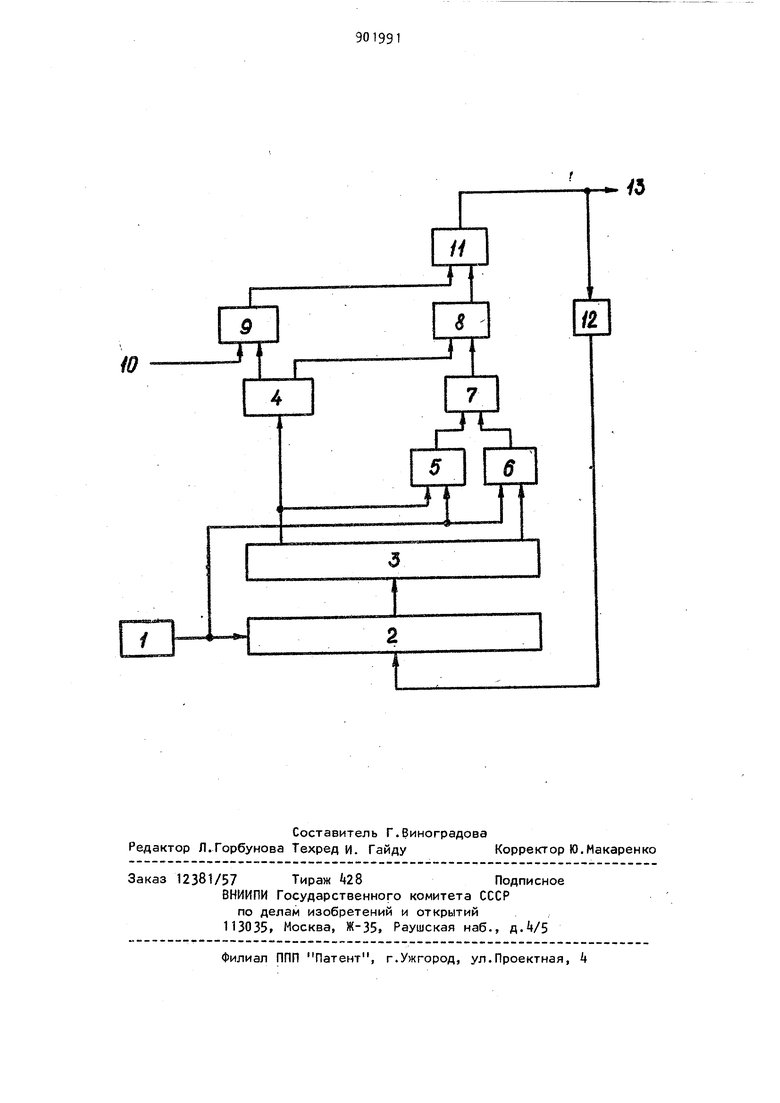

Поставленная цель достигается тем, что в устройство, содержащее последовательно соединенные кварцевый генератор, делитель частоты, выполненный в виде многоразрядного двоичного счетчика, и дешифратор, первый выход которого соединен со входом триггера, выходы которого соединены с первыми входами первого и второго элементов И, вторые входы которых соответственно.подключены . ко входу внешней синхронизации и к 3 9 выходу первого элемента ИЛИ, при этом выходы элементов И соединены со входами второго элемента ИЛИ, вве дены третий и четвертый элементы И и элемент задержки, причем первые вход третьего и четвертого элементов И соединены с выходом кварцевого генератора, вторые входы соединены соответственно с первым и вторым выходам дешифратора, а их выходы подключены ко входам первого элемента ИЛИ, а элемент задержки соединен с шиной обнуления делителя частоты и выходом второго элемента ИЛИ. На чертеже представлена структурная схема устройства для синхронизации часов. Устройство содержит кварцевый генератор 1, подключенный к делители) 2 частоты, дешифратор 3 включенный на выходе делителя 2 частоты, первый выход дешифратора 3 соединен со входом триггера Ц и вторым входом элемента И 5 а второй выход дешифратора - со вторым входом элемента И 6. Первые входы элементов И 5 и 6 , соединены с выходом кварцевого генератс эа 1, а выходы - со входами элемента ИЛИ 7 выход которого соедииен со вторым входом элемента И 8, к первому входу которого подключен вто рой выход триггера k. Первый выход триггера Ц соединен с первым входом элемента И 9 второй вход которого соединен со входом внешней 10 синхро низации. Выходы элементов И 8 и 9 сое динены с входами элемента ИЛИ 11, выход которого соединен со входом элемента 12 задержки и одновременно является выходом 13 устройства. Выход элемента 12 задержки соединен с шинси обнуления делителя 2 частоты. Дешифрационные числа на первом и втором выходах дешифратора 3 выбираются из соотношений N, (HG); Nj , где f - частота кварцевого генератора 1; F - частота следования импульсов внешней синхронизации; относительная погрешность частоты кварцевого генератора 1 . Устройство работает следующим образом. В исходном состоянии делитель 2 частоты и триггер k обнулены. При 14 пуске устройства делитель 2 частоты получает разрешение на счет (цепь пуска не показана). Кварцевый генератор 1 формирует импульсы по длительности равные импульсам внешней синхронизации, поступающим на вход 10. Частота следования импульсов на выходе делителя 2 частоты точно равна частоте следования импульсов внешней синхронизации, так как обнуление делителя частоты производится только импульсами внешней синхронизации, поскольку цепь обнуления внутренними сигналами с первого и второго выходов дешифратора 3 закрыта (закрыт элемент И 8) Для подключения цепи обнуления внутренними сигналами необходимо переключение триггера Ц, управляющего элементами И 8 и И 9 которые переключают цепи обнуления делителя 2. Триггер переключается сигналом с первого выхода дешифратора 3- Этот сигнал формируется только в случае пропадания импульсов внешней синхронизации, так как при наличии импульсов внешней синхронизации, благодаря выбору дешифрационных чисел на выходах дешифратора 3 делитель 2 обнуляется раньше, чем он наберет код, соответствующий первому дешифрационному числу. Таким образом, в случае пропадания импульсов внешней синхронизации на вход 10 делитель 2 в очередной раз не обнулен, формируется сигнал на первом выходе дешифратора 3 и происходит переключение триггера i. Элемент И 9 закрывается, элемент И 8 открывается, элемент И 5 си«-налом с первого выхода дешифратора 3 открыт по второму входу. Делитель 2 частоты, выполненный в виде многоразрядного двоичного счетчика, изменяет свое состояние по задним фронтам импульсов, поступающих с выхода кварцевого генератора 1. Поэтому сигнал на первом выходе дешифратора 3 созраняется до прихода и окончания очередного импульса с выхода кварцевого генератора 1. Этот импульс проходит через открытые элементы И 5, ИЛИ 7, И 8, ИЛИ 11, поступает на выход 13 устройства и Одновременно через элемент задержки 12 на шину обнуления делителя 2 частоты, приводя его в исходное состояние. Для того, чтобы делитель 2 не обнулился раньше полного прохождения импульса на выход 13 уст59

ройства, время задержки элемента 12 должно удовлетворять условию

U U )

где tj - время задержки элемента 12; - длительность импульсов кварцевого генератора; Тц - период следования импульсов

кварцевого генератора 1. В дальнейшем делитель 2 обнуляется импульсами с выхода элемента И 6,формируемыми при одновременном поступлении на его входь - импульса с выхода кварцевого генератора 1 и сигнала со второго выхода дешифратора 3. Устройство выдает счетные импульсы на собственной частоте, равной F(1±S), т.е. переключится в режим внутренней синхронизации. Время переключения при соответствующем выборе числа N на первом выходе дешифратора 3 должно составлять величину не менее G/F.

Предлагаемое устройство благодаря введению третьего и четвертого элементов И, стробируемых по первым импульсами с выхода кварцевого генератора, л элемента заде{Я1Ски который не дает делителю частоты обну литься до полного прохождения импульсов на выход устройства обеспечивает на выходе устройства независимо от режима синхронизации последовательность счетных импульсов, стабильных не только по частоте, но и по длительности.

16

Формула изобретения Устройство для синхронизации часов, содержащее последовательно соединенные кварцевый генератор, делитель частоты, выполненный в виде многоразрядного двоичного счетчика, и дешифратор, первый выход которого соединен со входом триггера, выходы которого соединены с первыми входами первого и второго элементов Иу вторые входа которых соответственно подключены ко входу внешней синхронизации и к выходу первого элемента ИЛИ, при этом выходы элементов И содинены со входами второго элемента ИЛИ, отличающееся тем, что, с целью стабклизации длительности счетных импульсов на-выходе устройства, 8 него введены третий и четвертый элементы Н и элемент задержки, причем первые входы третьего и четвертого элементов И- соедине1«1 с выходом кварцевого генератор вторые входы соединены соответственно с первым и вторым выходами дешифратсч а, а их выходы подключены ко входам левого элемента ИЛИ, а элемент заде(нкки соединен с шиной обнуления делителя частоты и выходом второго элемента ИЛИ.

Ист омни IO1 информации, . гц инятые во внимание при экспертизе

/3

Авторы

Даты

1982-01-30—Публикация

1980-06-06—Подача