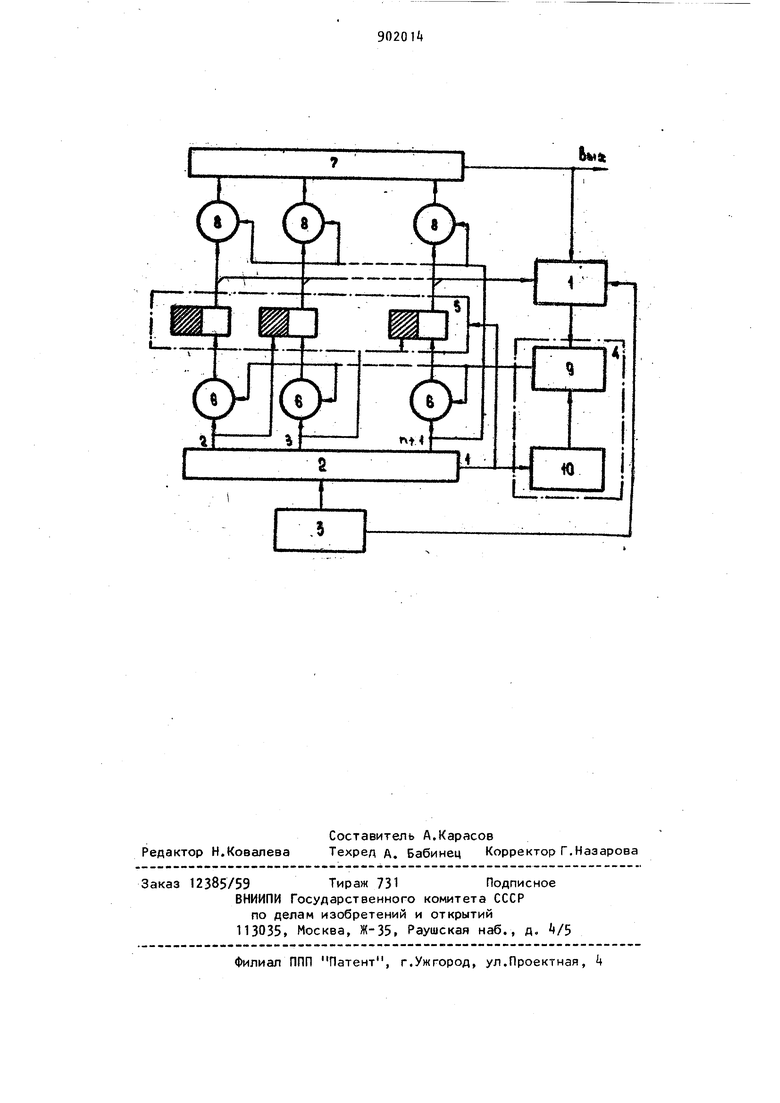

тактовых импульсов, первый выход которого соединен со входом сдвиг регистра сдвига, разрядные выходы ко торого, кроме первого, соединены с первы1 «1 входами соответствующих элементов И первой группы, вторые входы которых объединены между собой и подключены к выходу управляемого датчика случайных чисел, первый вход которого соединен с выходом блока памяти, первый вход которого объединен с выходом генератора и подключен к выходу Первого регистра памяти, разрядные входы которого соединены с выходами соответствующих элементов И второй fpyппы, первые входы которого объединены между собой и подключены к выходу последнего разряда регистра сдвига, введен второй регистр памяти, разрядные выходы которого соединены со вторыг«4 входами соответствующих элементов И второй группы и со вторым входом блока памяти, третий вход которого соединен со вторым выходом генератора тактовых импульсов, выход первого разряда регистра сдвига соединен со вторым входом управляемого датчика случайных чисел и со входом сброс второго регистра памяти, прякые разряд 1е входы которого соединены с выходами соответствустчих элементов И первой группы, а инверсные разрядные входы второго регистра памяти, начиная со второго, соединены с соответствующими разрядными, выходами регистра сдвига. На чертеже приведена блок-схема генератора. Генератор однородного марковского процесса содержит блок 1 памяти, регистр 2 сдвига, генератор 3 тактовых импульсов, первый выход которого подключен ко входу регистра сдвига, а второй - к входу считывания блока памяти, управляемый датчик k случайны; чисел, первый вход которого подключен к выходу блока памяти, второй регистр 5 памяти, установочный вход которого соединен со вторым входом управляемого датчика случайных чисел .и с первым выходом регистра сдвига, остальные п выходов которого подключены к единичным входам второго регистра памяти непосредственно и к нулевым входам этого же регистра через элементы 6 И, общие входы которых соединены с выходом управляемого датчика случайных чисел, первый регистр 7 памяти, входы которого подключены к выходам второго регистра памяти через элементы 8 И, общие входы которых соединены с последним выходом регистра сдвига. Причем выходы регистра 5 образуют младшие разряды адреса блока памяти, а выходы регистра - старшие разряды и подключены к выходу генератора. Кроме того, управляемый датчик случайных чисел состоит из блока 9 сравнения и генератора 10 случайных чисел, равномерно распределенных на интервале 0,1. Генератор работает следующим образом. Генератор 3 формирует на своих выходах сдвинутые по фазе тактрвые импульсы. В начале цикла розыгрыша очередного состояния импульс с первого выхода генератора 3 проходит на первый выход регистра 2 сдвига, устанавливает регистр 5 в состояние О (записывает единицу в первый разряд и нули во все остальные разряды) и включает генератор 10, который формирует случайное равномерно распределенное на интервале 0,1 число V. Импульс со второго выхода генератора 3 возбуждает ячейку блока 1 памяти, номер страницы которой задает регистр 7, а адрес внутри страницы - регистр 5. Блок 9 сравнения вычитает содержимое этсй ячейки из числа V и вырабатывает разрешаюи ий си гнал для элементов 6 И, если разность отрицательная. Следугаций импульс с первого выхода генератора 3 проходит через второй выход регистра сдвига или обнуляет первый разряд 5, или оставляет его без изменения. Этот же импульс записывает единицу во второй разряд. Второй импульс со второго выхода генератора 3 вновь возбуждает соответствующую ячейку блока памяти и подготавливает условия для определения значения второго разряда. Отыскание значений разрядов продолжается до момента появления импульса на последнем (п+1) выходе распределителя. Этот импульс завершает фо|3мирование младшего разряда и одновременно переписывает содержимое регистра 5 в регистр 7, определяя тем самым очередное состояние марковской цепи.

59020

Применение регистра 5 вместо сумматора, регистра и элементов ИЛИ, а также изменение схемы включения датчика 4 случайных чисел сокращает количество оборудования и связей между s функциональными элементами, снижает требования к быстродействию генератора 10 равномерно распределенных чисел и упрощает расчет содержимого ячеек блока памяти.10

Формула изобретения

Генератор однородного марковского 15 процесса, содержащий генератор тактовых импульсов, первый выход которого соединен со входом сдвиг регистра сдвига разрядные выходы которого, кроме первого, соединены с первыми 20 входами соответствующих элементов И первой групгы, вторые входы которых объединены между собой и подключены к выходу управляемого датчика случайных чисел, первый вход которого 25 соединен с выходом блока памяти, первый вход которого объединен с выходом генератора и подключен к выходу первого |)егистра памяти, разрядные входы которого соединены с выходами со- зо ответствующих элементов И второй групЙ6.

пы, первые входы которых объединены между собой и подключены к выходу последнего разряда регистра сдвига, отличающийся тем, что, с целью упрощения генератора, он содержит второй регистр памяти, разрядные выходы которого соединены со вторыми входами соответствующих элементов И второй группы и со вторым входом блока памяти, третий вход которого соединен со вторым выходом генератора тактовых импульсов, выход первого разряда регистра сдвига соединен со вторым входом управляемого датчика случайных чисел и со входом сброс второго регистра памяти, пряWiie разрядные вхрды которого соединены с выходами соответствующих элементов И первой группы, а инверсные разрядные входы второго регистра памяти, начиная со второго, соединены с соответствующими разрядными выходами регистра сдвига.

Источники информации, принятые во внимание при экспертизе

1.Авторское свидетельство СССР V , кл. G 06 G 7/26, 1970.

2.Авторское свидетельство СССР № , кл. G Об F 1/02, 197 (прототип). ( имя

| название | год | авторы | номер документа |

|---|---|---|---|

| Имитатор дискретного канала связи | 1989 |

|

SU1755292A1 |

| Генератор случайного Марковского процесса | 1982 |

|

SU1070548A1 |

| Имитатор дискретного канала связи | 1984 |

|

SU1223246A2 |

| Генератор случайных чисел | 1980 |

|

SU922738A1 |

| Генератор случайных чисел | 1981 |

|

SU1008738A1 |

| Генератор случайного марковского процесса | 1985 |

|

SU1278842A1 |

| ЦИФРОВОЙ ИМИТАТОР СЛУЧАЙНЫХ СИГНАЛОВ | 2019 |

|

RU2718417C1 |

| Устройство для моделирования вероятностного графа | 1982 |

|

SU1119023A1 |

| Цифровой имитатор случайных сигналов | 2019 |

|

RU2722001C1 |

| Имитатор дискретного канала связи | 1981 |

|

SU964651A2 |

Авторы

Даты

1982-01-30—Публикация

1980-06-04—Подача