(ЗЮ ИМИТАТОР ДИСКРЕТНОГО КАНАЛА СВЯЗИ

| название | год | авторы | номер документа |

|---|---|---|---|

| Имитатор дискретного канала связи | 1980 |

|

SU951318A2 |

| Имитатор дискретного канала связи с ошибками синхронизации | 1980 |

|

SU934479A2 |

| Имитатор дискретных каналов связи | 1979 |

|

SU842827A1 |

| УСТРОЙСТВО ДЛЯ МОДЕЛИРОВАНИЯ СИСТЕМЫ СВЯЗИ | 2005 |

|

RU2286597C1 |

| Имитатор дискретного канала связи | 1982 |

|

SU1075267A2 |

| Имитатор дискретного канала связи | 1989 |

|

SU1755293A1 |

| Имитатор дискретного канала связи | 1984 |

|

SU1223246A2 |

| Цифровой интегратор с контролем | 1975 |

|

SU540269A1 |

| Имитатор дискретного канала связи | 1989 |

|

SU1755292A1 |

| Устройство для контроля сбоев псевдослучайного испытательного сигнала | 1983 |

|

SU1172056A1 |

1

Изобретение относится к радиотехнике и может быть использовано для статистического анализа помехозащищенности систем передачи дискретных данных.

По основному авт, св. № 807312 известен имитатор дискретного канала связи, содержащий сумматор по модулю два, выход и первый вход которого является соответственно выходом и первым входом имитатора, блок синхронизации, первый вход которого является вторым входом имитатора, а выход блока синхронизации соединен с входом генератора марковской последовательности, первый выход которого соединен с вторым входом блока синхронизации и входом датчика случайных чисел, блок промежуточной памяти, пороговый сумматор и элемент И, выход которого соединен с вторым входом сумматора по модулю два, а первый и второй входы элемента И подключены соответственно к выходу порогового сумматора и второму выходу генератора марковской последовательности, третий выход которого через блок промежуточной памяти соединен с первым входом порогового сумматора, второй вход которого подключен к выходу датЧика Случайных чисел tl .

Недостатком известного имитатора является то, что он имитирует только ошибки трансформации и не учитывает

10 краевые ошибки, которые проявляются в смещении фронтов переданного символа, что снижает достоверность моделирования дискретного канала.

Цель изобретения - повышение досто15верности моделирования канала связи.

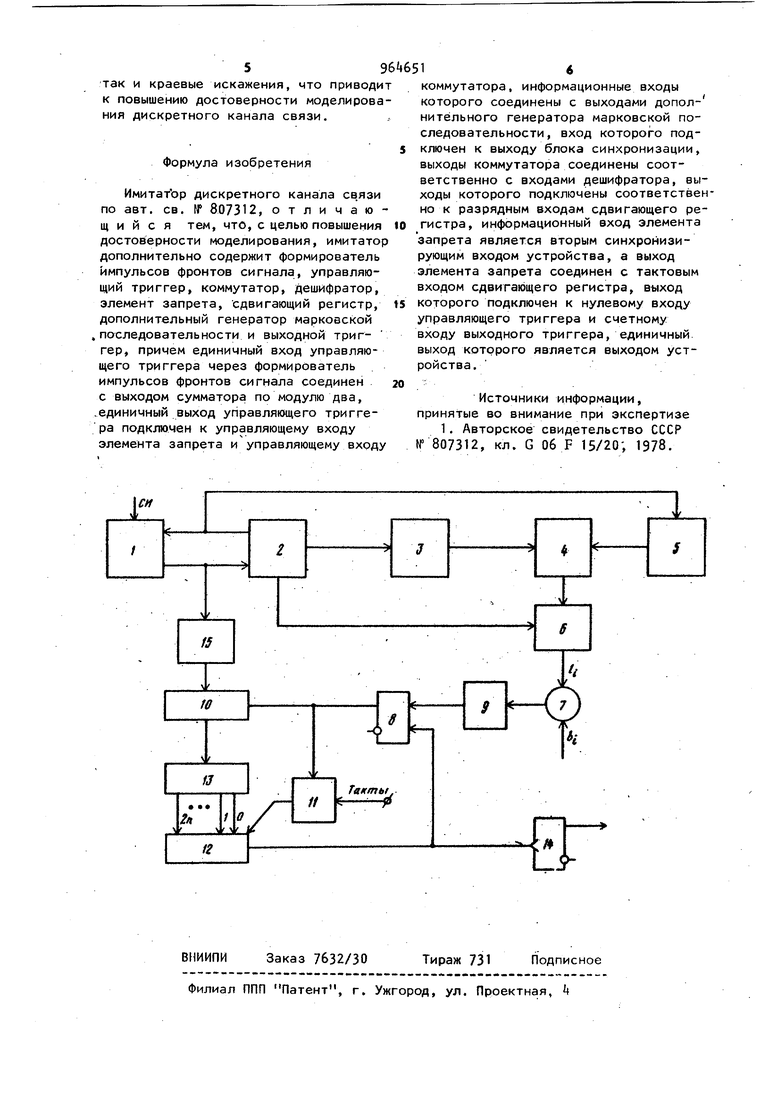

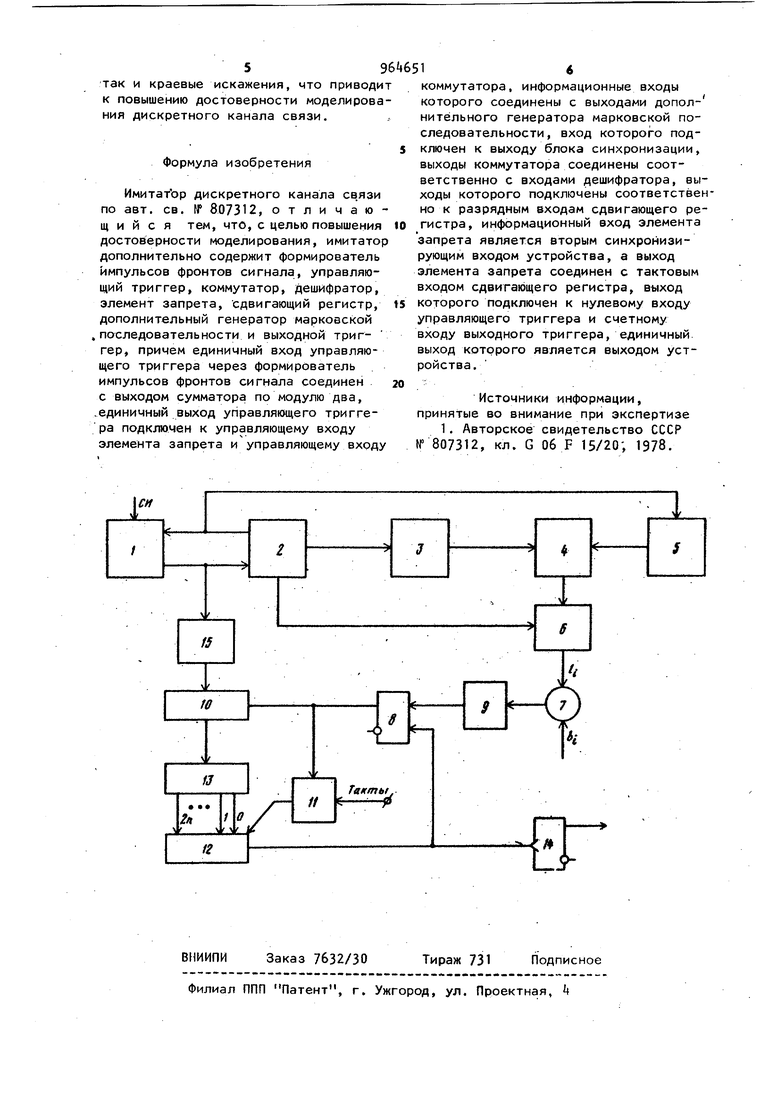

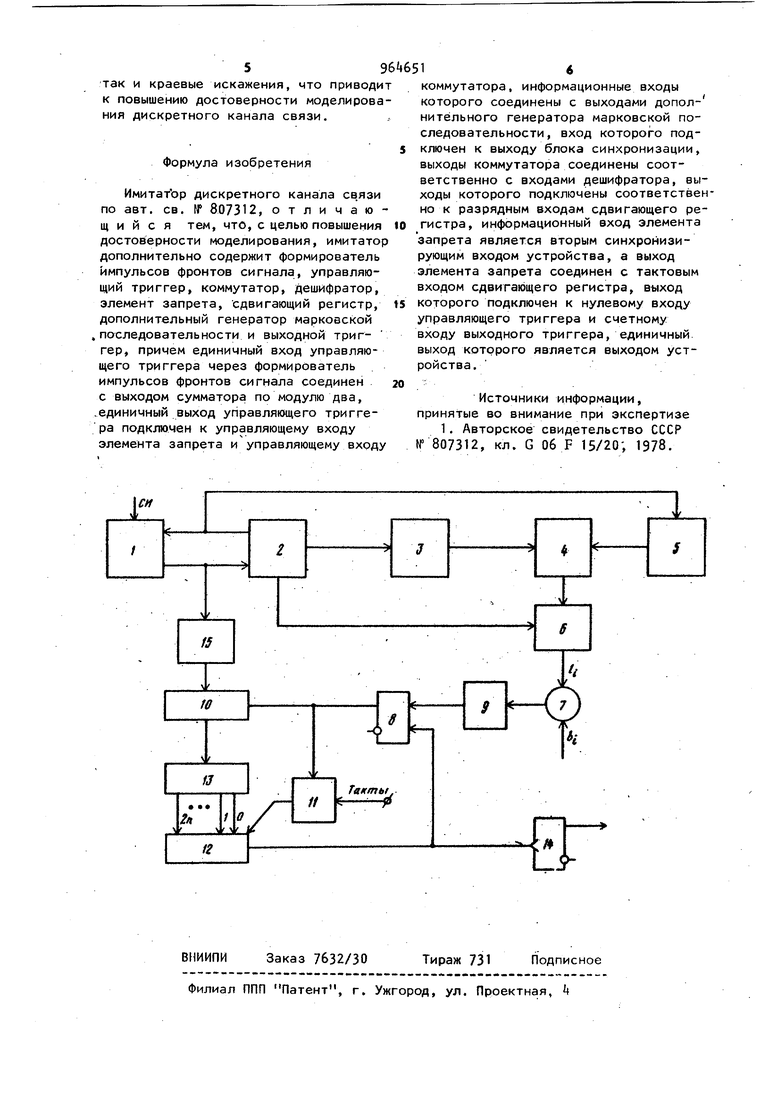

Цель достигается тем, что в имитатор дискретного канала связи дополнительно введены формирователь импульсов фронтов сигнала, управляющий триг20гер, коммутатор, дешифратор, элемент :3апрета, сдвигающий регистр, дополнительный генератор марковской последова:тельности и выходной триггер, единичный вход управляющего триггера через формирователь импульсов фронтов сигналов соединен с выходом сумматора по модулю два, единичный выход управляющего триггера подключен к управляющему входу элемента запрета и управляющему входу коммутатора, информационные входы которого соединены с выходами дополнительного генератора марковской последовательности, вход которого подключен к выходу блока синхронизации, выходы коммутатора соединены соответственно с входами дешифратора, выходы которого подключены соответственно к разрядным входам сдвигающегося регистра, информационный вход элемента запрета является вторым синхронизирующим входом устройства, а выход элемента запрета соединен с тактовым входом сдвигающего регистра, выход которого подключен к нулевому входу управляющего три гера и счетному входу выходного три1- гера, единичный выход которого являет ся выходом устройства. На чертеже приведена структурная схема устройства. Имитатор дискретного канала связи содержит блок 1 синхронизации, генератор 2 марковской последовательности блок 3 промежуточной памяти, порого вый сумматор k, датчик 5 случайных чисел, элемент И 6, сумматор 7 по мо дулю два, управляющий триггер 8, фор миррватель 9 импульсов фронтов сигна ла, коммутатор 10, элемент 11 запрет сдвигающий регистр 12, дешифратор 13 выходной триггер 1, выход которого является выходом устройства, и до- полнительный генератор 15 марковской последовательности. Устройство работает следующим образом. Внешний синхроимпульс запускает блок 1, который вырабатывает сигнал, запускающий генераторы 2 и 15 последовательности. На первом такте работы генератора 2 на втором его выходе появляется сигнал, который опрашивае элемент И 6. Поскольку на входы поро гового сумматора ничего не подавалось, на входе элемента И 6 будет низкий уровень, и на вход сумматора по модулю два сигнал не поступит. После окончания цикла поиска на выхо дах генераторов 2 и 15 появляются коды состояний цепи Маркова, причем код на выходе генератора 15 определяет величину смещения фронта, а код 9 14 на выходе генератора 2 задает адрес ячейки блока 3 памяти, в которой хранится соответствующая условная вероятность ошибки трансформации. Одновременно на третьем выходе генератора второй марковской последовательности появляется сигнал, который подготавливает блок 1 к новому циклу и опрашивает датчик 5 случайных чисел, который вырабатывает случайное равновероятно распределенное число. Это число поступает на первый вход порогового суматора 4, на второй вход которого поступает из блока 3 памяти соответствующая условная вероятность ошибки. Сигнал на выходе порогового суммат,вра k появляется в том случае, если сумма .-слагаемых больше единицы. Таким образом, если выполнились все условия, на входе элемента И 6 появляется единица. С.приходом следующего импульса снова запускаются генераторы 2 и 15, и на втором такте работы опрашивается элемент И 6. В результате на выходе элемента И 6 появляется сигнал ошибки, который поступает на вход сумматора 7 по модулю два, на выходе которого получится смесь информационных символов В с ошибками трансформации . Если в результате суммирования на вход формирователя 9 фронтов поступает сигнал, с выхода формирователя 9 фронтов триггер , 8 перебрасывается в единичное состояние, поскольку в исходном положении триггеры 8 и 14 находились в нулевом положении. По сигналу с единичного выхода триггера 8 опрашивается коммутатор 10, который пропускает код смещения фронта с генератора 15 на вход дешифратора 13 и с задержкой, необходимой для записи 1 по одному из 2п-разрядов с дешифратора 13 в сдвигающий регистр 12, разрешает подачу тактовых импульсов на сдвигающий вход регистра 12. 1 в п-разряде соответствует несмещенному фронту, в разряде, меньшем п, - смещению влево, в разряде, большем п, смещению вправо. 1, продвигаемая тактовыми импульсами с выхода сдвигающего регистра 12, перебрасывает триггер k в единичное состояние и запрещает подачу тактовых импульсов по нулевому входу триггера 8. По обработке кода для заднего фронта устройство работает аналогично. Использование изобретения позволяет моделировать как ошибки трансформации.

так и краевые искажения, что приводит к повышению достоверности моделирования дискретного канала связи.

Формула изобретения

ИмитатЪр дискретного канала св.язи по авт. св. ff 807312, отличающийся тем, что, с целью повышения Ю достоверности моделирования, имитатор дополнительно содержит формирователь импульсов фронтов сигнала, управляющий триггер, коммутатор, дешифратор, элемент запрета, сдвигающий регистр, ts дополнительный генератор марковской

последовательности и выходной триггер, причем единичный вход управляющего триггера через формирователь импульсов фронтов сигнала соединен 20 с выходом сумматора по модулю два,

единичный выход управляю дего триггера подключен к управляющему входу элемента запрета и управляющему входу

коммутатора, информационные входы которого соединены с выходами дополнитёльного генератора марковской последовательности, вход которого подключен к выходу блока синхронизации, выходы коммутатора соединены соответственно с входами дешифратора, выходы которого подключены соответствено к разрядным входам сдвигающего регистра, информационный вход элемента

запрета является вторым синхронизирующим входом устройства, а выход элемента запрета соединен с тактовым входом сдвигающего регистра, выход которого подключен к нулевому входу управляющего триггера и счетному входу выходного триггера, единичный выход которого является выходом устройства.

Источники информации, принятые во внимание при экспертизе

Авторы

Даты

1982-10-07—Публикация

1981-03-09—Подача