Изобретение относится к радиотехнике и можег быть использовано для анализа помехоустойчивости систем передачи дискретной информации,

Известен имитатор дискретного канала связи, содержащий сумматор по модулю два, блок синхронизации, генератор марковской последовательности, датчик случайных чисел, блок промежуточной памяти, пороговый сумматор и элемент И.

Недостатком известного имитатора является отсутствие возможности моделирования ошибок в несимметричных каналах связи.

Наиболее близким по технической сущности к предлагаемому является имитатор дискретного канала связи, содержащий сумматор по модулю два, выход и первый

вход которого являются соответственно выходом и первым входом имитатора, блок синхронизации, генератор марковской последовательности, датчик случайных чисел, промежуточный блок памяти, пороговый сумматор и элемент И.

Недостатком является отсутствие возможности моделирования дискретных каналов связи со стираниями.

Целью изобретения является расшире ние области применения за счет имитации стирзния символов в дискретных каналах связи.

Поставленная цель достигается тем, что в имитатор дискретного канала связи, содержащий блок синхронизации, генератор марковской последовательности, первый блок памяти, первый пороговый сумматор,

Ю

датчик случайных чисел, первый элемент И, сумматор по модулю два, причем выход блока синхронизации соединен с входом запускагенераторямарковскойпоследовательности, выход синхронизиру- ющих импульсов которого подключен к синхровходу блока синхронизации, вход которого является входом запуска имитатора, выход тактовых импульсов генератора марковской последовательности соединен с тактовым входом датчика случайных чисел, и первым входом первого элемента И, группа информационных выходов генератора марковской последовательности подключена к соответствующей группе адресных вхо- дов первого блока памяти, группа выходов которого соединена с соответствующими информационными входами первой группы первого порогового сумматора, к второй группе информационных входов которого подключена группа соответствующих информационных выходов датчика случайных чисел, выход первого порогового сумматора соединен с вторым входом первого элемента И, выход которого подключен к первому информационному входу сумматора по модулю два, второй информационный вход которого является информационным входом устройства и соединен с управляющим входом первого блока памяти, введены второй блок памяти, второй пороговый сумматор, второй элемент И и ключевой элемент, причем группа информационных выходов генератора марковской последовательности соединен с соответствующей группой ад- ресных входов второго блока памяти, группа выходов которого подключена к первой группе входов второго порогового сумматора, к второй группе входов которого подключена группа выходов датчика случайных чисел, выходы первого и второго пороговых сумматоров и выход тактовых импульсов генератора марковской последовательности подключены соответственно к первому, второму и третьему входам второго элемента И, выход которого соединен с управляющим входом ключевого элемента, информационных вход которого подключен к выходу сумматора по модулю два, выход ключевого элемента является выходом устройства, ин- формационный вход устройства соединен с управляющим входом второго блока памяти.

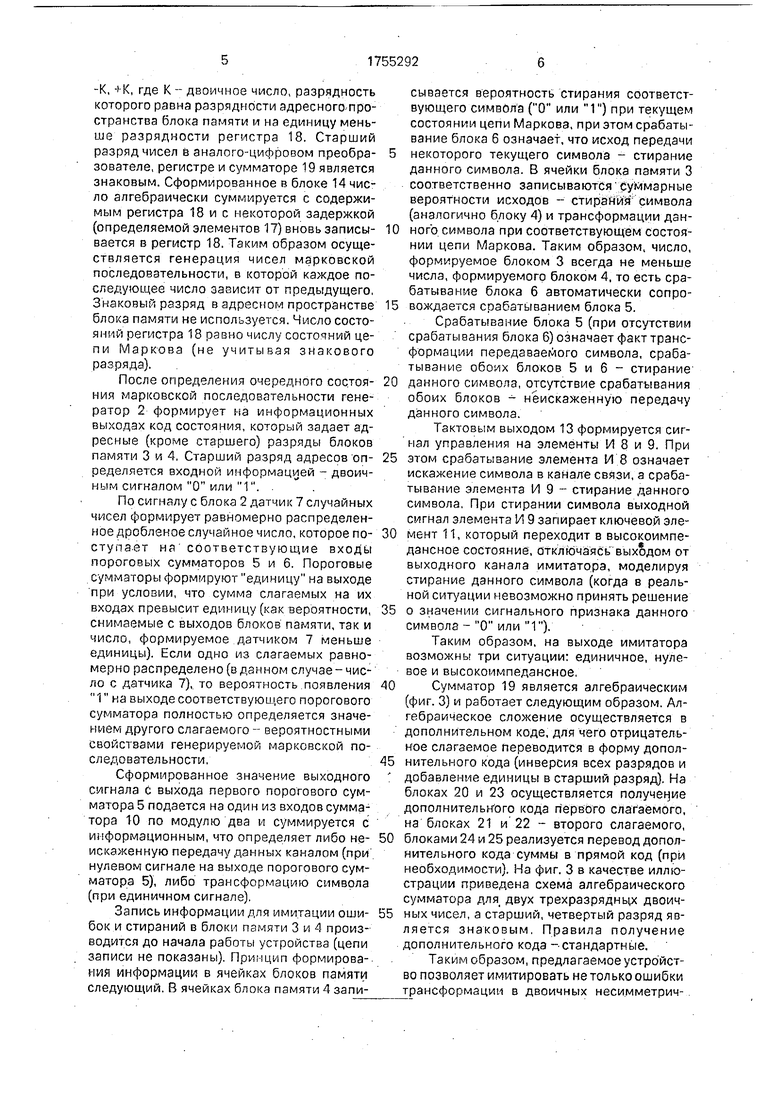

Кроме того, генератор марковской последовательности содержит регистр, сум- матър, генератор тактовых импульсов, генератор случайного сигнала, аналого- цифровой преобразователь и элемент задержки, группа выходов регистра, кроме старшего разряда, является группой информационных выходов генератора, выходы регистра подключены к первой группе информационных входов сумматора, к второй группе информационных входов которого подключена группа выходов аналого-цифрового преобразователя, группа выходов сумматора соединена с группой входов регистра, выход генератора случайного сигнала подключен к информационному входу аналого-цифрового преобразователя, вход синхронизации которого соединен с входом элемента задержки и является входом синхронизации генератора марковской последовательности выход генератора тактовых импульсов подключен к тактовому входу аналого-цифрового преобразователя и является выходом синхронизирующих импульсов генератора марковской последовательности, выход элемента задержки соединен с входом записи регистра и является выходом тактовых импульсов генератора марковской последовательности.

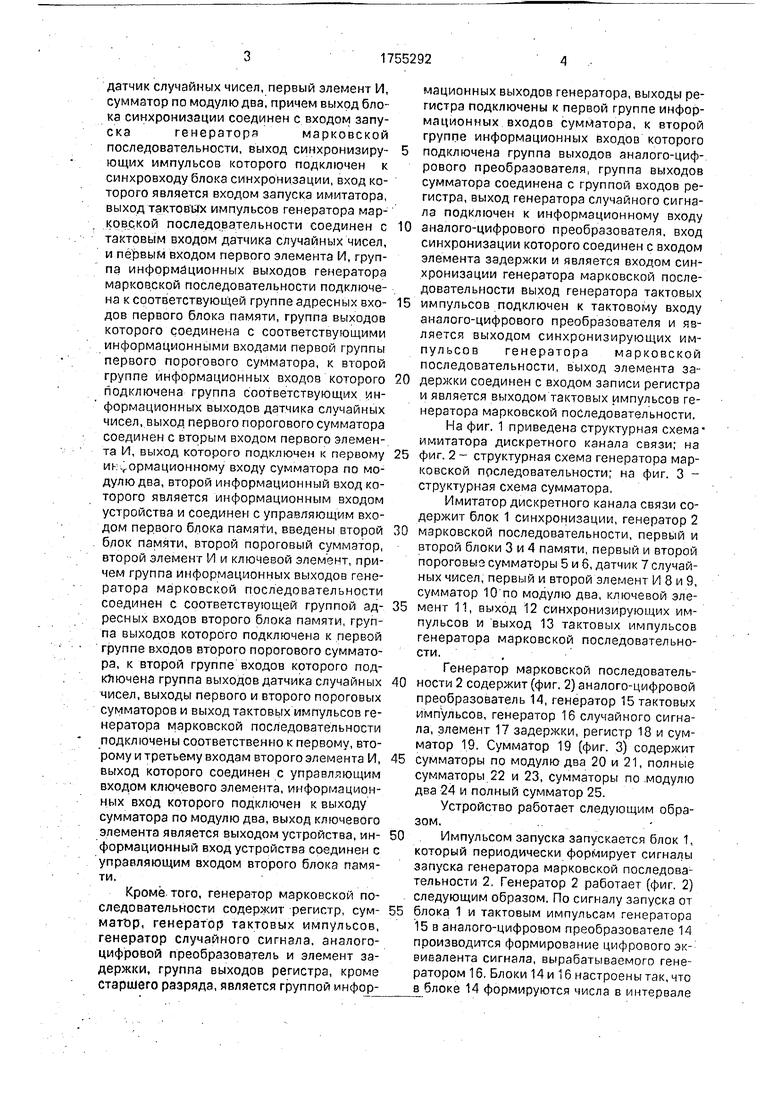

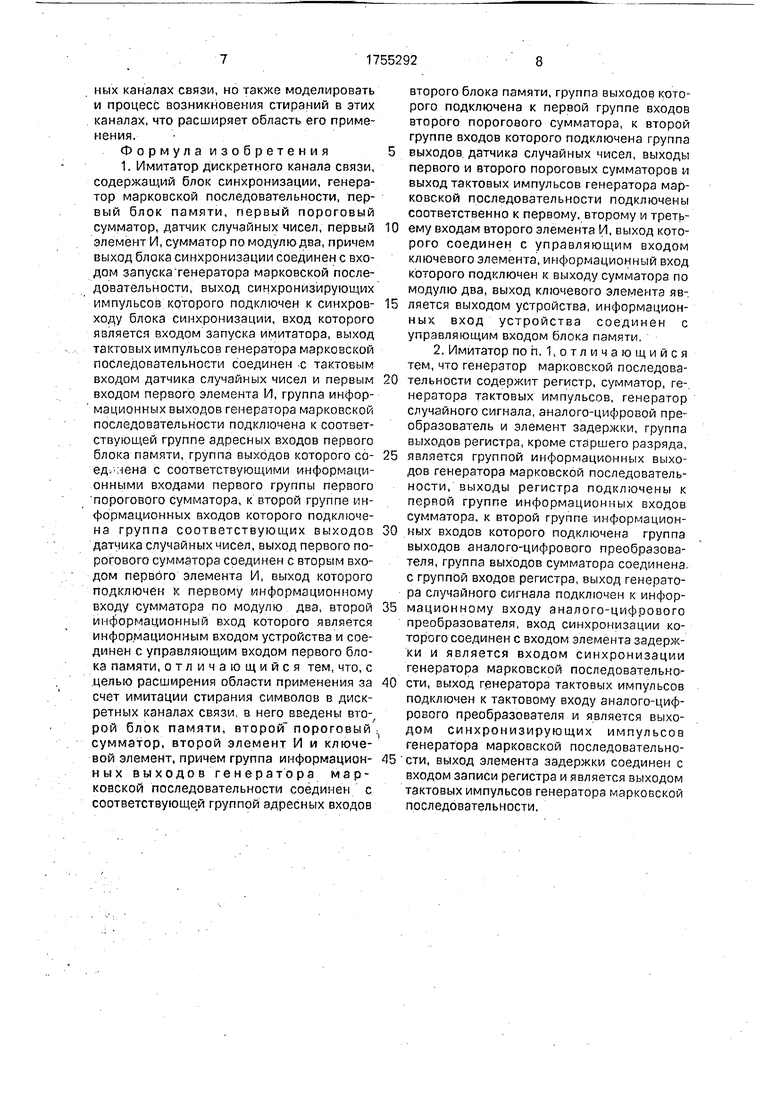

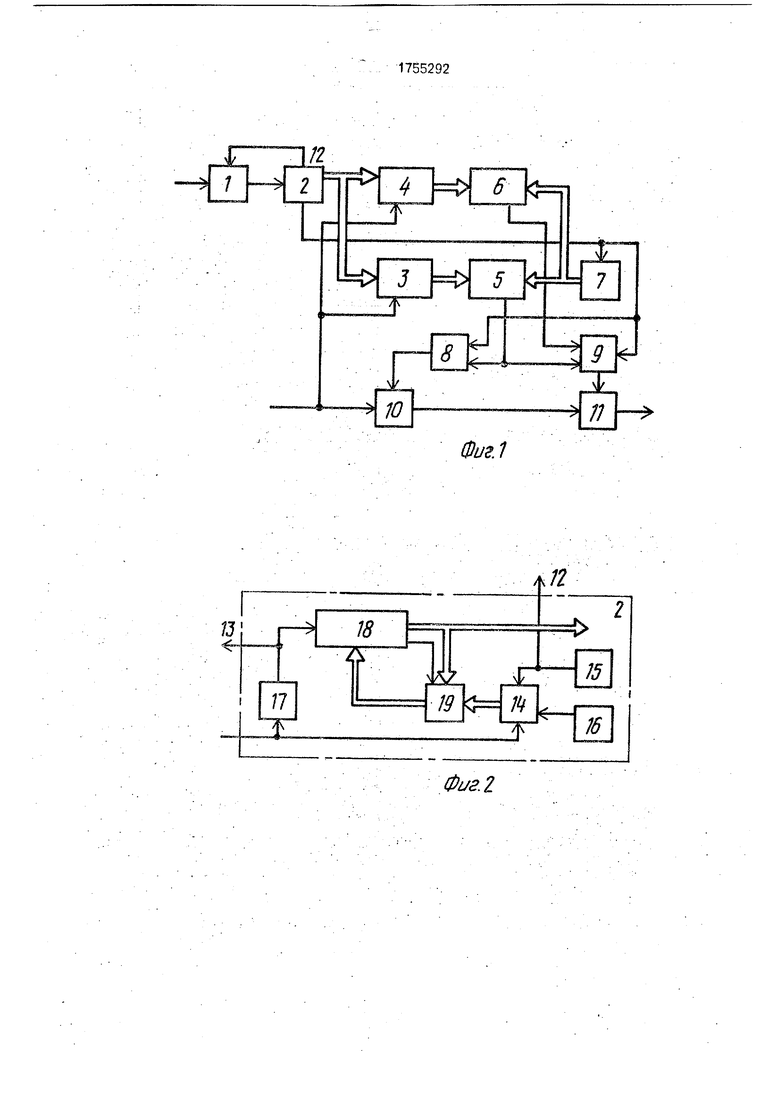

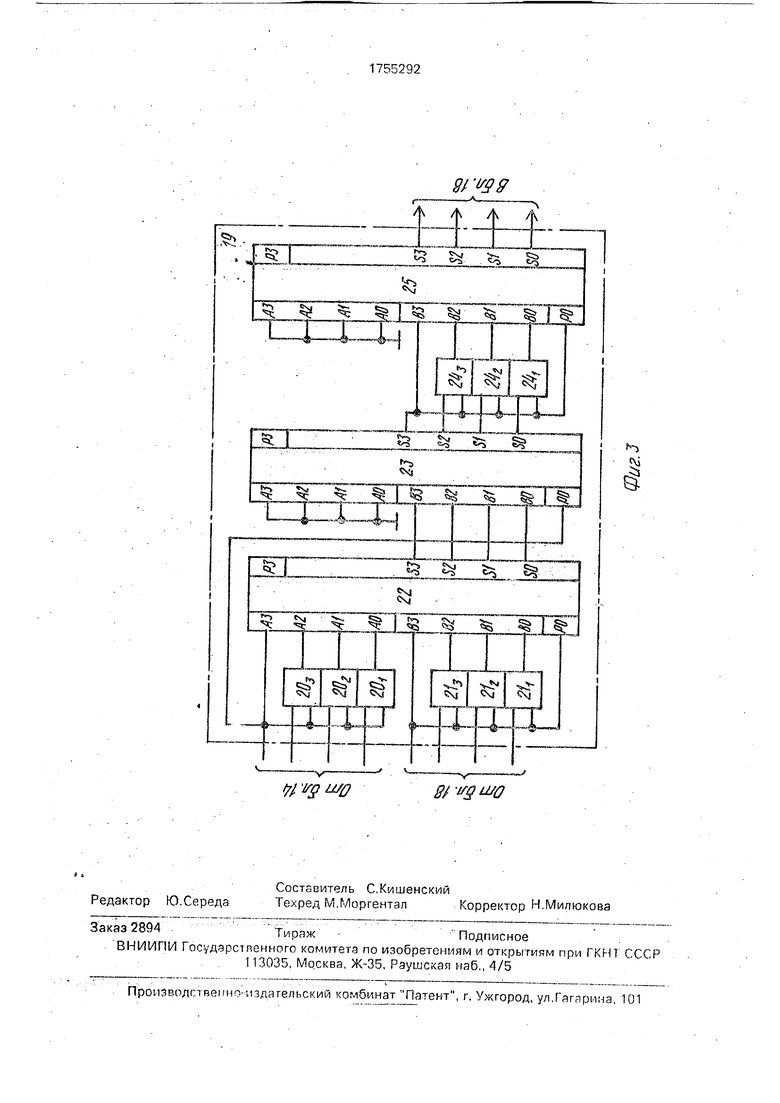

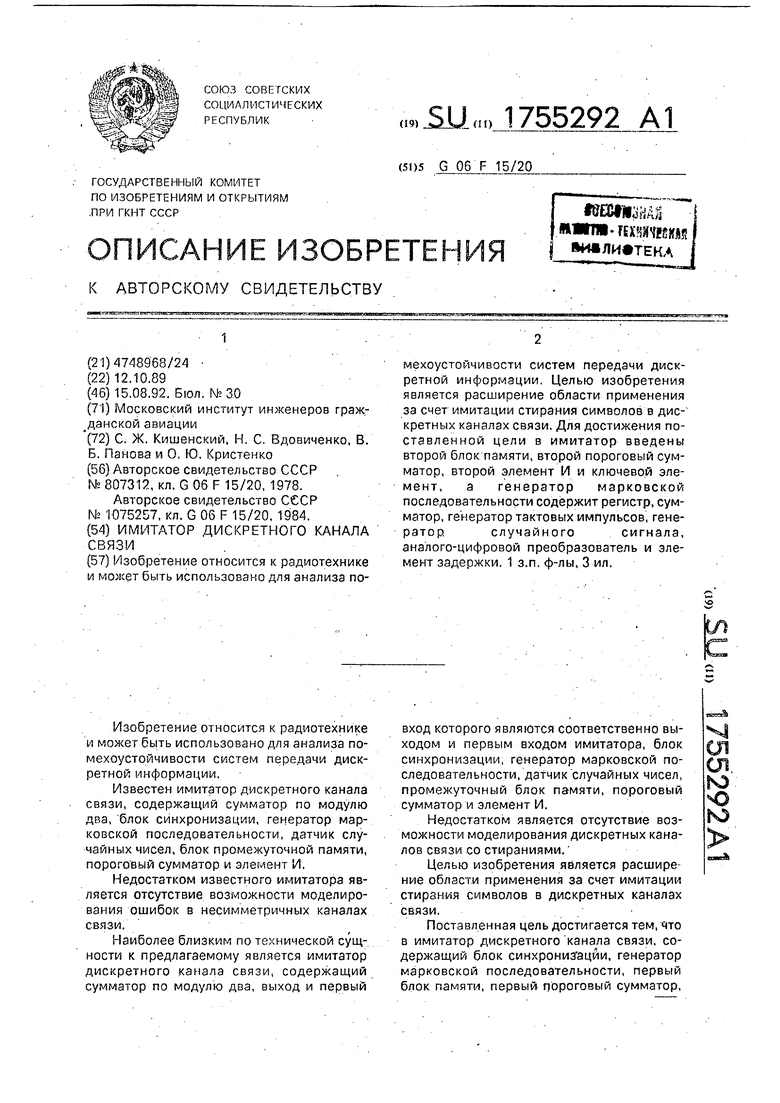

На фиг. 1 приведена структурная схема- имитатора дискретного канала связи; на фиг. 2 - структурная схема генератора марковской последовательности; на фиг. 3 - структурная схема сумматора.

Имитатор дискретного канала связи содержит блок 1 синхронизации, генератор 2 марковской последовательности, первый и второй блоки 3 и 4 памяти, первый и второй пороговые сумматоры 5 и 6, датчик 7 случайных чисел, первый и второй элемент И 8 и 9, сумматор 10 по модулю два, ключевой элемент 11, выход 12 синхронизирующих импульсов и выход 13 тактовых импульсов генератора марковской последовательности.

Генератор марковской последовательности 2 содержит (фиг. 2) аналого-цифровой преобразователь 14, генератор 15 тактовых импульсов, генератор 16 случайного сигнала, элемент 17 задержки, регистр 18 и сумматор 19. Сумматор 19 (фиг. 3) содержит сумматоры по модулю два 20 и 21, полные сумматоры 22 и 23, сумматоры по модулю два 24 и полный сумматор 25.

Устройство работает следующим образом.

Импульсом запуска запускается блок 1, который периодически формирует сигналы запуска генератора марковской последовательности 2, Генератор 2 работает (фиг. 2) следующим образом. По сигналу запуска от блока 1 и тактовым импульсам генератора 15 в аналого-цифровом преобразователе 14 производится формирование цифрового эк- еиеалента сигнала, вырабатываемого генератором 16, Блоки 14 и 16 настроены так, что в блоке 14 формируются числа в интервале

-К, -i К, где К - двоичное число, разрядность которого равна разрядности адресного пространства блока памяти и на единицу меньше разрядности регистра 18. Старший разряд чисел в аналого-цифровом преобразователе, регистре и сумматоре 19 является знаковым. Сформированное в блоке 14 число алгебраически суммируется с содержимым регистра 18 и с некоторой задержкой (определяемой элементов 17) вновь записывается в регистр 18. Таким образом осуществляется генерация чисел марковской последовательности, в которой каждое последующее число зависит от предыдущего, Знаковый разряд в адресном пространстве блока памяти не используется. Число состояний регистра 18 рявно числу состотний цепи Маркова (не учитывая знакового разряда).

После определения очередного состояния марковской последовательности генератор 2 формирует на информационных выходах код состояния, который задает адресные (кроме старшего) разряды блоков памяти 3 и 4, Старший разряд адресов определяется входной информацией - двоичным сигналом О или 1.

По сигналу с блока 2 датчик 7 случайных чисел формирует равномерно распределенное дробленое случайное число, которое поступает на соответствующие входы пороговых сумматоров 5 и 6. Пороговые с/мматоры формируют единицу на выходе при условии, что сумма слагаемых на их входах превысит единицу (как вероятности, снимаемые с выходов блоков памяти, так и число, формируемое датчиком 7 меньше единицы). Если одно из слагаемых равномерно распределено (в данном случае - число с датчика 7), то вероятность появления 1 на выходе соответствующего порогового сумматора полностью определяется значением другого слагаемого - вероятностными свойствами генерируемой марковской последовательности,

Сформированное значение выходного сигнала с выхода первого порогового сумматора 5 подается на один из входов сумматора 10 по модулю два и суммируется с информационным, что определяет либо неискаженную передачу данных каналом (при нулевом сигнале на выходе порогового сумматора 5), либо трансформацию символа (при единичном сигнале).

Запись информации для имитации ошибок и стираний в блоки памяти 3 и 4 производится до начала работы устройства (цепи записи не показаны). Принцип формирования информации в ячейках блоков памяти следующий. В ячейках блока памяти 4 записывается вероятность стирания соответствующего символа (О или 1) при текущем состоянии цепи Маркова, при этом срабатывание блока 6 означает, что исход передачи

некоторого текущего символа - стирание данного символа. В ячейки блока памяти 3 соответственно записываются суммарные вероятности исходов - стирания символа (аналогично блоку 4) и трансформации дан0 ного символа при соответствующем состоянии цепи Маркова. Таким образом, число, формируемое блоком 3 всегда не меньше числа, формируемого блоком 4, то есть срабатывание блока б автоматически сопро5 вождается срабатыванием блока 5.

Срабатывание блока 5 (при отсутствии срабатывания блока 6) означает факт трансформации передаваемого символа, срабатывание обоих блоков 5 и 6 - стирание

0 данного символа, отсутствие срабатывания обоих блоков - неискаженную передачу данного символа.

Тактовым выходом 13 формируется сигнал управления на элементы И 8 и 9. При

5 этом срабатывание элемента И 8 означает искажение символа в канале связи, а срабатывание элемента И 9 - стирание данного символа, При стирании символа выходной сигнал элемента И 9 запирает ключевой эле0 мент 11, который переходит в высокоимпе- дансное состояние, отключаясь выходом от выходного канала имитатора, моделируя стирание данного символа (когда в реальной ситуации невозможно принять решение

5 о значении сигнального признака данного символа - О или 1).

Таким образом, на выходе имитатора возможны три ситуации: единичное, нулевое и высокоимпедансное,

0 Сумматор 19 является алгебраическим (фиг. 3) и работает следующим образом. Алгебраическое сложение осуществляется в дополнительном коде, для чего отрицательное слагаемое переводится в форму допол5 нительного кода (инверсия всех разрядов и

добавление единицы в старший разряд). На

блоках 20 и 23 осуществляется получение

дополнительного кода первого слагаемого,

на блоках 21 и 22 - второго слагаемого,

0 блоками 24 и 25 реализуется перевод дополнительного кода суммы в прямой код (при необходимости). На фиг. 3 в качестве иллюстрации приведена схема алгебраического сумматора для двух трехразрядньр двоич5 ных чисел, а старший, четвертый разряд является знаковым. Правила получение дополнительного кода - стандартные,

Таким образом, предлагаемое устройство позволяет имитировать не только ошибки трансформации в двоичных несимметричных каналах связи, но также моделировать и процесс возникновения стираний в этих каналах, что расширяет область его применения.

Формула изобретения

1. Имитатор дискретного канала связи, содержащий блок синхронизации, генератор марковской последовательности, первый блок памяти, первый пороговый сумматор, датчик случайных чисел, первый элемент И, сумматор по модулю два, причем выход блока синхронизации соединен с входом запуска генератора марковской последовательности, выход синхронизирующих импульсов которого подключен к синхров- ходу блока синхронизации, вход которого является входом запуска имитатора, выход тактовых импульсов генератора марковской последовательности соединен с тактовым входом датчика спучайных чисел и первым входом первого элемента И, группа информационных выходов генератора марковской последовательности подключена к соответствующей группе адресных входов первого блока памяти, группа выходов которого со- ед йена с соответствующими информационными входами первого группы первого порогового сумматора, к второй группе информационных входов которого подключена группа соответствующих выходов датчика случайных чисел, выход первого порогового сумматора соединен с вторым входом первого элемента И, выход которого подключен к первому информационному входу сумматора по модулю два, второй информационный вход которого является информационным входом устройства и соединен с управляющим входом первого блока памяти, отличающийся тем, что, с целью расширения области применения за счет имитации стирания символов в дискретных каналах связи в него введены второй блок памяти, второй пороговый сумматор, второй элемент И и ключевой элемент, причем группа информацией- ных выходов генератора марковской последовательности соединен с соответствующей группой адресных входов

второго блока памяти, группа выходов которого подключена к первой группе входов второго порогового сумматора, к второй группе входов которого подключена группа выходов датчика случайных чисел, выходы первого и второго пороговых сумматоров и выход тактовых импульсов генератора марковской последовательности подключены соответственно к первому, второму и третьему входам второго элемента И, выход которого соединен с управляющим входом ключевого элемента, информационный вход которого подключен к выходу сумматора по модулю два, выход ключевого элемента является выходом устройства, информационных вход устройства соединен с управляющим входом Ьлока памяти

2. Имитатор по п. 1,отличающийся тем, что генератор марковской последовательности содержит регистр, сумматор, генератора тактовых импульсов, генератор случайного сигнала, аналого-цифровой преобразователь и элемент задержки, группа выходов регистра, кроме старшего разряда, является группой информационных выходов генератора марковской последовательности, выходы регистра подключены к первой группе информационных входов сумматора, к второй группе информационных входов которого подключена группа выходов аналого-цифрового преобразователя, группа выходов сумматора соединена с группой входов регистра, выход генератора случайного сигнала подключен к информационному входу аналого-цифрового преобразователя, вход синхронизации которого соединен с входом элемента задержки и является входом синхронизации генератора марковской последовательности, выход генератора тактовых импульсов подключен к тактовому входу аналого-цифрового преобразователя и является выходом синхронизирующих импульсов генератора марковской последовательности, выход элемента задержки соединен с входом записи регистра и является выходом тактовых импульсов генератора марковской последовательности.

Фиг. 2

gj Wff

| название | год | авторы | номер документа |

|---|---|---|---|

| Имитатор дискретного канала связи | 1989 |

|

SU1755293A1 |

| Имитатор дискретного канала связи | 1981 |

|

SU964651A2 |

| Имитатор дискретного канала связи | 1980 |

|

SU951318A2 |

| Имитатор дискретного канала связи | 1989 |

|

SU1661788A1 |

| Имитатор дискретного канала связи | 1989 |

|

SU1651293A1 |

| Имитатор дискретного канала связи | 1984 |

|

SU1223246A2 |

| Имитатор дискретного канала связи | 1986 |

|

SU1348853A2 |

| Имитатор дискретного канала связи | 1986 |

|

SU1425702A1 |

| Имитатор дискретного канала связи с ошибками синхронизации | 1980 |

|

SU934479A2 |

| Имитатор дискретных каналов связи | 1979 |

|

SU842827A1 |

Изобретение относится к радиотехнике и может быть использовано для анализа помехоустойчивости систем передачи дискретной информации Целью изобретения является расширение области применения за счет имитации стирания символов в дискретных каналах связи. Для достижения по- ставленной цели в имитатор введены второй блок памяти, второй пороговый сумматор, второй элемент И и ключевой элемент, а генератор марковской последовательности содержит регистр, сумматор, генератор тактовых импульсов, генераторслучайногосигнала, аналого-цифровой преобразователь и элемент задержки. 1 з.п. ф-лы, 3 ил.

ч

т

Ј Ј St I Ј Јs s S

Ч J 3 55

j

v %JLt

Ni

т

I

J

| ВРАЩАЮЩИЙ ЭЛЕКТРОД ДУГОВОГО ВЕНТИЛЯ БОЛЬШОЙ МОЩНОСТИ | 1949 |

|

SU80731A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для сравнения двоичных чисел | 1982 |

|

SU1075257A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1992-08-15—Публикация

1989-10-12—Подача