I

Изобретение относится к связи и может использоваться в системах передачи дискретной инфорамции методом фазовой и относительной фазовой манипуляции.

Известен цифровой демодулятор фазом нипулированных сигналов, содержащий формирователь входного сигнала и последовательно соединенные генератор стабильной частоты, управляемый делитель частоты и формирователь опорных сигналов 1.

Однако известный демодулятор имеет сравнительно невысокую помехоустойчивость.

Цель изобретения - повышение помехоустойчивости.

Указанная цель достигается тем, что в известный демодулятор введены блоки равнозначности,реверсивные счетчики и последовательно соединеннее блок сравнения и анализатор сигналов, соответствующие входы которых соединены с первыми выходами

реверсивных счетчиков, к первым входам которых подключены выходы соответствующих блоков равнозначности, входы которых соединены с выходом формирователя входного сигнала и выходами формирователя опорных сигналов, при этом вторые выходы реверсивных счетчиков подключены к входам блока сравнения, я выход аналичатооя сигналов г.оепинен с вто10оым вхойом управляемого делителя частоты.

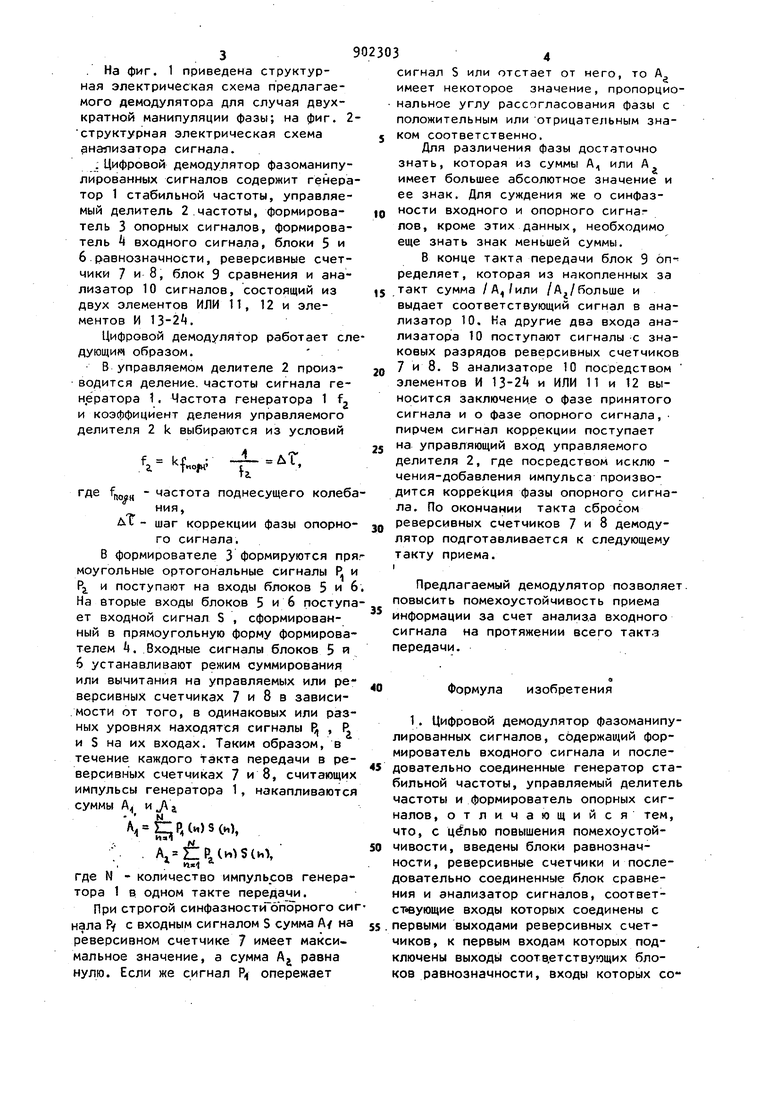

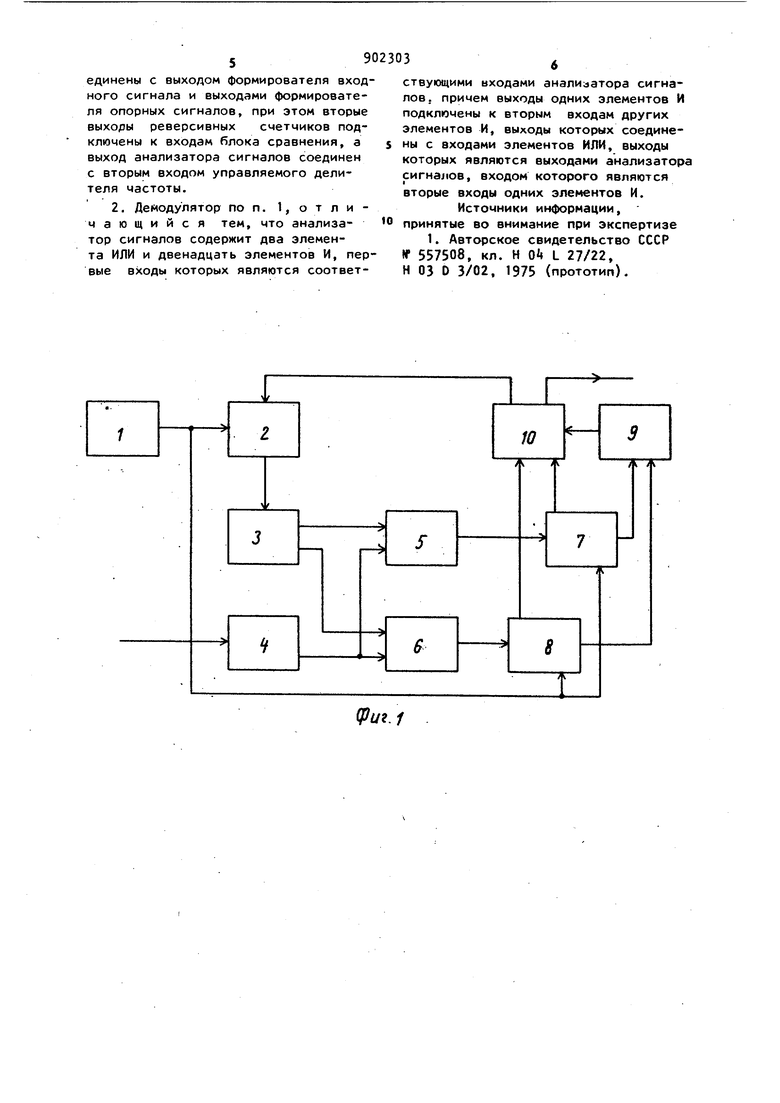

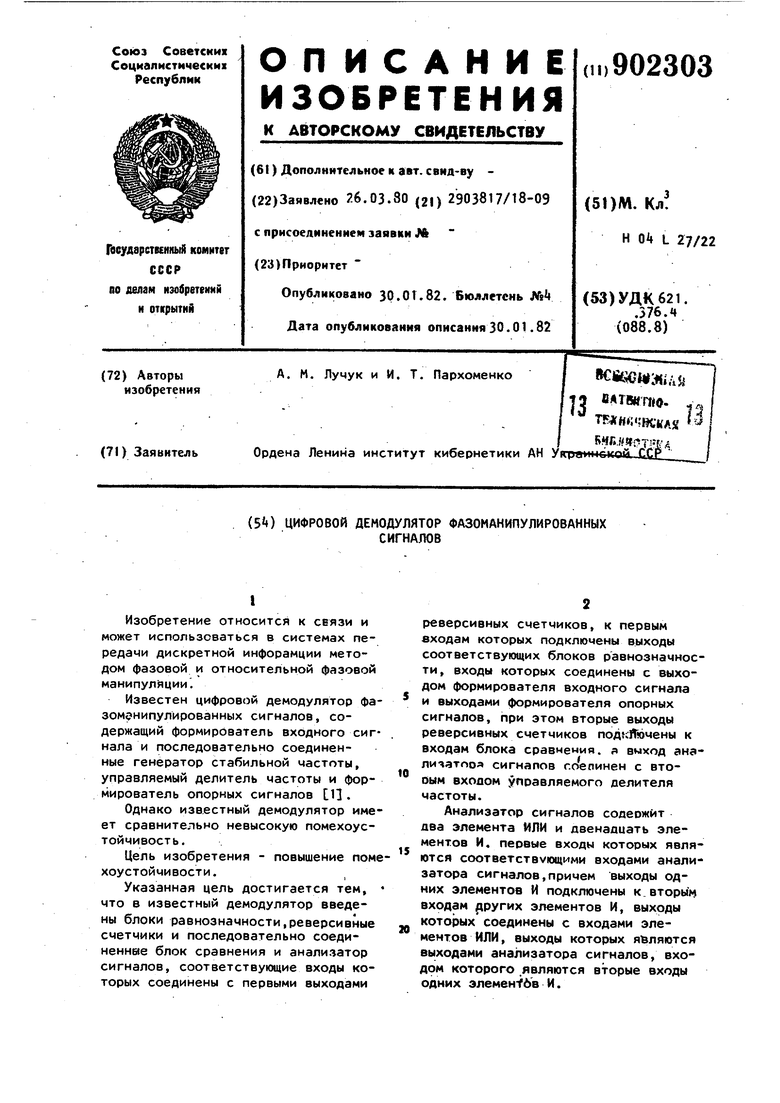

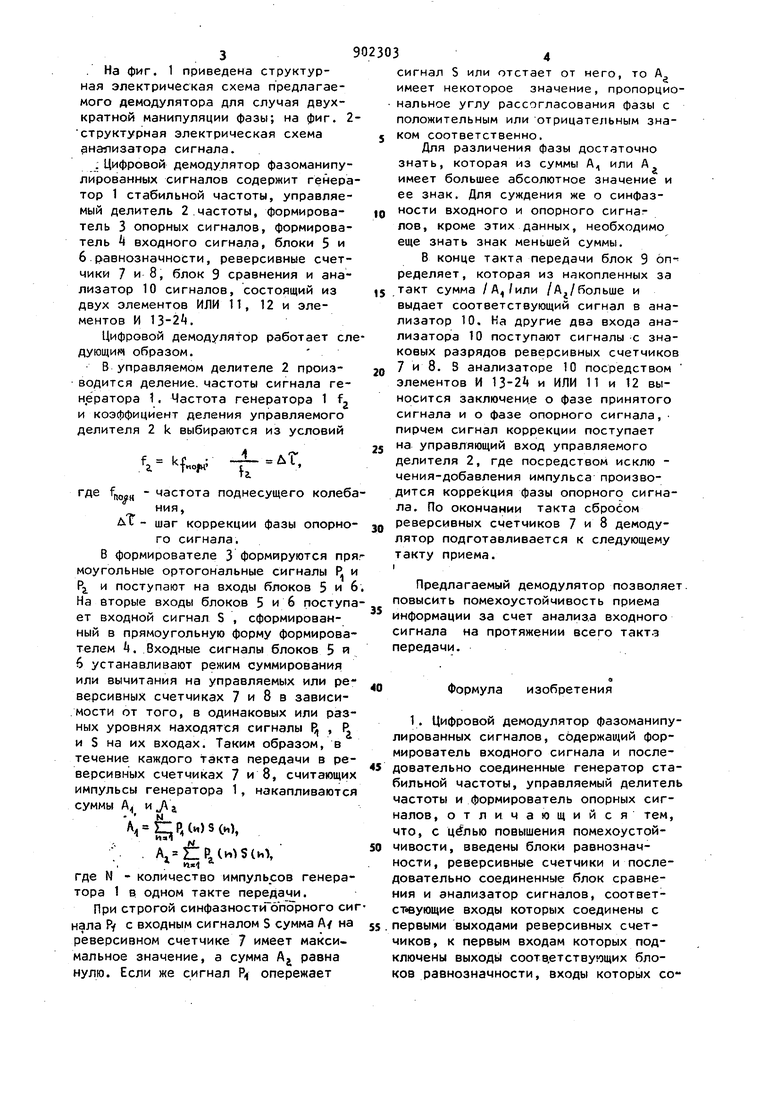

Анализатор сигналов содержит два элемента ИЛИ и двенадцать элементов И. первые входы которых явля15ются соответствующими входами анализатора сигналов,причем выходы одних элементов И подключены к.вторым входам других элементов И, выходы которых соединены с входами эле20ментов ИЛИ, выходы которых являются вь1ходами анализатора сигналов, входом которого являются вторые входы одних элемент6в И. . На фиг. 1 приведена структурная электрическая схема предлагаемого демодулятора для случая двухкратной манипуляции фазы; на фиг. 2 структурная электрическая схема анаяизатсра сигнала. ; Цифровой демодулятор фазоманипулированных сигналов содержит генера тор 1 стабильной частоты, управляемый делитель 2.частоты, формирователь 3 опорных сигналов, формирователь входного сигнала, блоки 5 и 6 равнозначности, реверсивные счетчики 7 и 8, блок 9 сравнения и анализатор 10 сигналов, состоящий из двух элементов ИЛИ 11, 12 и элементов И . Цифровой демодулятор работает ел дующи ч образом. В управляемом делителе 2 производится деление, частоты сигнала генератора 1. Частота генератора 1 fj и коэффициент деления управляемого делителя 2 k выбираются из условий - частота поднесущего колеб ния, At - шаг коррекции фазы опорно го сигнала. В формирователе 3 формируются пр моугольные ортогональные сигналы R Р и поступают на входы блоков 5 и На вторые входы блоков 5 и 6 поступ ет входной сигнал S , сформированный в прямоугольную форму формирова телем . Входные сигналы блоков 5 и 6 устанавливают режим суммирования или вычитания на управляемых или ре версивных счетчиках 7 и 8 в зависимости от того, в одинаковых или раз ных уровнях находятся сигналы 15| , и S на их входах. Таким образом, в течение каждого такта передачи в ре версивных счетчиках 7 и 8, считающих импульсы генератора 1, накапливаютс суммы А и J J ,Р,(и)зси), А. р,((и Л где N - количество импульсов генера тора 1 в одном такте передачи. При строгой синфазности 6порного си нала i с входным сигналом S сумма А/ на реверсивном счетчике 7 имеет максимальное значение, а сумма Aj равна нулю. Если же сигнал Р опережает 4 сигнал S или отстает от него, то А имеет некоторое значение, пропорциональное углу рассогласования фазы с положительным или отрицательным знаком соответственно. Для различения фазы достаточно знать, которая из суммы А или А имеет большее абсолютное значение и ее знак. Для суждения же о синфазности входного и опорного сигнаг лов, кроме этих данных, необходимо еще знать знак меньшей суммы. В конце такта передачи блок 9 определяет, которая из накопленных за такт сумма /А,/или /А /больше и выдает соответствующий сигнал в анализатор 10. На другие два входа анализатора 10 поступают сигналы с знаковых разрядов реверсивных счетчиков 7 и 8. 8 анализаторе 10 посредством элементов И 13-2 и ИЛИ 11 и 12 выносится заключение о фазе принятого сигнала и о фазе опорного сигнала, пирчем сигнал коррекции поступает на управляющий вход управляемого делителя 2, где посредством исклю чения-добавления импульса производится коррекция фазы опорного сигнала. По окончании такта сбросом реверсивных счетчиков 7 и 8 демодулятор подготавливается к следующему такту приема. Предлагаемый демодулятор позволяет, повысить помехоустойчивость приема информации за счет анализа входного сигнала на протяжении всего тактз передачи. Формула изобретения 1. Цифровой демодулятор фазоманипулированных сигналов, содержащий формирователь входного сигнала и последовательно соединенные генератор стабильной частоты, управляемый делитель частоты и формирователь опорных сигналов, отличающийся тем, что, с повышения помехоустойчивости, введены блоки равнозначности, реверсивные счетчики и последовательно соединенные блок сравнения и анализатор сигналов, соответст«вующие входы которых соединены с первыми выходами реверсивных счетчиков, к первым входам которых подключены выходы соотв,етствующих блоков равнозначности, входы которых соединены с выходом формирователя входного сигнала и выходами формирователя опорных сигналов, при этом вторые выхоры реверсивных счетчиков подключены к входам блока сравнения, а выход анализатора сигналов соединен с вторым входом управляемого делителя частоты.

2, Демодулятор по п. 1, о т л и чающийся тем, что анализатор сигналов содержит два элемента ИЛИ и двенадцать элементов И, первые входы которых являются соответствующими входами анализатора сигналов, причем выходы одних элементов И подключены к вторым входам других элементов И, выходы которых соединены с входами элементов ИЛИ, выходы которых являются выходами анализатора сигналов, входом которого являются вторые входы одних элементов И. Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР If 557508, кл. Н Oi L 27/22, Н 03 D 3/02, 1975 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой демодулятор частотно-манипулированных сигналов | 1982 |

|

SU1058083A1 |

| Цифровой когерентный демодулятор сигналов относительной фазовой модуляции | 1975 |

|

SU557508A1 |

| УСТРОЙСТВО АВТОМАТИЧЕСКОЙ ПОДСТРОЙКИ ЧАСТОТЫ | 1993 |

|

RU2089047C1 |

| ПРЕОБРАЗОВАТЕЛЬ ПЕРЕМЕННОГО НАПРЯЖЕНИЯ | 1991 |

|

RU2020707C1 |

| Демодулятор фазоманипулированных сигналов | 1983 |

|

SU1095441A1 |

| Устройство восстановления несущей фазоманипулированного сигнала | 1990 |

|

SU1786659A1 |

| Устройство для преобразования фазовой модуляции сигнала в цифровой код | 1984 |

|

SU1220127A1 |

| Аналого-цифровой преобразователь сдвига фаз | 1981 |

|

SU955519A2 |

| Устройство для измерения преобладаний двоичных сигналов | 1985 |

|

SU1246396A1 |

| Устройство для передачи и приема информации по двупроводной линии связи | 1990 |

|

SU1836709A3 |

(риг.1

(риг. Z

Авторы

Даты

1982-01-30—Публикация

1980-03-26—Подача