11

Изобретение относится к вычислительной и измерительной технике, в частности к преобразователям фаза-код

Цель изобретения - повышение точности преобразования путем фиксации среднего уровня переменного цифрового кода, в результате отсутствуют искажения закона изменения фазы входного сигнала, что позволяет использовать устройство для измерения Параметров фазовой модуляции с повышенной точностью, и расширяется область применения преобразователей фаза-код.

В устройстве обеспечивается при- вязка среднего уровня переменного цифрового кода п к заданному кодуп, который соответствует коэффициенту деления управляемого делителя при отсутствии сигнала на входе устрой- ства.

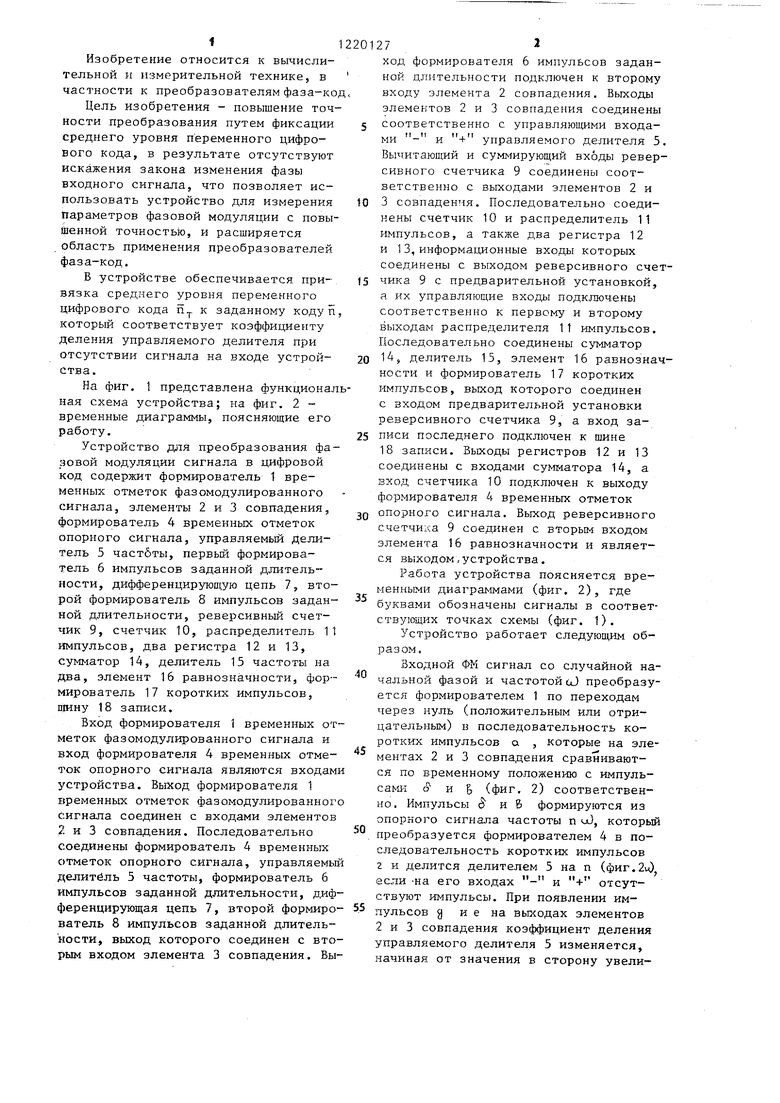

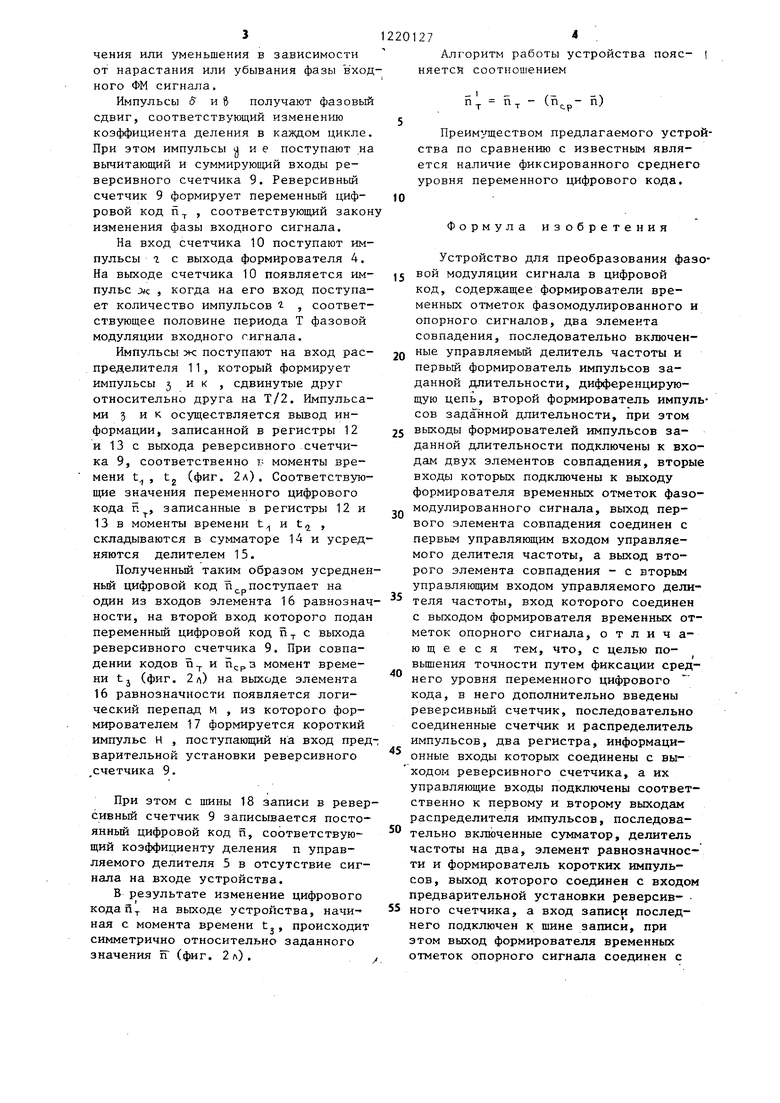

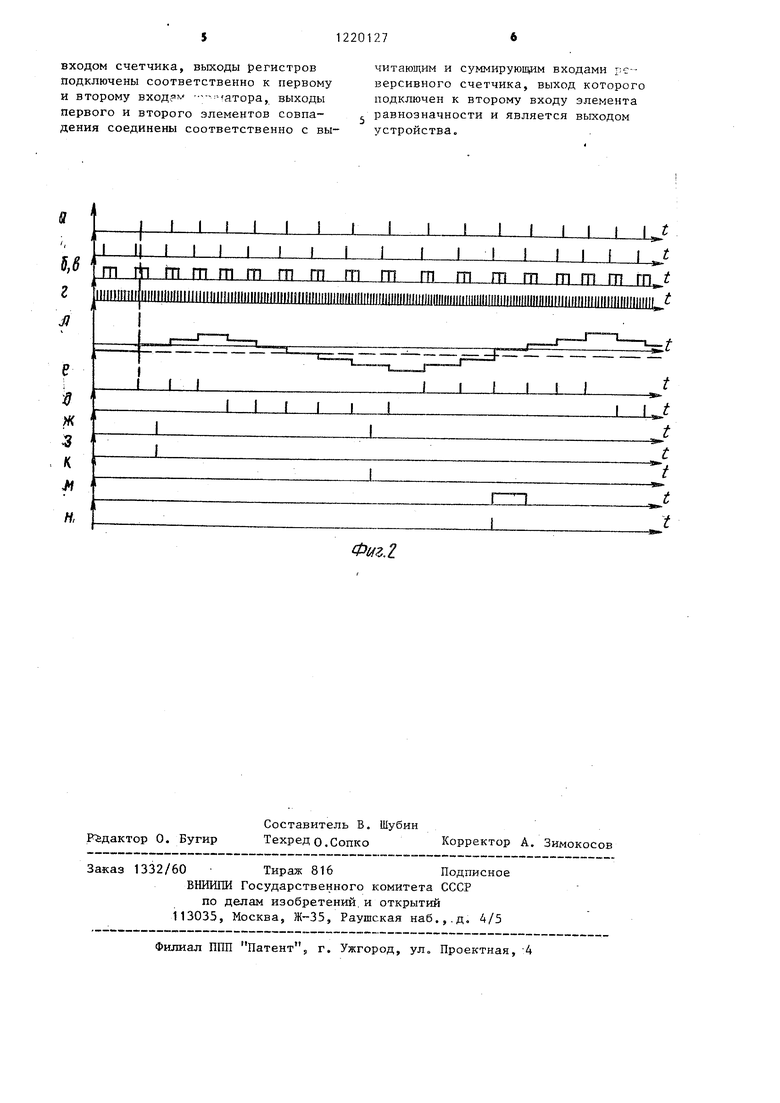

На фиг. 1 представлена функциональная схема устройства; на фиг. 2 - временные диаграммы, поясняющие его работу.

Устройство для преобразования фазовой модуляции сигнала в цифровой код содержит формирователь 1 временных отметок фазомодулированного сигнала, элементы 2 и 3 совпадения, формирователь 4 временных отметок опорного сигнала, управляемый делитель 5 частбты, первый формирователь 6 импульсов заданной длительности, дифференцирующую цепь 7, второй формирователь 8 импульсов задан- ной длительности, реверсивный счетчик 9, счетчик 10, распределитель 11 импульсов, два регистра 12 и 13, сумматор 14, делитель 15 частоты на два, элемент 16 равнозначности, фор- мирователь 17 коротких импульсов, шину 18 записи.

Вход формирователя 1 временных отметок фазомодулированного сигнала и вход формирователя 4 временных отме- ток опорного сигнала являются входами устройства. Выход, формирователя 1 временных отметок фазомодулированного сигнала соединен с входами элементов 2 и 3 совпадения. Последовательно соединены формирователь 4 временных отметок опорного сигнала, управляемьш делитель 5 частоты, формирователь 6 импульсов заданной длительности, дифференцирующая цепь 7, второй формиро- ватель 8 импульсов заданной длительности, выход которого соединен с вторым входом элемента 3 совпадения. Вы

272

ход формирователя 6 импульсов заданной длительности подключен к второму входу элемента 2 совпадения. Выходы элементов 2 и 3 совпадения соединены соответственно с управляющими входами - и + управляемого делителя 5. Вычитающий и суммирующий входы реверсивного счетчика 9 соединены соответственно с выходами элементов 2 и 3 совпадент1я. Последовательно соединены счетчик 10 и распределитель 11 импульсов, а также два регистра 12 и 13, информационные входы которых соединены с выходом реверсивного счетчика 9 с предварительной установкой, а их управляющие входы подключены соответственно к первому и второму выходам распределителя 1t импульсов. Последовательно соединены сумматор 14, делитель 15, элемент 16 равнозначности и формирователь 17 коротких импульсов, выход которого соединен с входом предварительной установки реверсивного счетчика 9, а вход записи последнего подключен к шине 18 записи. Выходы регистров 12 и 13 соединены с входами сумматора 14, а вход счетчика 10 подключен к выходу формирователя 4 временных отметок опорного сигнала. Выход реверсивного счетчика 9 соединен с вторым входом элемента 16 равнозначности и является вь.ходом/устройства.

Работа устройства поясняется вре- менньЕми диаграммами (фиг. 2), где буквами обозначены сигналы в соответствующих точках схемы (фиг. 1).

Устройство работает следующим образом.

Входной ФМ сигнал со случайной начальной фазой и частотой (х) преобразуется формирователем 1 по переходам через нуль (положительным или отрицательным) в последовательность коротких импульсов а , которые на элементах 2 и 3 совпадения сравниваются по временному положению с импульсами и S (фиг. 2) соответственно. Импульсы § и 6 формируются из опорного сигнала частоты п uJ, который преобразуется формирователем 4 в последовательность коротких импульсов г и делится делителем 5 на п (фиг.2и) если На его входах - и + отсутствуют импульсы. При появлении импульсов g и е на выходах элементов 2 и 3 совпадения коэффициент деления управляемого делителя 5 изменяется, начиная от значения в сторону увели3

чения или уменьшения в зависимости от нарастания или убывания фазы в ход ного ФМ сигнала.

Импульсы 5 и 8 получают фазовьй сдвиг, соответствующий изменению коэффициента деления в каждом цикле. При этом импульсы М я поступают на вычитающий и суммирующий входы реверсивного счетчика 9. Реверсивный счетчик 9 формирует переменный цифровой код п-г соответствующий закон изменения фазы входного сигнала.

На вход счетчика 10 поступают импульсы 1 с выхода формирователя 4. На выходе счетчика 10 появляется импульс JK , когда на его вход поступает количество импульсов i , соответствующее половине периода Т фазовой модуляции входного сигнала.

Импульсы эк поступают на вход распределителя 11, который формирует импульсы 3 и к , сдвинутые друг относительно друга на Т/2. Импульсами 5 и к осуществляется вьшод информации, записанной в регистры 12 и 13 с выхода реверсивного счетчика 9, соответственно в моменты времени t , tg (фиг. 2л). Соответствующие значения переменного цифрового кода г. , записанные в регистры 12 и 13 в моменты времени t и t , складываются в сумматоре 14 к усредняются делителем 15.

Полученньй таким образом усредненный цифровой код П|. поступает на один из входов элемента 16 равнозначности, на второй вход которого подан переменный цифровой код п с вьгхода реверсивного счетчика 9. При совпадении кодов П-j. и П(-рЗ момент времени tj (фиг. 2л) на выходе элемента 16 равнозначности появляется логический перепад м , из которого формирователем 17 формируется короткий импульс н , поступающий на вход предварительной установки реверсивного ,счетчика 9.

При этом с шины 18 записи в реверсивный счетчик 9 записывается постоянный цифровой код тг, соответствующий коэффициенту деления п управляемого делителя 5 в отсутствие сигнала на входе устройства.

В результате изменение цифрового кодай - на выходе устройства, начиная с момента времени t, происходит симметрично относительно заданного значения гГ (фиг. 2л).

220127

Алгоритм работы устройства пояс- няетсй соотношением

I

п п - ( п)

Преимуществом предлагаемого устройства по сравнению с известным является наличие фиксированного среднего уровня переменного цифрового кода.

10

5

0

5

0

5

0

5

0

Формула изобретения

Устройство для преобразования фазовой модуляции сигнала в цифровой код, содержащее формирователи временных отметок фазомодулированного и опорного сигналов, два элемента совпадения, последовательно включенные управляемый делитель частоты и первый формирователь импульсов заданной длительности, дифференцирующую цепь, второй формирователь импульсов задаГнной длительности, при этом выходы формирователей импульсов заданной длительности подключены к входам двух элементов совпадения, вторые входы которых подключены к выходу формирователя временных отметок фазомодулированного сигнала, выход первого элемента совпадения соединен с первым управляющим входом управляемого делителя частоты, а выход второго элемента совпадения - с вторым управляющим входом управляемого делителя частоты, вход которого соединен с выходом формирователя временных отметок опорного сигнала, отличающееся тем, что, с целью по- вьшения точности путем фиксации среднего уровня переменного цифрового кода, в него дополнительно введены реверсивный счетчик, последовательно соединенные счетчик и распределитель импульсов, два регистра, информационные входы которых соединены с выходом реверсивного счетчика, а их управляющие входы подключены соответственно к первому и второму выходам распределителя импульсов, последовательно включенные сумматор, делитель частоты на два, элемент равнозначности и формирователь коротких импульсов, выход которого соединен с входом предварительной установки реверсивного счетчика, а вход записи последнего подключен к шине записи, при этом выход формирователя временных отметок опорного сигнала соединен с

входом счетчика, выходы регистров подключены соответственно к первому и второму -- «атора, выходы первого и второго элементов совпадения соединены соответственно с вычитающим и суммирующим входами рс-- версивного счетчика, выход которого подключен к второму входу элемента равнозначности и является выходом устройства.

f I

J

JиIIIL

II

m rti mnmiiiiii

fn m m m m mm mшCEL

JLI J I

) I IU.

m m m m mj t

t

-

Lj

-

t

редактор 0. Бугир

Составитель В. Шубин

Техред о.Сопко Корректор А. Зимокосов

Заказ 1332/60 Тираж 816Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений, и открытий 113035, Москва, , Раушская наб.,.д, 4/5

Филиал ППП Патент, г. Ужгород, ул. Проектная, 4

Фмг.г

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для преобразования фазовой модуляции сигнала в цифровой код | 1975 |

|

SU741460A1 |

| УПРАВЛЯЮЩИЙ АППАРАТНО-ПРОГРАММНЫЙ КОМПЛЕКС ДЛЯ ОБРАБОТКИ РАДИОЛОКАЦИОННОЙ ИНФОРМАЦИИ | 2001 |

|

RU2222028C2 |

| Цифровой фазометр | 1987 |

|

SU1458836A1 |

| Преобразователь фазового сдвига в цифровой код | 1982 |

|

SU1056073A1 |

| Устройство для программного управления приводом | 1984 |

|

SU1226410A1 |

| Устройство для оценки амплитуды узкополосного случайного процесса | 1987 |

|

SU1499375A1 |

| Преобразователь средней частоты в код | 1977 |

|

SU660245A1 |

| Устройство индикации пеленга | 1983 |

|

SU1167555A1 |

| Система цикловой синхронизации для многоканальных систем связи | 1988 |

|

SU1598193A1 |

| ИМПУЛЬСНЫЙ РАДИОЛОКАТОР | 1985 |

|

SU1840927A1 |

Изобретение относится к вычислительной и измерительной технике.Цель изобретения - повьшение точности преобразования. Устройство содержит формирователь 1 временных отметок фазомодулированного сигнала, элементы 2 и 3 совпадения, формирователь 4 временных отметок опорного сигнала, управляемый делитель 5 частоты, формирователи 6 и 8 импульсов, дифференцирующую цепь 7, реверсивный счетчик 9, счетчик 10, распределител 11 импульсов, регистры 12 и 13, сумматор 14, делитель 15 частоты на два, элемент 16 равнозначности, формирователь 17 коротких импульсов и шину записи 18. Введение в устройство реверсивного счетчика, счетчика, распределителя импульсов, двух регистров, сумматора, делителя частоты на два, элемента равнозначности и формирователя коротких импульсов позволило фиксировать уровень переменного цифрового результате чего отсутствуют искажения закона изменения фазы входного сигнала. 2 ил. i (Л to ю ю

| Устройство для преобразования фазы в цифровой код | 1973 |

|

SU448596A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Устройство для преобразования фазовой модуляции сигнала в цифровой код | 1975 |

|

SU741460A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1986-03-23—Публикация

1984-07-23—Подача