1

Изобретение относится к средствам автоматики и вьтислительной техники и предназначено для сравнения любого количества двоичных чисел производной разрядности и выбора среди них большего (меньшего) по величине числа.

Известно устройство сравнения, содеркаЩее регистры, элементы Л. ШМ, которое предназначено для сравнения И-разрядных чисел l.

Недостатками, этого устройства являются низкое быстродействие и значительные аппаратурные затраты.

Наиболее близким по технической сущности к предлагаемому, является устройство для сравнения трех двоичных чисел, содержащее генератор импульсов, ключевую схему, регистрсчетчик левого конца интервала, регистр-счетчик сравниваемого числа, регистр-счетчик правого конца интервала, схему формирования сигнала с нахождением числа за правой границей интервала, элемент задержки, элемент памяти, схему формирования сигнала с нахождением числа левее интервала, схему формирования сигнала с нахозкдением числа внутри интервала, схему формирования сигнала о нахозчдении числа правее интервала 2 J.

Недостатками известного устройства являются также низкое быстродействие и болыше аппаратурные затраты.

Цель изобретения - повьшение быстродействия и упрощение устройства.

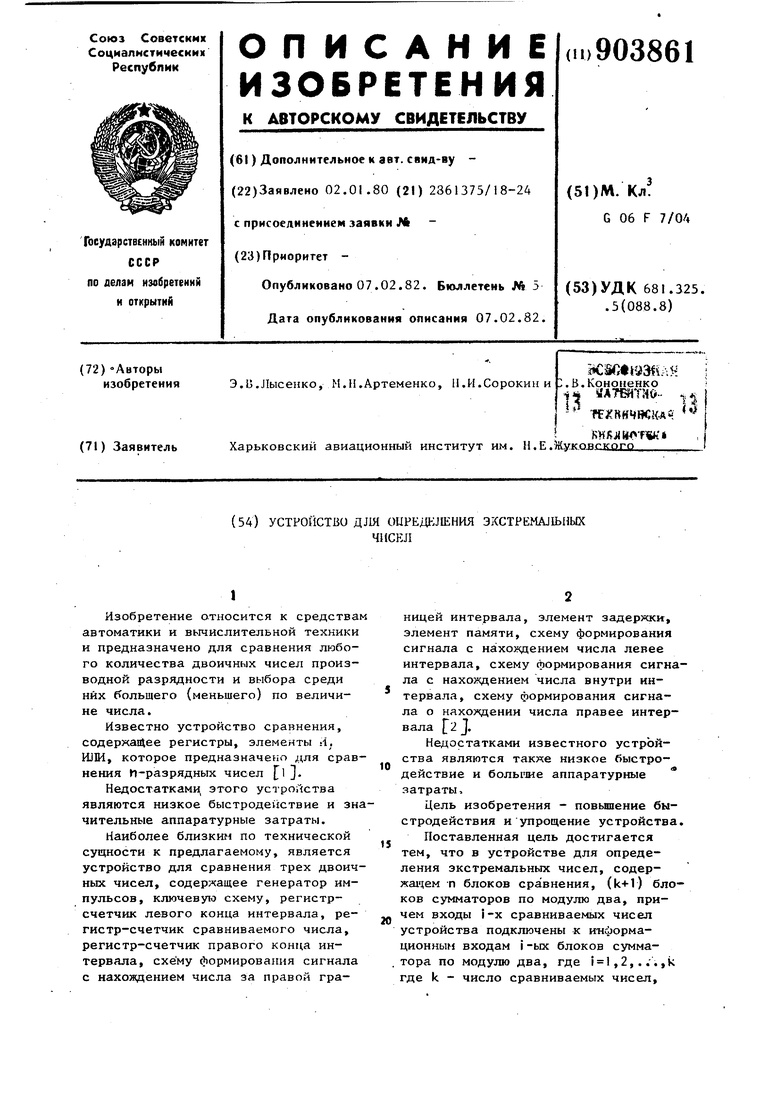

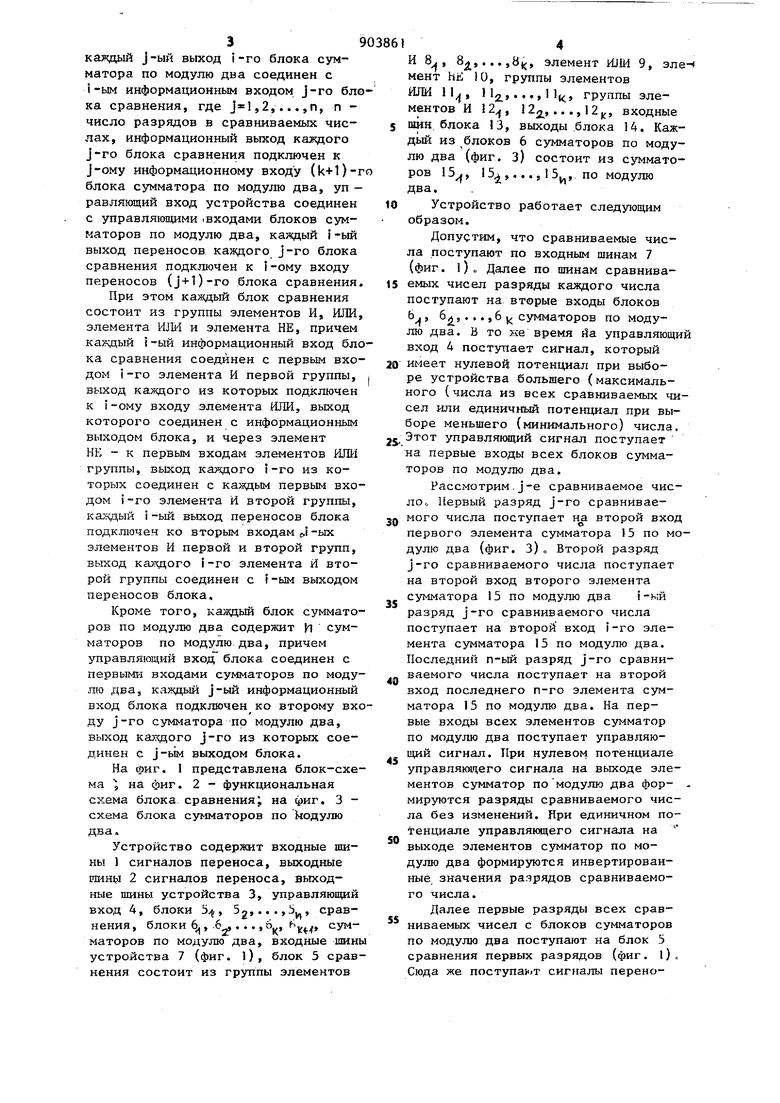

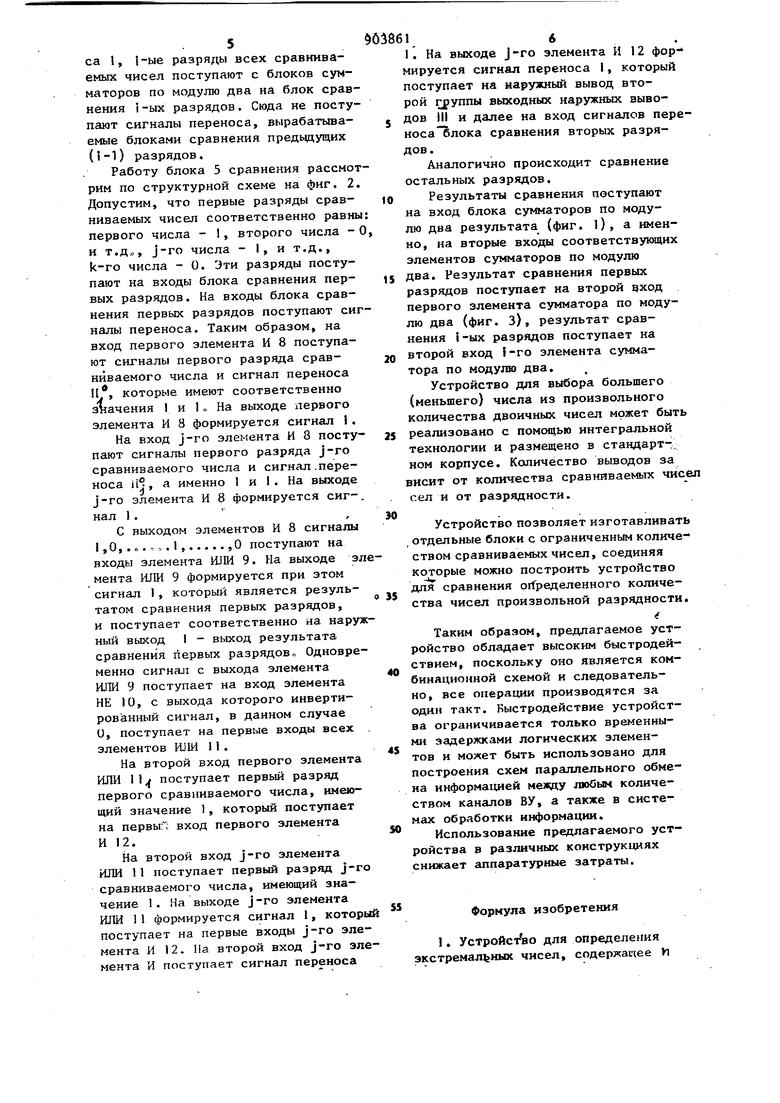

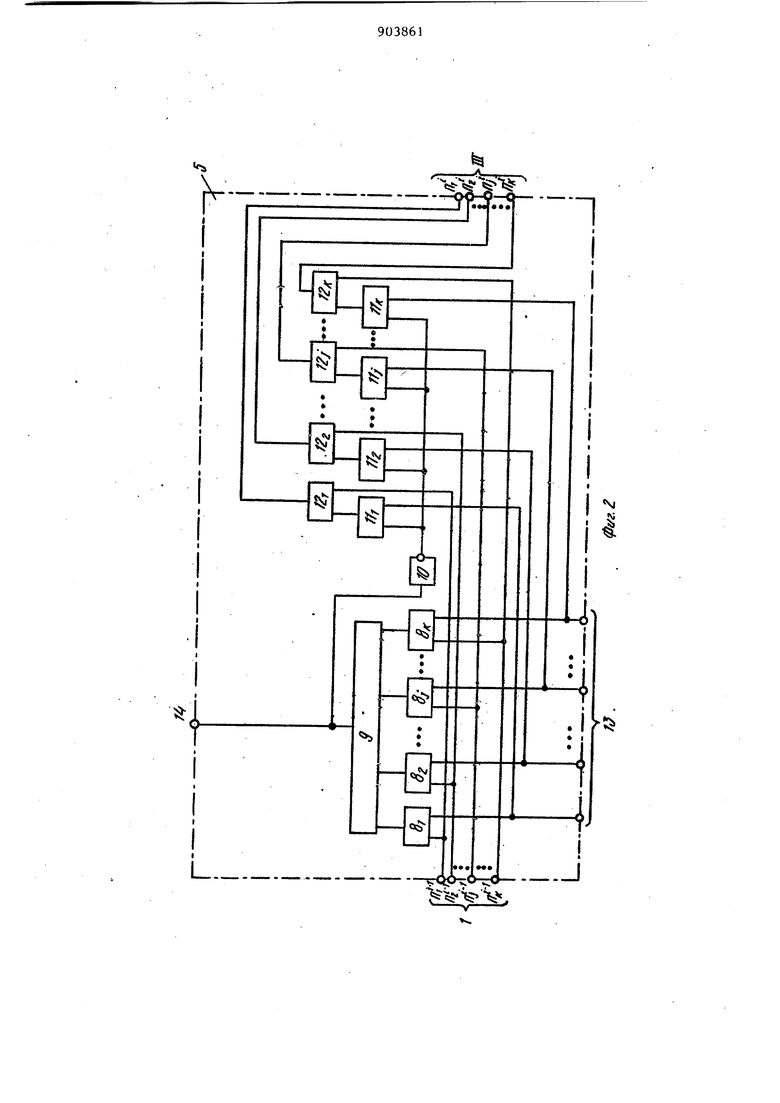

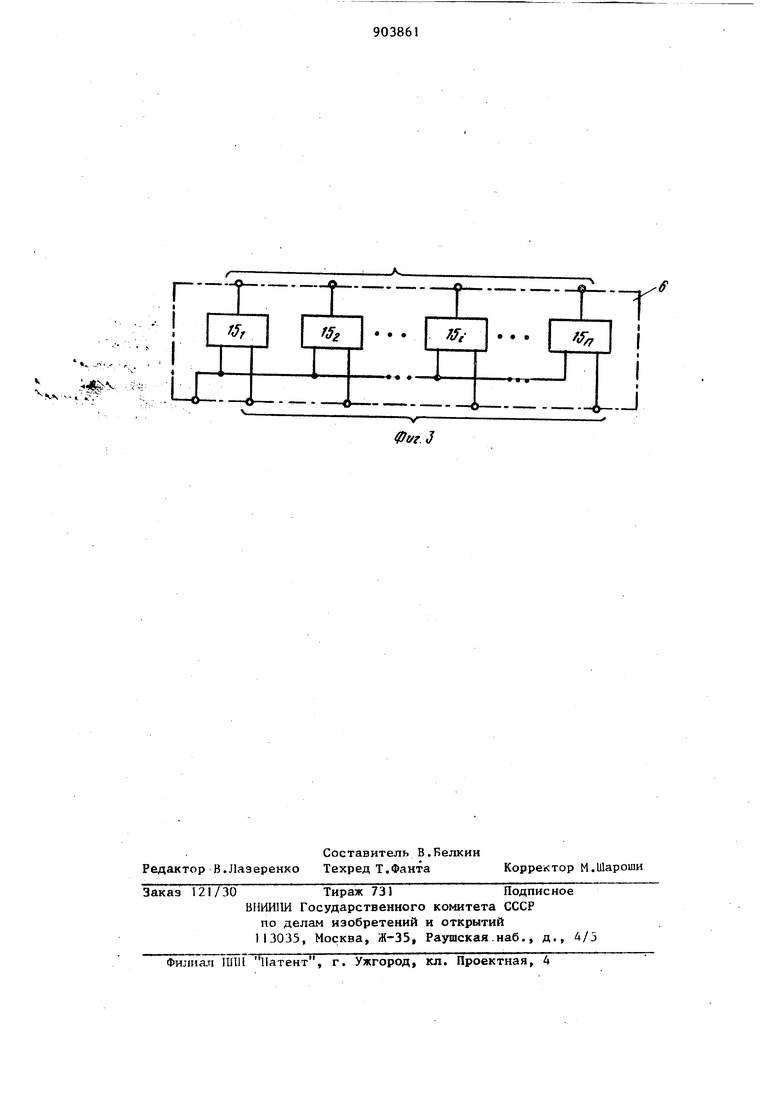

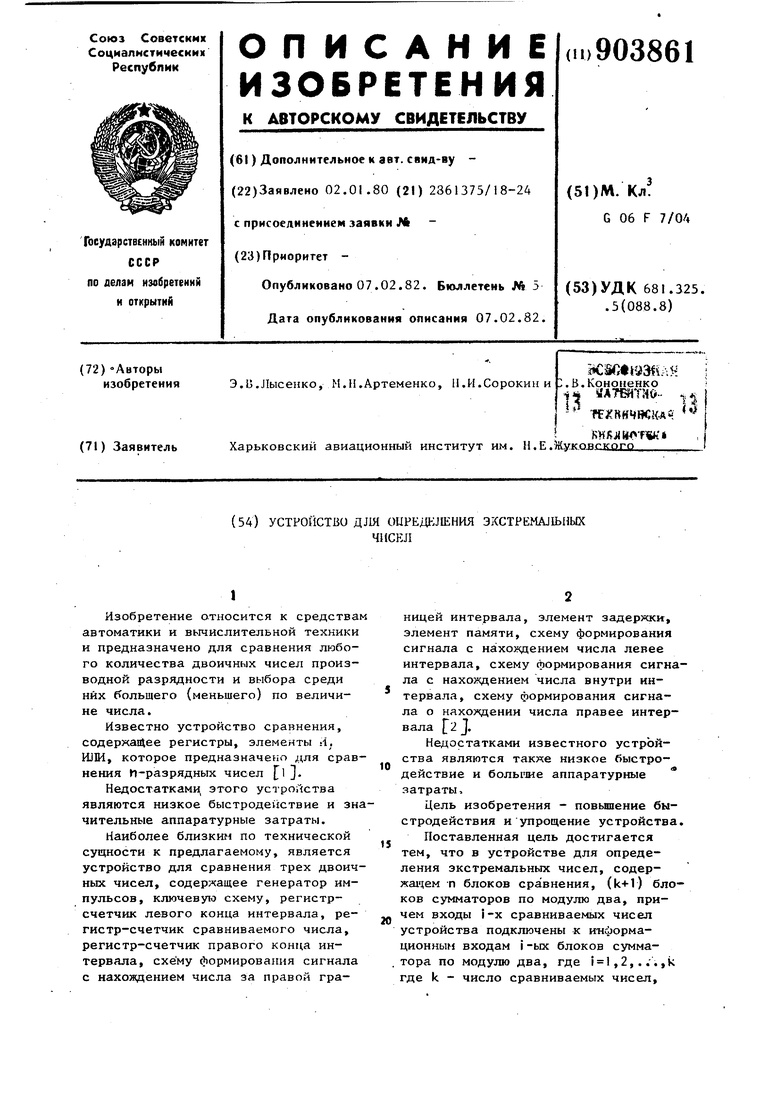

Поставленная цель достигается тем, что в устройстве для определения экстремальных чисел, содержа1чем п блоков сравнения, (k+1) блоков сумматоров по модулю два, причем входы i-X сравниваемых чисел устройства подключены к информационным входам i-ых блоков сумматора по модулю два, где 1 1,2,..-. ,к где k - число сравниваемых чисел. 39 каждый j-ый выход i-ro блока сумматора по модулю два соединен с i-ым информационным входом j-ro бло ка сравнения, где ,2,...,п, п число разрядов в сравниваемых числах, информационный выход каждого j-ro блока сравнения подключен к J-ому информационному входу (k+1)-r блока сумматора по модулю два, уп равляющий вход устройства соединен с управляющими 1входами блоков сумматоров по модулю два, каждый i-ый выход переносов каждого j-ro блока сравнения подключен к 1-ому входу переносов (j+1)-ro блока сравнения При этом каждый блок сравнения состоит из группы элементов И, ИЛИ элемента ШЫ и элемента НЕ, причем каждый I-ый информационный вход бло ка сравнения соединен с первым входом i-ro элемента И первой группы, выход каждого из которых подключен к 1-ому входу элемента ИЛИ, выход которого соединен с информационным выходом блока, и через элемент НЕ - к первым входам элементов ИЛИ группы, выход каждого i-ro из которых соединен с каждым первым входом i-ro элемента И второй группы, каждый i-ый выход переносов блока подключен ко вторым входам .i -ых элементов И первой и второй групп, выход каждого i-го элемента И второй группы соединен с t-ым выходом переносов блока, Кроме того, каждый блок суммато ров по модулю два содержит И сумматоров по модулю, два, причем управляющий BxoflT блока соединен с первыми входами сумматоров по моду лю два, каждый J-ый информационный вход блока подключен ко второму вх ду j-ro сумматора по модулю два, выход какцого J-ro из которых соединен с J-biM выходом блока. На фиг. 1 представлена блок-схе ма 5 на фиг. 2 - функциональная схема блока сравнения; на фиг. 3 схема блока сумматоров по одулю два. Устройство содержит входные шины 1 сигналов переноса, выходные шины 2 сигналов переноса, выходные Бшны устройства 3, управляющий вход 4, блоки 5, 52...,, сравнения, блоки 6,, .6 ... ,6|, h, сумматоров по модулю два, входные шин устройства 7 (фиг. 1), блок 5 срав нения состоит из группы элементов И 8,, 8,...,8j;, элемент ШМ 9, элен мент hii 10, группы элементов IlJBi J 1 1 Ig,, . .., 1 1((, группы элементов И 12,j, .. ., 1 2 (, входные шин блока 13, выходы .блока 14. Каждый из блоков 6 сумматоров по модулю два (фиг. З) состоит из сумматоров 15, 15,,... J 15, по модулю два. Устройство работает следующим образом. Допустим, что сравниваемые числа поступают по входным шинам 7 (фиг. 1)о Далее по шинам сравниваемых чисел разряды каждого числа поступают на вторые входы блоков Ь., б,...,6 сумматоров по модулю два. В то не время ria управляющий вход 4 поступает сигнал, который имеет нулевой потенциал при выборе устройства большего (максимального (числа из всех сравниваемых чисел или единичный потенциал при выборе меньшего (минимального) числа. Этот управляющий сигнал поступает на первые входы всех блоков сумматоров по модулю два. Рассмотрим.j-e сравниваемое число о Первый разряд j-ro сравниваемого числа поступает н второй вход первого элемента сумматора 15 по модулю два (фиг. З)о Второй разряд j-ro сравниваемого числа поступает на второй вход второго элемента сумматора 15 по модулю два 1-ь;й разряд j-ro сравниваемого числа поступает на второй вход i-го элемента сумматора 15 по модулю два. Последний п-ьй разряд j-ro сравниваемого числа поступает на второй вход последнего п-го элемента сумматора 15 по модулю два. На первые входы всех элементов сумматор по модулю два поступает управляющий сигнал. При нулевом потенциале управляющего сигнала на выходе элементов сумматор помодулю два фор- . мируются разряды сравниваемого числа без изменений. При единичном потенциале управляющего сигнала на выходе элементов сумматор по модулю два формируются инвертированные значения разрядов сравниваемого числа. Далее первые разряды всех сравниваемых чисел с блоков сумматоров по модулю два поступают на блок 5 сравнения первых разрядов (фиг. 1)с Сюда же поступа1 т сигналы переноса 1, 1-ые разряды всех сравниваемых чисел поступают с блоков сумматоров по модулю два на блок срав нения 1-ых разрядов. Сюда не посту пают сигналы переноса, вырабатываемые блоками сравнения предыдущих (1-1) разрядов. Работу блока 5 сравнения рассмо рим по структурной схеме на фиг. 2 Допустим, что первые разряды сравниваемых чисел соответственно равн первого числа - 1, второго числа и т.До, j-ro числа - I, и т.д., k-ro числа - О. Эти разряды поступают на входы блока сравнения первых разрядов. На входы блока сравнения первых: разрядов поступают си налы переноса. Таким образом, на вход первого элемента И 8 поступают сигналы первого разряда сравниваемого числа и сигнал переноса И , которые имеют соответственно значения I и 1« На выходе первого элемента И 8 формируется сигнал 1. На вход j-ro элемента И 8 посту пают сигналы первого разряда j-ro сравниваемого числа и сигнал .переноса )1, а именно 1 и 1 . На выходе j-ro элемента И 8 формируется сигнал 1 . С выходом элементов И 8 сигналы 1,0,.о.о..I,,0 поступают на входы элемента ШШ 9. На выходе эл мента ИЛИ 9 формируется при этом сигнал 1, который является результатом сравнения первых разрядов, и поступает соответственно на наруж ный выход 1 - выход результата сравнения первых разрядов Одновременно сигнал с выхода элемента ШЮ 9 поступает на вход элемента НЕ 10, с выхода которого инвертированный сигнал, в данном случае и, поступает на первые входы всех элементов ИЛИ 11. На второй вход первого элемента ИЛИ 11 поступает первый разряд первого сравниваемого числа, имеющий значение 1, который поступает на первы ; вход первого элемента И 12. На второй вход j-ro элемента ИЛИ 11 поступает первый разряд j-ro сравниваемого числа, имеющий значение 1. На выходе j-ro элемента ШШ 1 1 формируется сигнал I, которы поступает на первые входы j-ro элемента И 12. На второй вход j-ro эле мента И поступает сигнал переноса 16 1. На выходе JTO элемента И 12 формируется сигнал переноса I, который поступает на наружный вывод второй группы выходных наружных выводов III и далее на вход сигналов переноса Влока сравнения вторых разрядов. Аналогично происходит сравнение остальных разрядов. Результаты сравнения поступают на вход блока сумматоров по модулю два результата (фиг. 1), а именно, на вторые входы соответствующих элементов сумматоров по модулю два. Результат сравнения первых разрядов поступает на второй чход первого элемента сумматора по модулю два (фиг. З), результат сравнения 1-ых разрядов поступает на второй вход i-го элемента сумматора по модулю два. Устройство для выбора большего (меньшего) числа из произвольного количества двоичных чисел может быть реализовано с помощью интегральной технологии и размещено в стандарт-ном корпусе. Количество выводов за исит от количества сравняваемзтх чисел сел и от разрядности. Устройство позволяет изготавливать отдельные блоки с ограниченным количеством сравниваемых чисел, соединяя которые можно построить устройство для сравнения огГределенного количества чисел произвольной разрядности. Таким образом, предлагаемое устройство обладает высоким быстродействием, поскольку оно является комбинационной схемой и следовательно, все опера1щи производятся за один такт. Быстродействие устройства ограничивается только временныи задержками логических элементов и моАет быть использовано для остроения схем параллельного обмеа информа1щей между любым количетвом каналов ВУ, а также в систеах обработки информации. Использование предлагаемого устойства в различных конструкциях нижает аппаратурные затраты. Формула изобретения 1. УстройсАо для определения кстремальных чисел, содержащее И 7 блоков сравнения, (k+1) блоков сумматоров по модулю два, причем входы i-X сравниваемых чисел устройства подключены к информационным входай j-ых блоков сумматоров по мо дулю два, где i l ,2,, .,, где k число сравниваемых чисел, отли чающееся тем, что, с целью повышения быстродействия и упрощения устройств, в нем каждый j-Ый выход i-го блока сумматора по моду лю два соединен с i-ым информацион ным входом j-ro блока сравнения, где ,2,...,n, п - число разрядоз в сравниваемых числах, информа ционный выход каждого j-ro блока сравнения подключен к j-ому информационному входу (k+1)-ro блока сумматоров по модулю два, управляющий вход устройства соединен с уп раляющими входами блоков сумматоров по модулю два, казедый выход переносов j-ro блока сравнения подключен к I-ому входу переносов (j+1)-го блока сравнения 2. Устройство по п. I, о т л и ч ающе е с я тем, что в нем каждый блок сравнения состоит из группы элементов И, ШШ, элемента йим и элемента НЕ, причем каждый i-ый информационный вход блока сра нения соединен с первым входом f-r 1 элемента И первой группы, выход каждого из которых подключен к i-ому входу элемента ШЫ, выход которого соединен с информационным выходом блока, и через элемент НЕ - к первым входлм элементов ИЛИ группы, выход каждого i-ro из которых соединен с первы;-4 входом i-ro элемента И второй группы, кахдый i-ый вход переносов блока подключен ко вторьм входам i-ых эигсментов И первой и второй групп, выход каждого i-ro элемента И второй группы соединен с 1-ым выходом переносов блока. Зо Устройство по п. 1, отличающееся тем, что в нем каждый блок сумматоров по модулю два содержит п сумматоров по модулю Два, причем.управляющий вход блока соединен с первыми входами сумматоров по модулю два, каждый j-ый информационный вход блока подключен ко второму входу j-ro сумматора по модулю два, выход каждого j-ro из которых соединен с j-ым выходом блока. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР № 478302, кл. G 06 F 7/04, 1963. 2.Авторское свидетельство СССР № 310246, кл. G 06 F 7/00, 1963 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для выбора экстремальногочиСлА | 1977 |

|

SU809163A1 |

| Устройство для определения среднего из трех чисел | 1977 |

|

SU717758A1 |

| Устройство для сравнения двух п-разрядных чисел | 1979 |

|

SU864280A1 |

| Устройство для умножения @ -разрядных двоичных чисел | 1990 |

|

SU1783519A1 |

| Устройство для вычисления суммы квадратов К @ -разрядных чисел | 1981 |

|

SU993256A1 |

| Устройство для сравнения чисел | 1980 |

|

SU949651A1 |

| Устройство для сортировки чисел | 1990 |

|

SU1795449A1 |

| Устройство для вычисления логарифмов чисел | 1980 |

|

SU932491A1 |

| Устройство для умножения чисел с плавающей запятой | 1985 |

|

SU1280624A1 |

| Цифровой анализатор спектра в ортогональном базисе | 1983 |

|

SU1124326A1 |

-Т

Т I-iL «I

«iiv

Г

VK -.

I

ц-т

fffi

f

« -1

..J

фуг J

Авторы

Даты

1982-02-07—Публикация

1980-01-02—Подача