11

Изобретение относится к вычислительной технике и может быть использовано при построении арифметических устройств с плавающей запятой быстродействующих вычислительных машин.

Цель изобретения - повышение быстродействия.

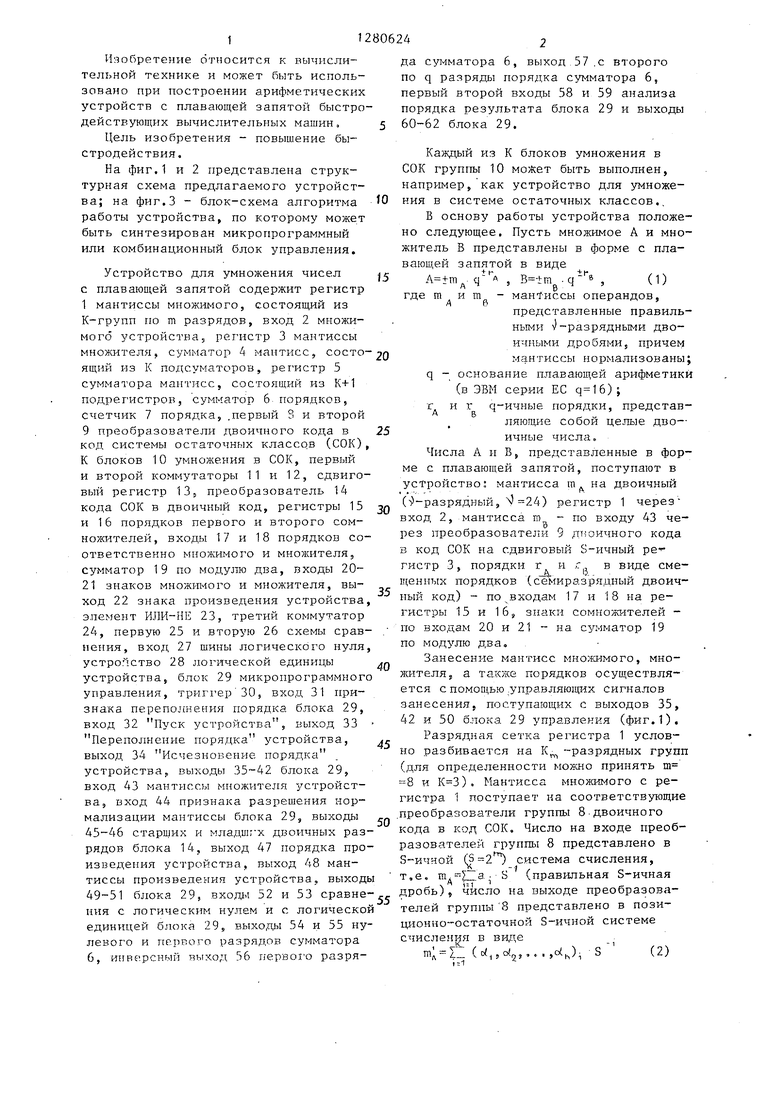

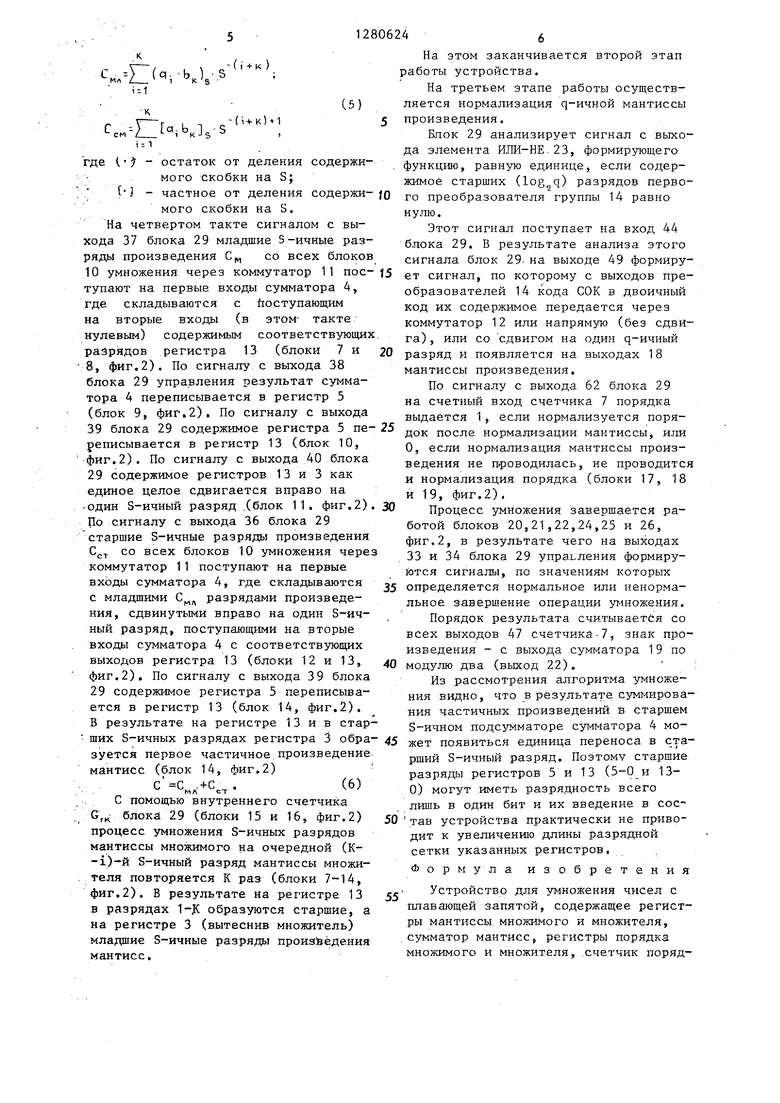

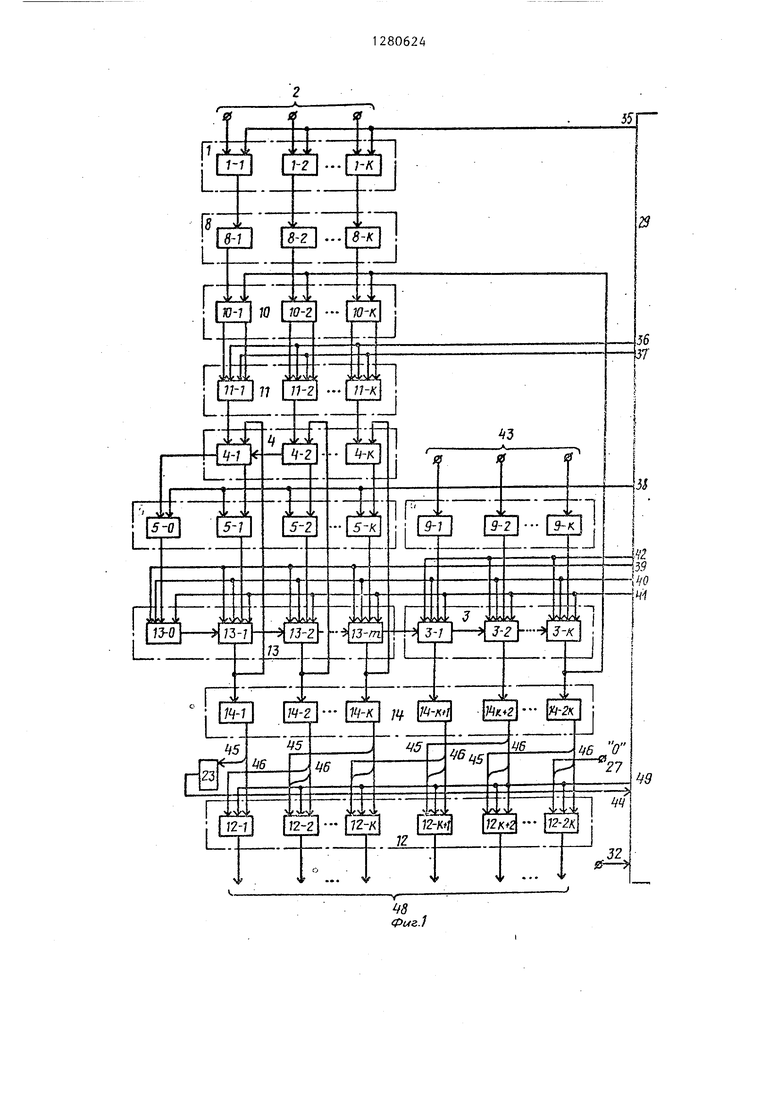

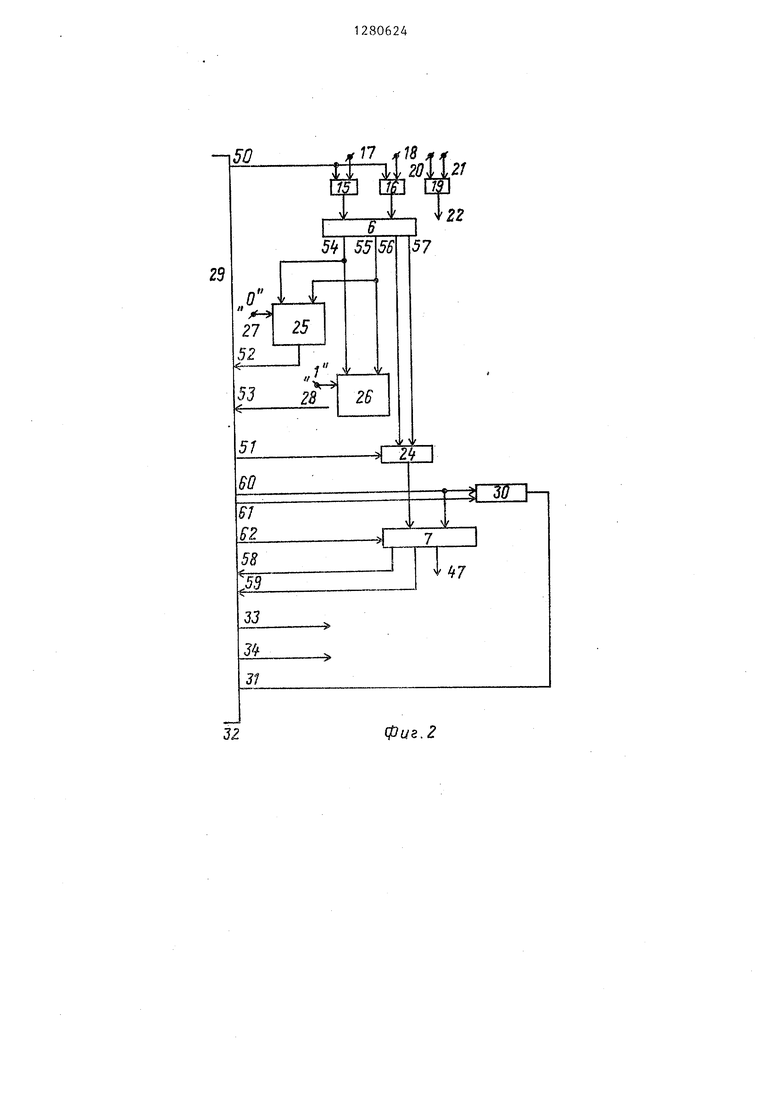

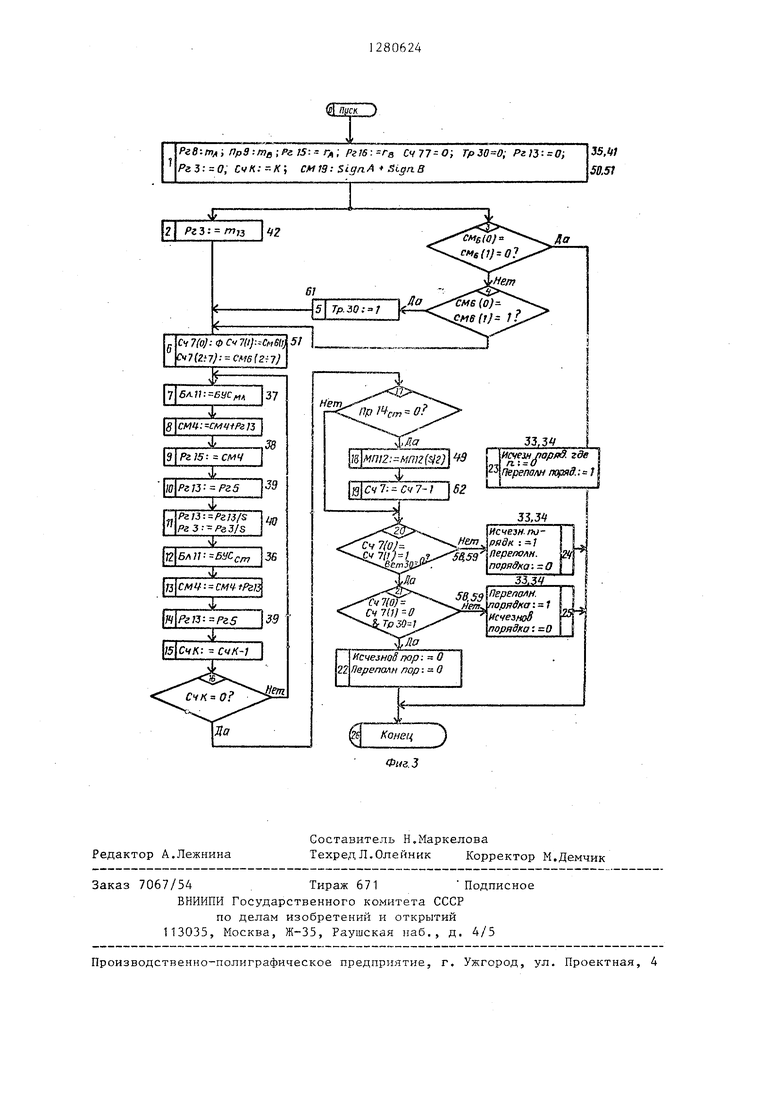

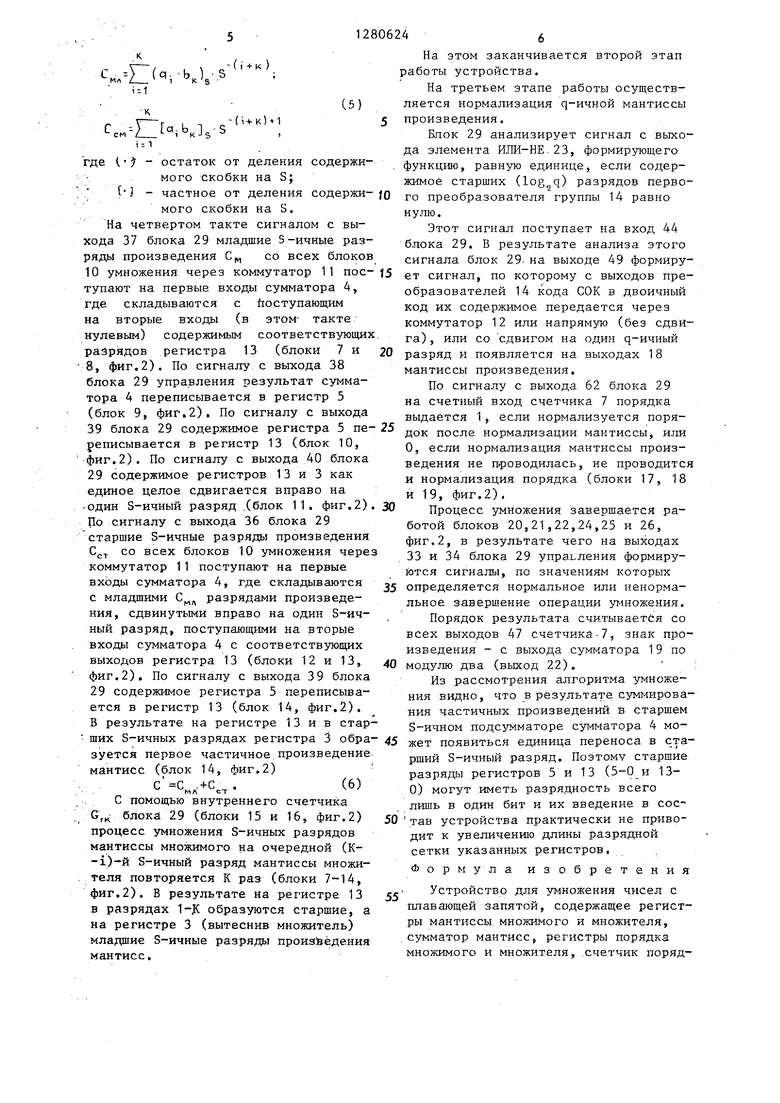

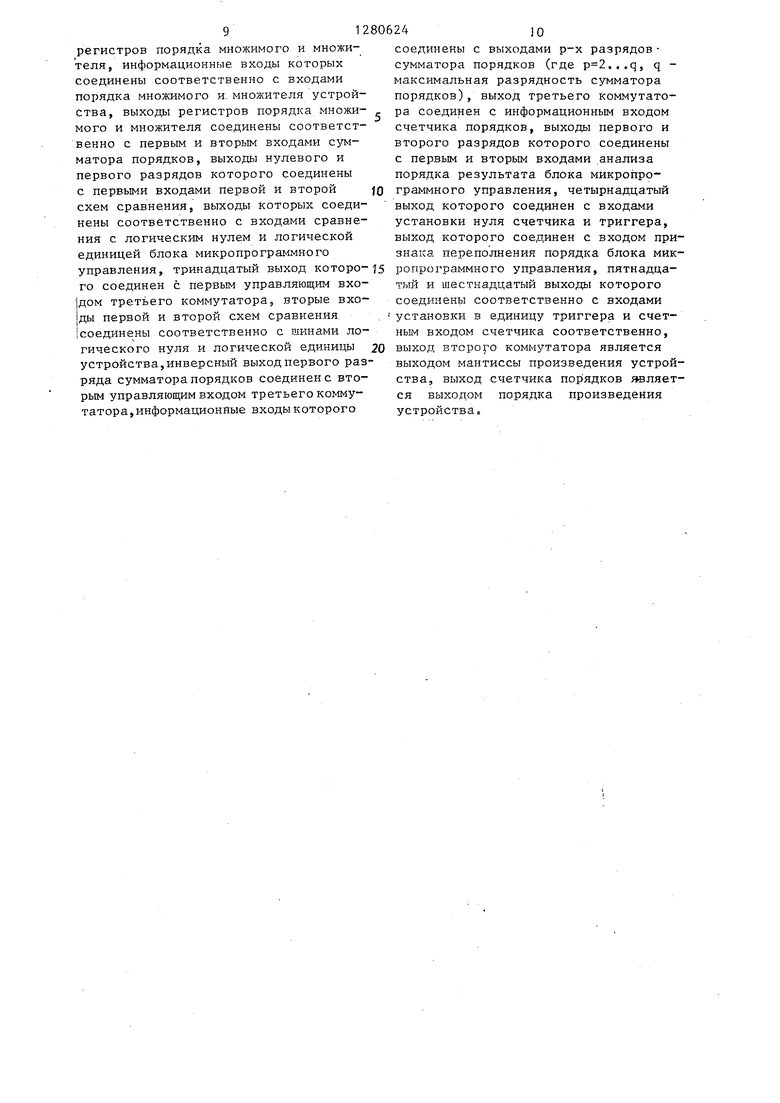

На фиг,1 и 2 представлена структурная схема предлагаемого устройства; на фиг.З - блок-схема алгоритма работы устройства, по которому может быть синтезирован микропрограммный или комбинационный блок управления.

Устройство для умножения чисел с плавающей запятой содержит регистр 1 мантиссы множимого, состоящий из К-групп по m разрядов, вход 2 множимого устройства, регистр 3 мантиссы множителя, сумматор 4 мантисс, состоящий из К подсуматоров, регистр 5 сумматора мангнсс, состоящий из К+1 подрегистровJ сумматор 6 порядков,

счетчик 7 порядка, .первый S и второй 9 преобразователи двоичного кода в код системы остаточных классов (СОК), К блоков 10 умножения в СОК, первый и второй коммутаторы 11 и 12, сдвиговый регистр 13э преобразователь 14 кода СОК в двоичный код, регистры 15 и 16 порядков первого и второго сомножителей, входы 17 и 18 порядков соЧисла А и В, представленные в фор ме с плавающей запятой, поступают в устройство: мантисса т на двоичный (-разрядный, 24) регистр 1 через вход 2, мантисса го - по входу 43 че рез преобразователи 9 дт оичного кода в код СОК на сдвиговый S-ичный ре- гистр 3, порядки г и г в виде смещенных порядков (с ёмиразрядный двоич код)

45

ответственно множимого и множителя, сумматор 19 по модулю два, входы 20- 21 знаков МНОЖ1-ШОГО и множителя, выход 22 знака произведения устройства, код) - по входам 17 и 18 на ре- элемент ИЛИ-НЕ 23, третий коммутатор гистры 15 и 16, зпаки сомножителей - 24, первую 25 и вторую 26 схемы срав- / нения, вход 27 шины логического пуля, устройство 28 логической единицы д устройства, блок 29 микропрограммного управления, триггер 30, вход 31 признака перепо.чнения порядка блока 29, вход 32 Пуск устройства, выход 33 Переполнение порядка устройства, выход 34 Исчезновение порядка устройства,, выходы 35-42 блока 29, вход 43 мантиссы мпож 1теля устройства, вход 44 признака разрешения нормализации мантиссы блока 29, выходы 45-46 старщих и младшг х двоичных разрядов блока 14, выход 47 порядка произведения устройства, выход 48 мантиссы произведения устройства, выходы

49-51 блока 29, входы 52 и 53 сравне-„ ДРобь), число на выходе преобразования с логическим нулем и с логической телей группы 8 представлено в пози- единицей блока 29, выходы 54 и 55 нулевого и первого разрядов сумматора 6, инверсный выход 56 первого разря50

по входам 20 и 21 - на сумматор 19 по модулю два.

Занесение мантисс мно 31мого, множителя, а также порядков осуществляется с помощью ,управляю цих сигналов занесения, поступающих с выходов 35, 42 и 50 блока 29 управления (фиг.1).

Разрядная сетка регистра 1 условно разбивается на К -разрядных групп (для определенпости можно принять т 8 и ), Мантисса мнояшмого с регистра 1 поступает на соответствующие .преобразователи группы 8-двоичного кода в код СОК, Число на входе преобразователей группы 8 представлено в S-ичной (2 система счисления.

т.е.

m... S ч

(правильная S-ичная

ционно-остаточной S-ичной системе

счисления в виде

- (с/,,Ы,2,,..,Ы,), s (2)

4да су1-1матора 6, выход.57.с второго по q разряды порядка сумматора 6, первый второй входы 58 и 59 анализа порядка результата блока 29 и выходы 60-62 блока 29.

Каждый из К блоков умножения в СОК группы 10 может быть выполнен, например,, как устройство для умножения в системе остаточных классов.,

В основу работы устройства положено следующее. Пусть множимое А и множитель В представлены в форме с плавающеи запятой в виде

. , q

А

где m и m д 6

- манТиссь операндов,

представленные правильными i -разрядными двоичными дробями, причем мантиссы нормализованы; q - основание плавающей арифметики (в ЭВМ серии ЕС );

г, и г

А Б

q-ичные порядки, представляющие собой целые дво-- ичные числа.

Числа А и В, представленные в форме с плавающей запятой, поступают в устройство: мантисса т на двоичный (-разрядный, 24) регистр 1 через вход 2, мантисса го - по входу 43 через преобразователи 9 дт оичного кода в код СОК на сдвиговый S-ичный ре- гистр 3, порядки г и г в виде смещенных порядков (с ёмиразрядный двоичНЬ Й код)

код) - по входам 17 и 18 на ре- гистры 15 и 16, зпаки сомножителей -

5

код) - по входам 17 и 18 на ре- гистры 15 и 16, зпаки сомножителей - / д

„ ДРобь), число на выходе преобразователей группы 8 представлено в пози-

0

по входам 20 и 21 - на сумматор 19 по модулю два.

Занесение мантисс мно 31мого, множителя, а также порядков осуществляется с помощью ,управляю цих сигналов занесения, поступающих с выходов 35, 42 и 50 блока 29 управления (фиг.1).

Разрядная сетка регистра 1 условно разбивается на К -разрядных групп (для определенпости можно принять т 8 и ), Мантисса мнояшмого с регистра 1 поступает на соответствующие .преобразователи группы 8-двоичного кода в код СОК, Число на входе преобразователей группы 8 представлено в S-ичной (2 система счисления.

т.е.

m... S ч

(правильная S-ичная

ДРобь), число на выходе преобразов телей группы 8 представлено в пози

ционно-остаточной S-ичной системе

ДРобь), число на выходе преобразователей группы 8 представлено в пози-

счисления в виде

- (с/,,Ы,2,,..,Ы,), s (2)

4где otj(j i,n) - остатки от деления

S-ичной цифры на основании Р СОК; п - количество оснований СОК.

Основания СОК выбираются из условия:

2S.(3)

Аналогично для мантиссы множителя можно записать (на входе и выходе

преобразователей группы 9): к к

, . -Ct.P.- b-s (

,--1 .

где р - остатки от деления S-ичной цифры р. на основания СОК.

Таким образом, произведен переход от представления мантисс множимого и множителя в двоичной системе счисления к представлению в позиционно-ос- таточной S-ичной системе счисления. С увеличением S количество К 3 ичных разрядов для представления одного и того же числа уменьшается и, следовательно, уменьшается длина распространения сигнала переноса.

Работа устройства происходит в соответствии с блок-схемой алгоритма, представленной на фиг.З, и начинается подачей сигнала Пуск на первый вход 32 блока 2.9 (блок О, фиг.2).

По сигналам с выходов 35, 41, 50, блока 29 управления в регистр 1

51

заносится мантисса множимого m (блок 1, фиг.2). Мантисса множителя (без управляющего сигнала) поступает на выходы преобразователей 9, появляясь к второму такту на их выходах в виде позиционно-остаточного S-ично- го- кода. На регистры 15 и 16 заносятся порядки сомножителей, обнуляются регистры 13 и 3, триггер 30, счетчик 7 порядка; внутренний счетчик блока 29 управления СЧК устанавливается в К-ое положение. Он является счетчиком цикла (счетчиком количества S-ичных разрядов мантисс сомножителей). Знаки сомножителей поступают на сумматор 19, где складываются по модулю два.

Порядки с регистров 15 и 16 поступают на входы сумматора (двоичного) 6, где складываются. Нулевой и первый разряды сумматора 6 поступают на вход первой 25 и второй 26 схем сравнения, которые проверяют их равенство нулям илк единицам, и на выходах формируют

функции лг, л г, значе

ния которых через входы 52 и 53 поступают в блок 29 управления. Одновременно содержимое сумматора 6 (кроме

нулевого разряда, а первый разряд - инверсный) поступает на входы коммутатора 24.

На втором такте работы блок 29 управления формирует сигнал на своем Десятом выходе 42, по которому в регистр 3 заносится позиционно-остаточ- ный код мантиссы множителя (блок 2, фиг.2). К этому моменту двоичный код мантиссы множимого, пройдя через преобразователи 8, в виде позиционно- остаточного кода поступает на первые входы блоков умножения группы 10, на вторые входы которых поступает содер- жимов младшей (правой) группы регистра 3 (младший S-ичный разряд позици- онно-остаточного кода мантиссы множителя) . На втором же такте в блоке 29 управления производится анализ сигналов с выходов схем 25 и 26 срав

нения (блоки 3 и 4, фиг.2). Если f , то блок 29 вырабатывает на своих выходах 33 и 34 соответственно

1 ,, Q

сигналы 1

что свидетельству

ет об отрицательном переполнении порядка, и работа устройства прекращается (выход на блоки 23 и 26, фиг.2), Если , то осуществляется переход к началу третьего такта (блок 6, фиг.2). Если f выхода 61 вырабатывается сигнал, переключающий триггер 30 в единичное положение (блок 5, фиг.2). и осуществляется переход к началу третьего такта (на блок 6, фиг.2).

На третьем такте сигналом с выхода 51 блока 29 управления (блок 6, фиг.2) коммутатор 24 открывается по вторым входам, и на счетчик 7 переписывается содержимое сумматора 6: инверсия с первого разряда и прямой код со всех остальных разрядов, кроме нулевого. Нулевой разряд счетчика 7 остается в нулевом положении.

На этом заканчивается подготовительный этап и начинается собственно этап перемножения мантисс, включающий Q блок 7-16, фиг.2. Выполняется эта совокупность блоков К раз до обнуления внутреннего счетчика блока 29 управления СЧК,

К началу третьего такта блоки умножения группы 10 на своих первых и вторых выходах имеют результат умножения всех S-ичных разрядов мантиссы множимого на младший З-ичный разряд мантиссы множителя в виде5

Ил--Г ГЬк)зi--1

CcH--ii:t ibj.s

5

- (i + к )

t

-(i-t-Kl + l

i 1

12806246

Ha этом заканчивается второй этап работы устройства.

На третьем этапе работы осуществ- (5) ляется нормализация q-ичной мантиссы 5 произведения.

Блок 29 анализирует сигнал с выхода элемента ИЛИ-НЕ.23, формирующего функцию, равную единице, если содергде ( У - остаток от деления содержимого скобки на S;

Ч - частное от деления содержи-jо го преобразователя группы 14 равно

мого скобки на S. На четвертом такте сигналом с выхода 37 блока 29 младшие S-ичные разряды произведения С„ со всех блоков

10 умножения через коммутатор 11 пос- |5 ет сигнал, по которому с выходов пре- тупают на первые входы сумматора 4, образователей 14 кода СОК в двоичный

жимое старших (log q) разрядов первонулю.

Этот сигнал поступает на вход 44 блока 29. В результате анализа этого сигнала блок 29- на выходе 49 формиругде складываются с поступающим на вторые входы (в этом- такте нулевым) содержимым соответствующих, разрядов регистра 13 (блоки 7 и 20

8, фиг.2). По сигналу с выхода 38 блока 29 управления результат сумматора 4 переписывается в регистр 5 (блок 9, фиг.2), По сигналу с выхода 39 блока 29 содержимое регистра 5 пе- 25 реписывается в регистр 13 (блок 10,

фиг.2). По сигналу с выхода 40 блока

код их содержимое передается через коммутатор 12 или напрямую (без сдвига) , или со сдвигом на один q-ичный разряд и появляется на выходах 18 мантиссы произведения.

По сигналу с выхода 62 блока 29 на счетный вход счетчика 7 порядка выдается 1, если нормализуется порядок после нормализации мантиссы, или О, если нормализация мантиссы произведения не п-роводилась, не проводится и нормализация порядка (блоки 17, 18 и 19, фиг.2).

29 содержимое регистров 13 и 3 как единое целое сдвигается вправо на -один S-ичный разряд .(блок 11. фиг.2). По сигналу с выхода 36 блока 29 старшие S-ичные разряды произведения С,;. со всех блоков 10 умножения через коммутатор 11 поступают на первые входы сумматора 4, где складываются с младшими С разрядами произведения, сдвинутыми вправо на один S-ичный разряд, поступающими на вторые входы сумматора 4 с соответствующих выходов регистра 13 (блоки 12 и 13, фиг.2), По сигналу с выхода 39 блока 29 содержимое регистра 5 переписывается в регистр 13 (блок 14, фиг.2). В результате на регистре 13 и в стар

Из рассмотрения алгоритма умножения видно, что в результате суммирования частичных произведений в старшем S-ичном подсумматоре сумматора 4 мо ших S-ичных разрядах регистра 3 обра- 45 жет появиться единица переноса в cja- зуется первое частичное.произведение. р S-ичный разряд. Поэтому старшие мантисс (блок 14, фиг.2) разряды регистров 5 и 13 (5-0 и 130) могут иметь разрядность всего лишь в один бит и их введение в сое- 50

С с..

(6)

с помощью внутреннего счетчика G; блока 29 (блоки 15 и 16, фиг.2) процесс умножения S-ичных разрядов мантиссы множимого на очередной (К- -1)-й S-ичный разряд мантиссы множителя повторяется К раз (блоки 7-14, фиг.2). В результате на регистре 13 в разрядах 1-jK образуются старшие, а на регистре 3 (вытеснив множитель) младшие S-ичные разряды произведения мантисс.

55

тав устройства практически не приводит к увеличению длины разрядной сетки указанных регистров,

Формула изобретения

Устройство для умножения чисел с плавающей запятой, содержащее регистры мантиссы, множимого и множителя, сумматор мантисс, регистры порядка множимого и множителя, .счетчик порядго преобразователя группы 14 равно

жимое старших (log q) разрядов первоет сигнал, по которому с выходов пре- образователей 14 кода СОК в двоичный

нулю.

Этот сигнал поступает на вход 44 блока 29. В результате анализа этого сигнала блок 29- на выходе 49 формиру

код их содержимое передается через коммутатор 12 или напрямую (без сдвига) , или со сдвигом на один q-ичный разряд и появляется на выходах 18 мантиссы произведения.

По сигналу с выхода 62 блока 29 на счетный вход счетчика 7 порядка выдается 1, если нормализуется порядок после нормализации мантиссы, или О, если нормализация мантиссы произведения не п-роводилась, не проводится и нормализация порядка (блоки 17, 18 и 19, фиг.2).

Процесс умножения завершается работой блоков 20,21,22,24,25 и 26, фиг.2, в результате чего на выходах 33 и 34 блока 29 упраьления формируются сигналы, по значениям которых определяется нормальное или ненормальное завершение операции умножения.

Порядок результата считывается со всех выходов 47 счетчика-7, знак произведения - с выхода сумматора 19 по модулю два (выход 22). ;

Из рассмотрения алгоритма умножения видно, что в результате суммирования частичных произведений в старшем S-ичном подсумматоре сумматора 4 может появиться единица переноса в cja- р S-ичный разряд. Поэтому старшие разряды регистров 5 и 13 (5-0 и 130) могут иметь разрядность всего лишь в один бит и их введение в сое-

тав устройства практически не приводит к увеличению длины разрядной сетки указанных регистров,

Формула изобретения

Устройство для умножения чисел с плавающей запятой, содержащее регистры мантиссы, множимого и множителя, сумматор мантисс, регистры порядка ножимого и множителя, .счетчик порядков, сумматор по модулю два, блок микропрограммного управления., регистр сумматора мантисс, причем вход регистра мантиссы множимог о является входом множимого устройства, первый и второй входы сумматора по модулю два являются входами знаков множимого и множителя устройства, выход сумматора по модулю два является выходом знака произведения устройства, выход сумматора мантисс соединен с информа- .ционным входом регистра сумматора ... мантисс, отличающееся тем, что, С целью повышения быстродействия, в него введены два преобра- 5 гистра сдвига, вход разрешения запизователя двоичного кода в код системы остаточных- классов, преобразователь кода системы остаточных классов в двоичный код, К блоков умножения в системе остаточных классов, где К - разрядность сомножителей, три коммутатора, регистр сдвига, ..элемент ИЖ- НЕ , сумматор порядков, две схемы сравнения и триггер, причем первый и

второй выходы блока микропрограммного 5 ля, выход (i-l)-ro разряда регистра

управления являются выходами соответственно переполнения порядка и исчезновения порядка устройства, третий выход блока микропрограммного управления соединен .с входом разрешения записи регистра мантиссы множимого, выход которого соединен с входом первого преобразователя двоичного кода в код системы остаточных классов, i-й выход которого (где ,...K) соединен с первым входом i-ro блока умножения в системе остаточных классов, второй вход которого соединен с выходом К-го разряда регистра мантиссы множителя, информационный вход i-ro разряда которого соединен с выходом i-ro разряда второго преобразователя двоичного кода в код остаточных классов,вход которого является входом множителя устройства, выходы младших и старших разрядов i-ro блока умножения соединены с первым и вторым информационными входами соответственно первого коммутатора, первый и второй управляющие входы которого соединены с четвертым и пятым выходами соответственно блока микропрограммного управления, i-й выход первого коммутатора соединен с первым информационным вхо- ,дом i-ro разряда сумматора мантисс, второй информационный вход которого соединен с выходом i-ro разряда регистра сдвига и входом i-ro разряда преобразователя кода системы остаточных классов в двоичный код, вход j-ro разряда которого (где , К+2, ,,., 2К) соединен с выходом i-ro разряда регистра мантиссы множителя, выход i-ro разряда сумматора мантисс соединен с информационным входом i-ro разряда регистра сумматора мантисс, информационный вход нулевого разряда которого соединен с выходом переноса сумматора мантисс, шестой выход блока микропрограммного управления соединен с входом разрешения записи регистра сумматора мантисс, выход которого соединен с информационным входом реси которого соединен с седьмым выходом блока микропрограммного управле- ния, восьмой и девятый выходы которого соединены с входами разрешения 20 сдвига и сброса соответственно регистров сдвига и мантиссы мнолсителя, десятый выход блока микропрограммного управления соединен с входом разрешения записи регистра мантиссы множитесдвига соединен с информационным входом сдвига i-ro разряда регистра сдвига, выход К-го разряда которого соединен с информационным входом сдвига регистра мантиссы множителя, выход i-ro разряда которого соединен с информационным входом сдвига (i+ +1)-го разряда регистра мантиссы множителя выходы младших двоичных разрядов 1-го З-ичного разряда, (где 1 1,2,,,.,2К, S -основание системы остаточных классов) преобразователя кода системы остаточных классов в двоичный код с первым информационным входом 1-го разряда второго коммутатора, вход управления которого соединен с одиннадцатым выходом блока микропрограммного управления, выход старших двоичных разрядов т-го S-ич- ного разряда (где ,3,...,2К) соединен с вторьм информационным входом (m-l)-ro разряда второго коммутатора информационный вход (2К)-го разряда которого соединен с шиной логическог нуля устройства, выход старших двоичных разрядов первого S-ичного разряда преобразователя кода системы остаточных классов в двоичный код соединен с входом элемента ШТИ-НЕ, выход которого соединен с входом признака разрешения нормализации мантиссы блока микропрограммного управления, двенадцатый выход которого соединен с входами разрешения записи ререгистров порядка множимого и множителя, информационнЕле входы которых соединены соответственно с входами порядка множимого и. мнонсителя устройства, выходы регистров порядка множи- мого и множителя соединены соответственно с первым и вторым входами сумматора порядков, выходы нулевого и первого разрядов которого соединены с первыми входами первой и второй схем сравнения, выходы которых соединены соответственно с входами сравнения с логическим нулем и логической единицей блока микропрограммного

управления, тринадцатый выход которо J5ропрограммного управления, пятнадцаго соединен с первым управляющим вхо-тый и шестнадцатый выходы которого

|дом третьего коммутатора, вторые вхо-соединены соответственно с входами

|ды первой и второй схем сравнения, . установки в единицу триггера и счет соедине ны соответственно с шинами ло-ным входом счетчика соответственно,

гического нуля и логической единицы 20выход второго коммутатора является

устройства,инверсный выход первого раз-выходом мантиссы произведения устройряда сумматора порядков соединен с ВТО-ства, выход счетчика порядков являетрым управляющим входом третьего комму-ся выходом порядка произведения

татора,информационные входы которогоустройства

соединены с выходами р-х разрядов- сумматора порядков (где ...q, q - максимальная разрядность сумматора порядков), выход третьего коммутатора соединен с информационным входом счетчика порядков, выходы первого и второго разрядов которого соединены с первым и вторым входами анализа порядка результата блока микропрограммного управления, четырнадцатый выход которого соединен с входами установки нуля счетчика и триггера, выход которого соединен с входом признака переполнения порядка блока микi nzTl I I I I «Л I I

32

0H

8 Фиг. }

Фиг.2

РгВ-.тл; ПрЗ:тв;Рг}5- ГА; Рг б:-га , Cv«. СМ 19: Sign А Sign. В

| название | год | авторы | номер документа |

|---|---|---|---|

| Арифметическое устройство | 1984 |

|

SU1236473A1 |

| Специализированный процессор | 1983 |

|

SU1144117A1 |

| Устройство для умножения | 1984 |

|

SU1233136A1 |

| Устройство для умножения | 1987 |

|

SU1495785A1 |

| Преобразователь двоичных чисел в двоично-десятичные числа | 1980 |

|

SU941990A1 |

| Вычислительное устройство | 1988 |

|

SU1545215A1 |

| Преобразователь двоично-десятичногоКОдА B дВОичНый КОд | 1979 |

|

SU809151A1 |

| Устройство для обработки данных | 1985 |

|

SU1287146A1 |

| Устройство для умножения | 1989 |

|

SU1672441A1 |

| Устройство для умножения | 1984 |

|

SU1226447A1 |

Изобретение относится к вычисли- тельной технике и может быть использовано при построении быстродействующих арифметических устройств современных ЭВМ., Цель изобретения - повышение быстродействия;i Заявляемое устройство содержит регистры мантисс МНОЖИМОГО и множителя, состоящее из К групп по m разрядов; первую и вто- рую группы из К преобразователей двоичного кода в код СОК, группу из К блоков умножения, три коммутатора, су№-1атор мантисс, состоящий из под- сумматоров; регистр сумматора мантисс, состоящий из К+1 групп; сдвиго- вьш регистр, состоящий из подре- гистров; группу из 2К преобразователей кода СОК в двоичный код; элемент ИЛИ-HEj блок микропрограммного управления, регистры порядков мнояотмого и мно.жителя, сумматор по модулю два, сумматор порядков, дйе схемы сравнения, триггер и счетчик порядка. 2 ил.

Редактор А.Лежнина

Составитель Н.Маркелова

Техред Л.Оленннк Корректор М.Демчик

Заказ 7067/54Тираж 671 Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

| Каган Б.М | |||

| Электронные вычислительные машины и системы, М.: Энергия, 1979, с | |||

| Приспособление для подачи воды в паровой котел | 1920 |

|

SU229A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-12-30—Публикация

1985-07-01—Подача