(54) УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ЛОГАРИФМОВ

ЧИСЕЛ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для определения закона распределения случайной величины | 1987 |

|

SU1425715A1 |

| Множительно-делительное устройство | 1980 |

|

SU920712A1 |

| Устройство для вычисления показательно-степенной функции | 1980 |

|

SU920717A1 |

| Устройство для извлечения квадратного корня | 1982 |

|

SU1084788A1 |

| Функциональный преобразователь | 1983 |

|

SU1136154A1 |

| Устройство для вычисления логарифмачиСлА | 1979 |

|

SU849210A1 |

| Устройство для спектрального анализа | 1984 |

|

SU1241256A1 |

| Устройство для решения систем алгебраических уравнений | 1982 |

|

SU1088007A1 |

| Универсальное суммирующее устройство | 1990 |

|

SU1786484A1 |

| Устройство для формирования адресов процессора быстрого преобразования Фурье | 1983 |

|

SU1080149A1 |

1

Изобрегение огносигся к вычислительвой технике и можег быть использовано в состаье универсальных вычислительных ма, шин или специализированных вычислительных устройств для вычисления с высокой точностью и быстродействием логарифмов чисел с произвольным основанием, например, в системах автоматического управления динамическими объектами.

Известно устройство, содержащее ре-. гисгр результата, счетчик с управляемым козф(|ициентом пересчета, коммутатор, два блока памяти, три счетчика, элементы ИИЛИ, причем второй вход первого блока памяти соединен с входом второго блока 15 памяти, выход которого подключен к первой группе входов элементов И-ИЛИ, вторая группа входов которого соединена с выходами первого счетчика, подключенного свсим входом к выходу счетчика с уп- 20 равляемым коэффициентом пересчета fll.

Недостатком устройства является точность из-за необходимости реализации лусочно линейной апроксимацки, низкое быстродействие, определяемое необходамостью организации пересчета коэффициентов, и относительная сложность, определяемая наличием двух блоков памяти.

Наиболее близким к предлагаемому по технической сущности является устройство, содержащее регистр числа, первый и второй регистры реЕ(ультатов, накопите г, б л (Ж у правления,, эле менты И, ИЛИ, схему сравнения, блок деления, кольцевой сдвигающий регистр, причем первые входы элементов ИЛИ первой группы являются информационными входами устройства, вторые входы подключены к соответствующим выходам блока деления, а вькоды - к соответствующим входам регистра числаГ2.

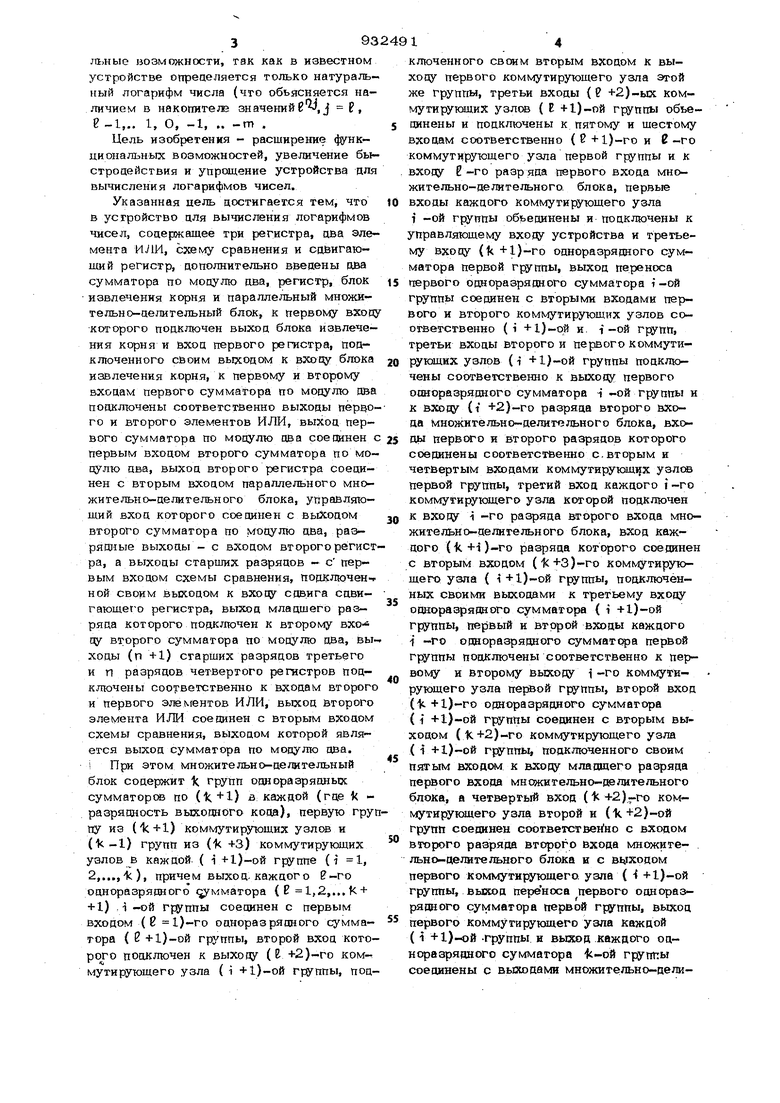

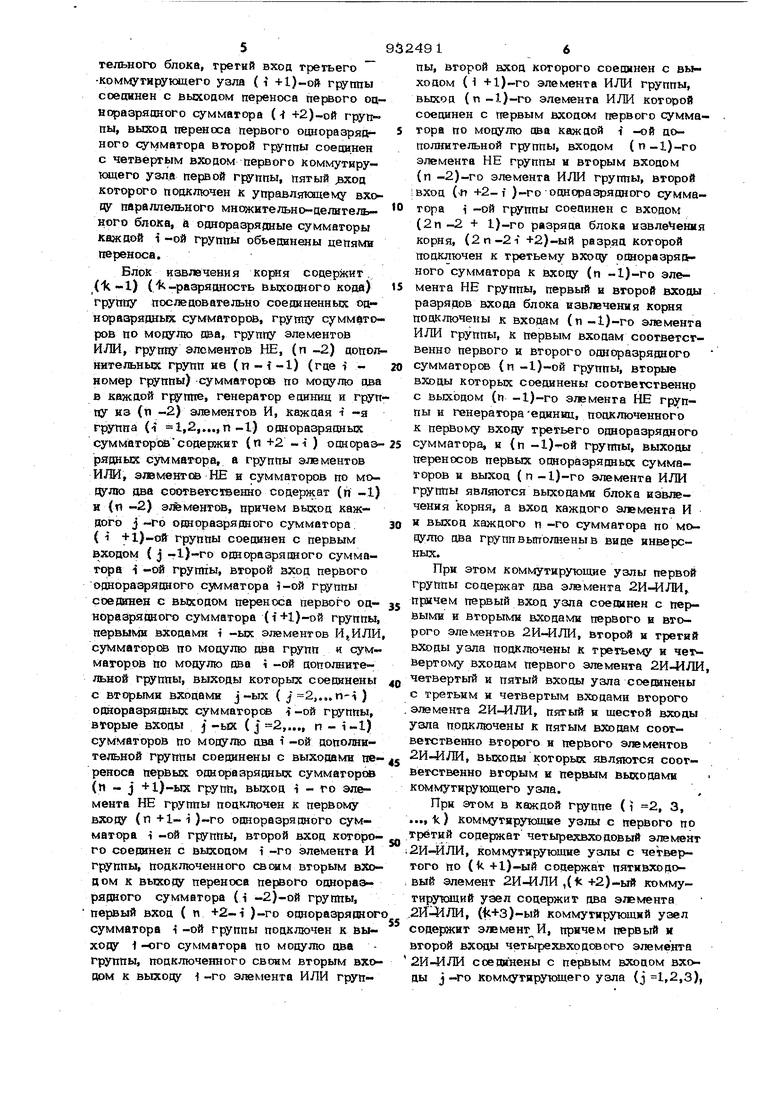

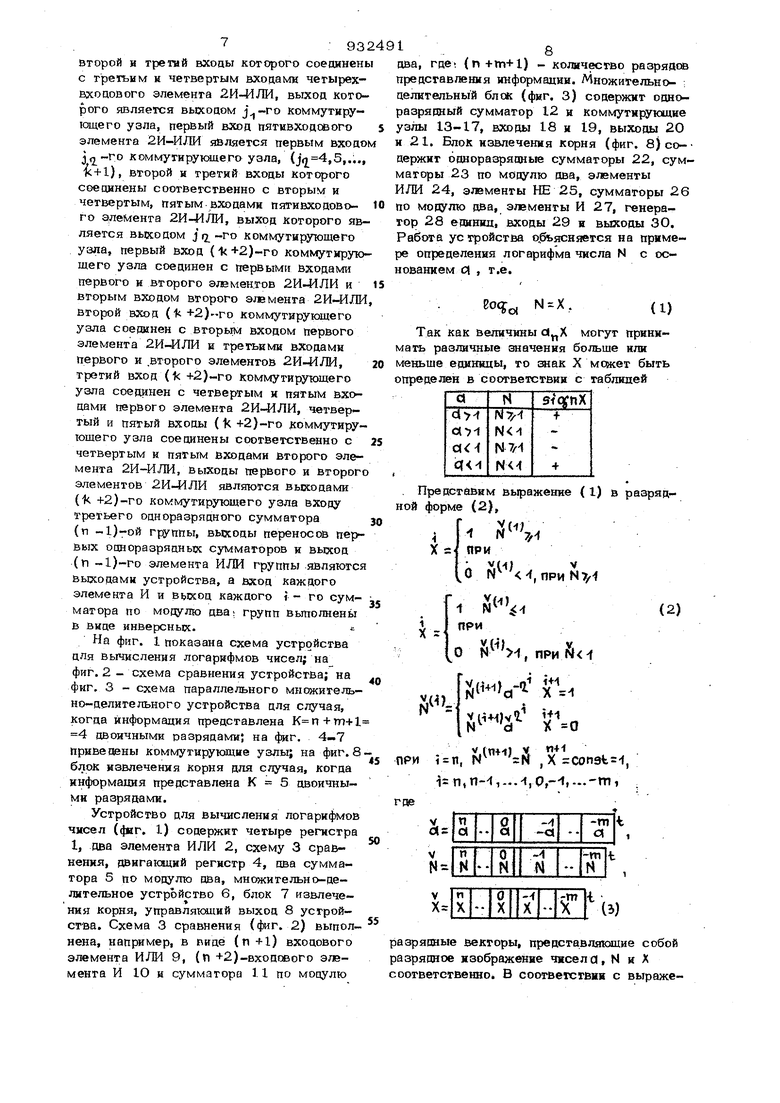

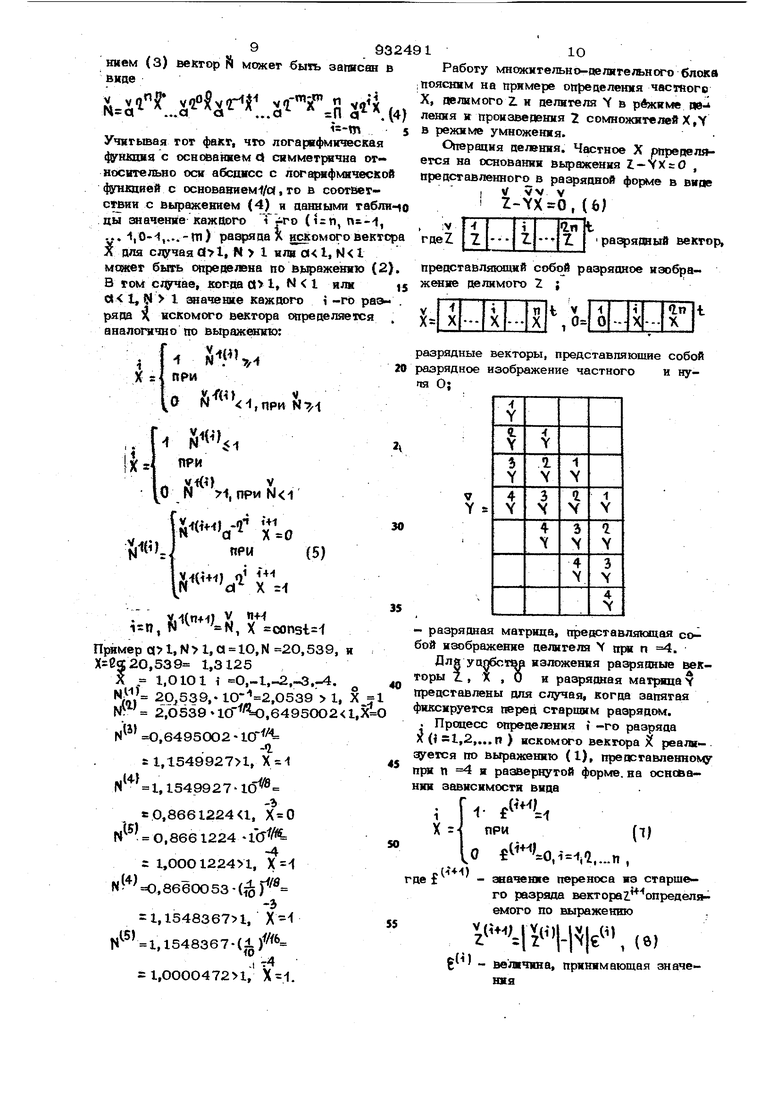

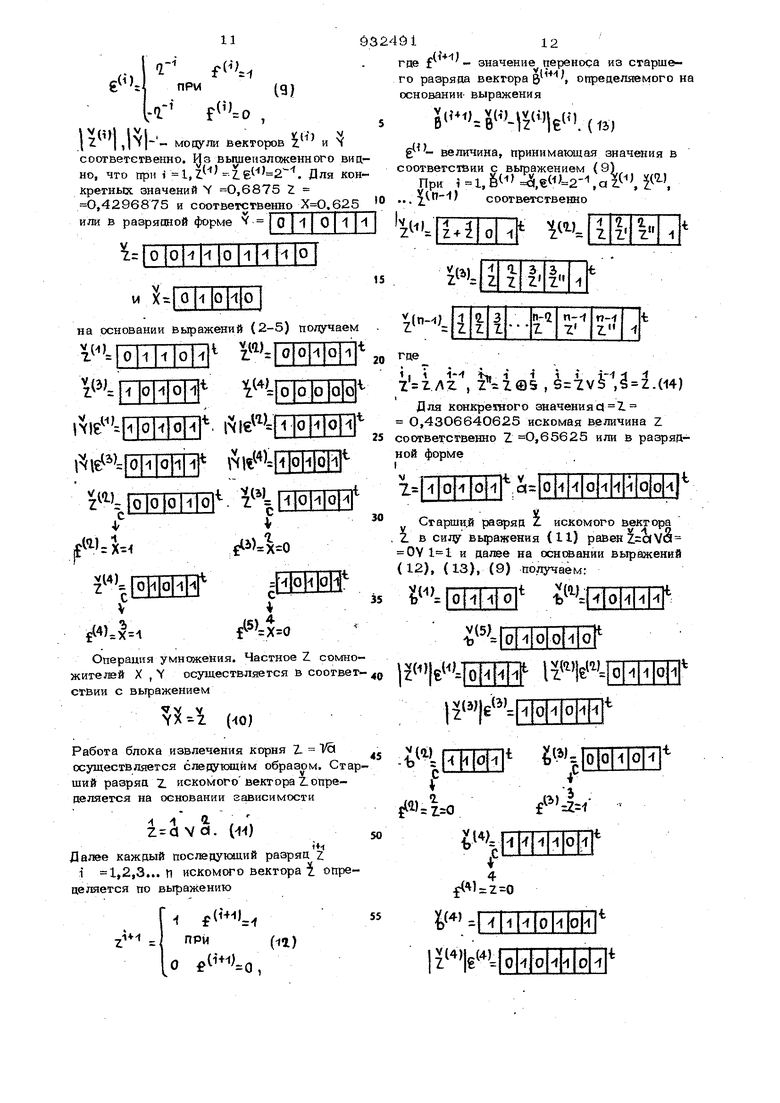

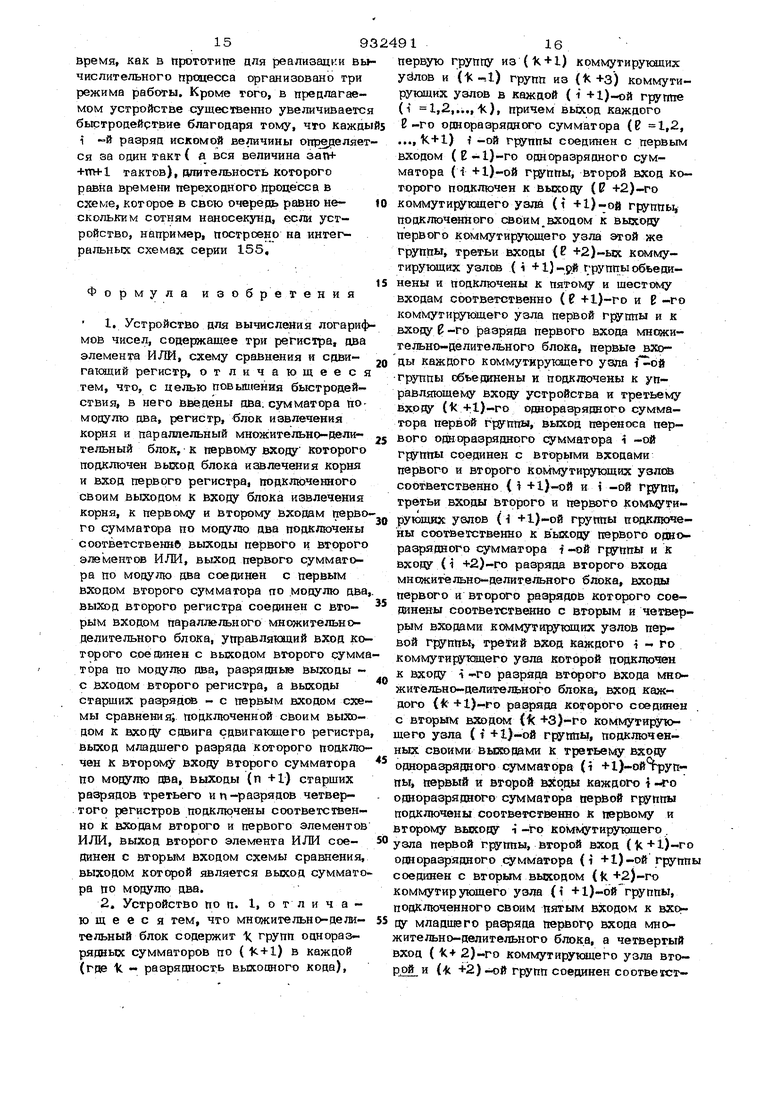

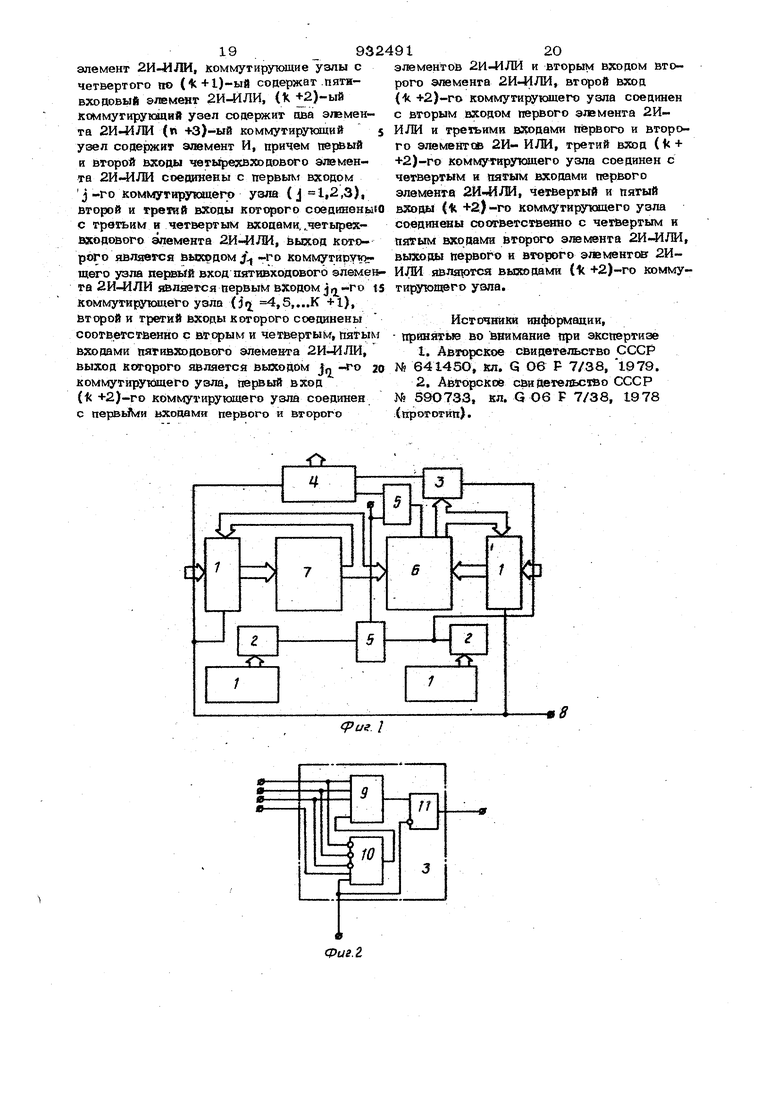

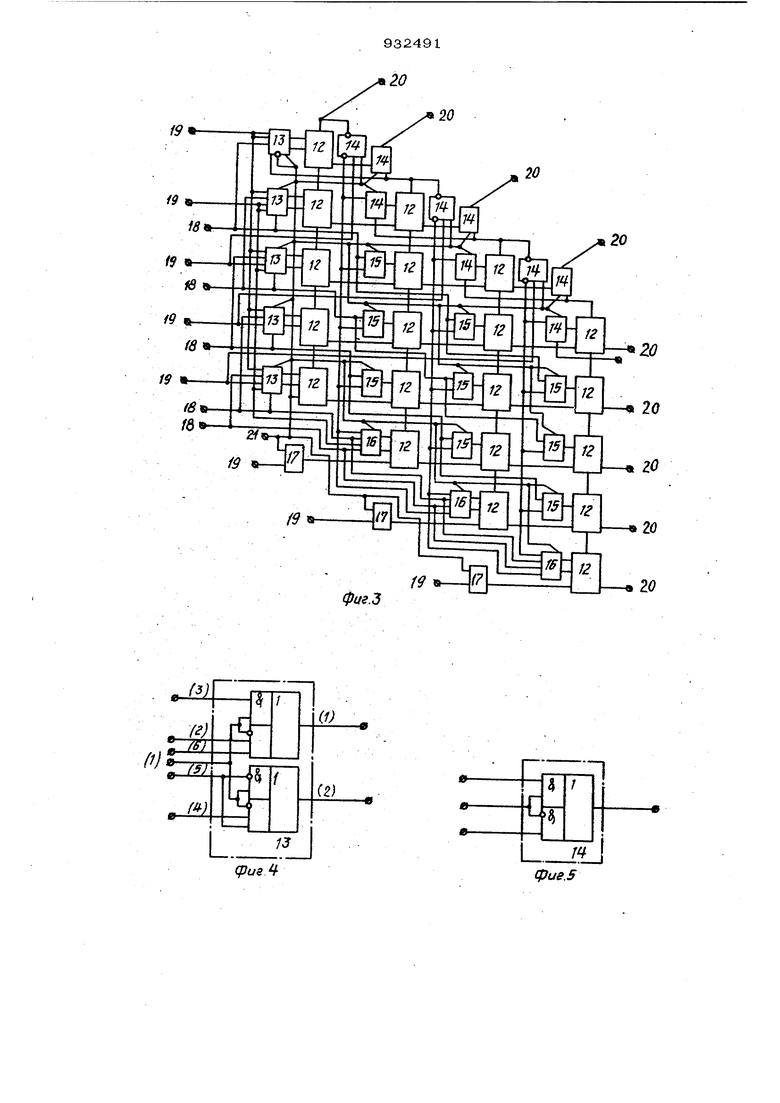

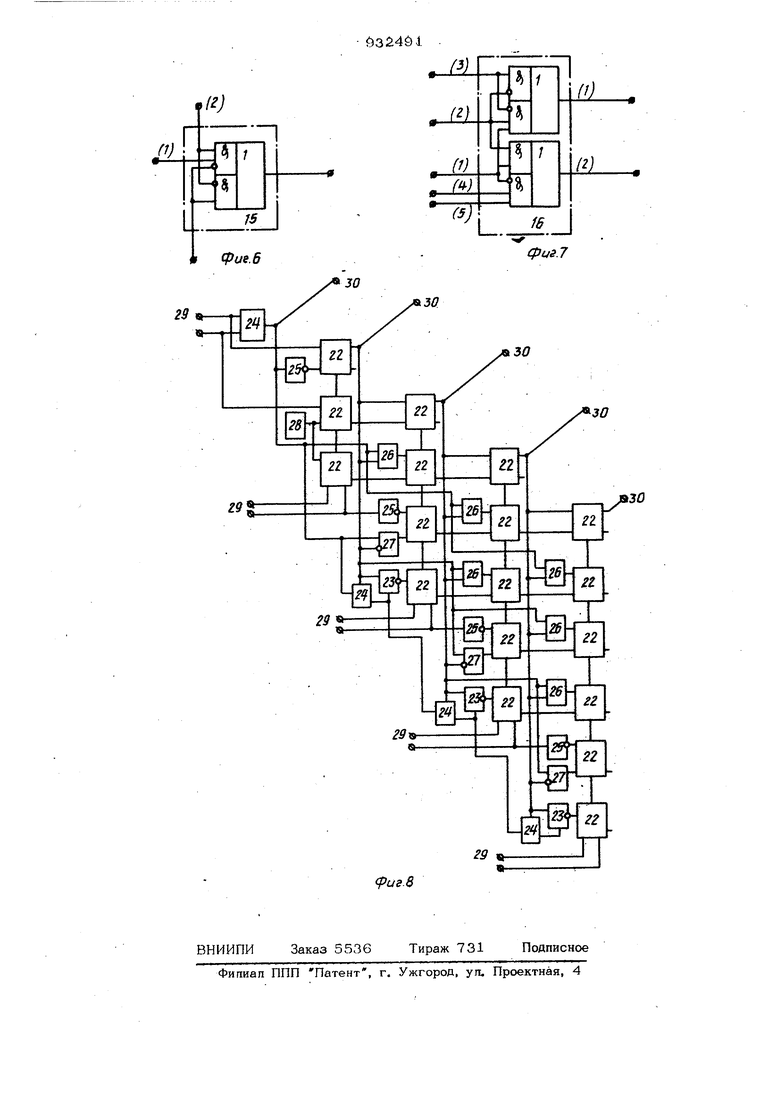

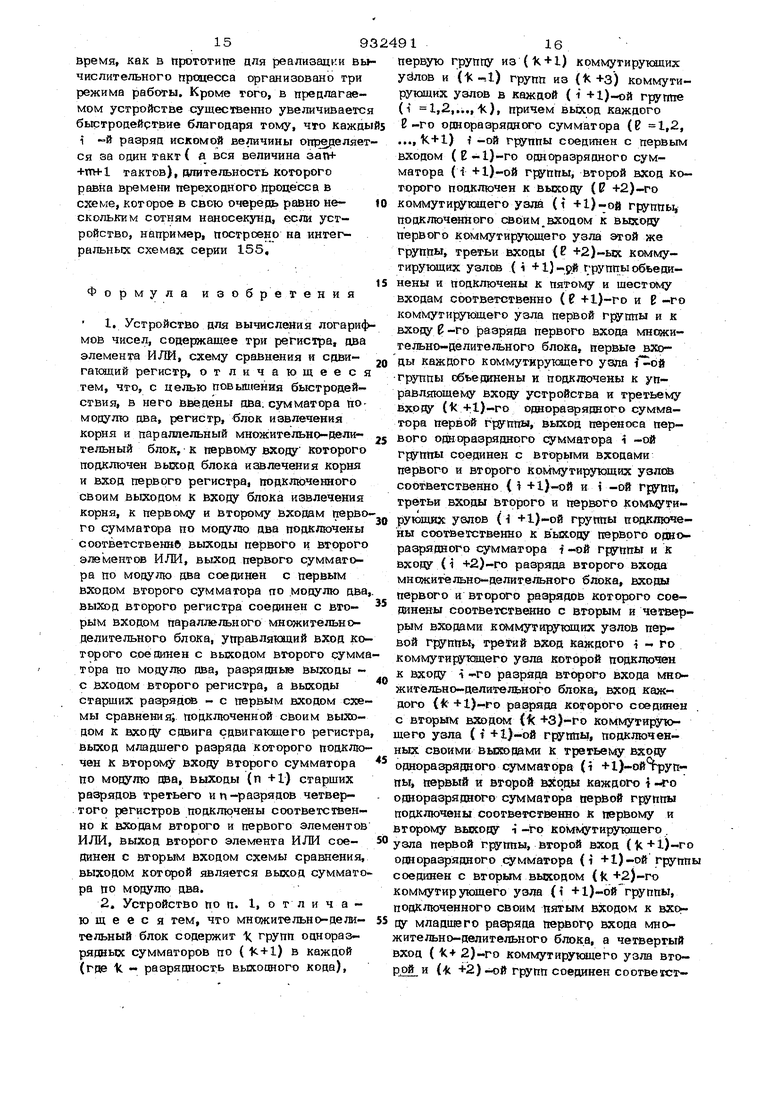

Недостатком известного устройства является относительная сложность, определяемая необходимостью работы устройства в трех режимах, а также наличие накопителя, низкое быстродействие, определяемое необходимостью реализации в каждом из (Р+т) тактов определенного количества микрогактов, ограниченные функционат иые возможности, гак как в извесгном устройсгве опрецеляется только натураль пый логарифм числа (что объясняется наличием в накопителэ значений,J Р, Е -1,.. 1, О, -1, .. -т . Цель изобретения - расширение функциональных возможностей, увеличение быстродействия и упрощение устройства для вычисления логарифмов чисел. Указанная цель достигается тем, что в устройство для вычисления логарифмов чисел, содержащее три регистра, два элемента ИЛИ, схему сравнения и сдвигающий регистр, дополнительно введены два сумматора по модулю два, регистр, блок извлечения корня и параллельный множите льно-целительный блок, к первому вход которого подключен выход блока извлечения корня и вход первого регистра, подключенного своим выходом к входу блока извлечения корня, к первому и второму входам первого сумматора по модулю два подключены соответственно выходы перво го и второго элементов ИЛИ, выход первого сумматора по модулю два соеоинен первым входом второго сумматора по модулю два, выход второго регистра соединен с вторым входом параллельного множительно-делительного блока, управляющий вход которого соединен с выходом второго сумматора по модулю два, разрядные выходы - с входом второго регист ра, а выходы старших разрядов - с первым входом схемы сравнения, подключен- ной своим выходом к BXotC сдвига сдвигающего регистра, выход младшего разряда которого подключен к второму вхо- цу второго сумматора по модулю два, вы ходы (п +1) старших разрядов третьего и п разрядов четвертого регистров подключены соответственно к входам второго и первого элементов ИЛИ, выход второго элемента ИЛИ соединен с вторым входом схемы сравнения, выходом которой является выход сумматора по модулю два. При этом множительно-делительный блок содержит 1(. групп одноразрядных сумматоре© по (1с+1) в; каждой (где k разрярность выходного кода), первую гру пу из () коммутирующих узлов и (1 -1) групп из (k 43) коммутирующих узлов в каждой. ( i +1)-ой группе (i 1, 2,...,k), причем выход, каждого Р-го одноразрядного ф мматора (,2,...К + + 1) ,1 -ой группы соединен с первым входом ( б 1)-го одноразрядного сумматора ( 2 +1)-ой группы, второй вход которого подключен к выходу (Е +2)-го коммутирующего узла ( i +1)-ой группы, подключенного своим вторым входом к выходу первого коммутирующего узла этой же группы, третьи входы ( Р +2)-ых коммутирующих узлсю ( Е +1)-ой группы объединены и подключены к пятому и шестому входам соответственно (С+1)-го и 2-го коммутирующего узла первой группы и к входу Е -го раар яда первого входа множительно-делительного. блока, первые входы каждого коммутирующего узла 1 -ой группы объединены и подключены к управляющему входу устройства и третьему вхооу (1 +1)-го одноразрядного сумматора первой группы, выход переноса первого одноразрядного сумматора i-ой группы соединен с вторыми входами первого и второго коммутирующих узлов соответственно (i +1)-ой и. i-ой групп, третьи входы второго и первого коммутирующих узлов (i +1)-ой группы подключены соответственно к выходу первого одноразрядного сумматора i -ой группы и к вуюау (i +2)-го разряда второго входа Множительно-делительного блока, входы первсго и второго разрядов которого соединены соответственно с.вторым и четвертым входами коммутирующих у злее первой группы, третий вход каждого i-го коммутирующего узла которой подключен к BXoty i -го разряда второго входа множите льно-делнте ьного блока, вход каждого (1с +i)-го разряда которого соединен с вторым входом ({с+3)-го коммутирующего узла ( 1+1)-ой группы, подключённых своими выходами к третьему входу одноразрядного сумматора ( i +1)-ой группы, первый и второй входы каждого 1 -го одноразрядного сумматора первой группы подключены соответственно к первому и второму выходу i-го коммутирующего узла первой группы, второй вход (It +1)-го одноразрядного сумматора ( 1 +1)-ой группы соединен с вторым выходом (lt+2)-ro коммутирующего узла ( i -И)-ой группь подключенного своим пятым входом к вхоцу младшего разряда первого входа множительно-делительного блока, а четвертый вход (14+2)-го коммутирующего узла второй и ()-ой групп соединен соответственно с входом второго разряда второго входа множительно-делительного блока и с выходом первого коммутирующего, узла ( i +1)-ой группы, выход переноса первого одноразрядного сумматора первой группы, выход первого Коммутирующего узла каждой (i -1-1)-ой -группы и выход каждого одноразрядного сумматора -k-oft группы соединены с выходами множительно-делительного блока, третий вход третьего коммутирующего узла ( i +1)-о группы с выхоцом переноса первого оцноразряоного сумматора (-t +2)-ой , выход переноса первого оцноразряриного сумматора второй группы соединен с четвертым входом первого коммутирующего узл.а первой группы, пятый Jвxoд которого подключен к управляющему вхоцу параллельного множнтельно-целительного блока, а одноразрядные сумматоры каждой i -ой группы обьеиннены цепями переноса. Блок извлечения корня содержит. ,(4-1) (Л-разрядность выходного кода) группу последовательно соединенный одноразрядных сумматоров, группу сумматоров по модулю два, группу элементов ИЛИ, группу элементов НЕ, (п -2) дополнительньвс групп ив (n-i-1) (где i номер группы) сумматоров по модулю два в каждой группе, генератор единиц и груп пу из (п -2} элементов И, каждая -t -я группа (i l,2,.,.,n-1) одноразрядных суммагорсйсодержит (п +2 -i ) ооноразрядных сумматора, а группы элементов ИЖ, эшментш НЕ и сумматоров по модулю два соответстеенно содержат (п -1) и (я -2) элементов, причем выход каждого j -го одноразрядного сумматора, ( +1)-ой группы соединен с первым входом ( j -1)-го одноразряпного сумматора i -ой группы, второй аход первого одноразрядного сумматора i-ой группы соединен с выходом переноса первого одноразрядного сумматора ()-ой группы, первыми входами t -ых элементов И,,ИЛИ сумматоров по модулю два групп и сумматоров по модулю два i -ой дополнительной группы, выходы которых соединены с вторыми входами j-ых ( / 2,... n-i ) одноразрядных сумматоров i -ой группы, вторые входы j -ых ( j 2,..,, п - i-1) сумматоров по модулю два i -ой дополнительной группы соединены с выходами tieреяоса первых одноразрядных сумматорш (п - j +1)-ых групп, выход i - го элемента НЕ группы подключен к первому Bxofv (п +l-i)-ro одноразрядного сумматора i -ой группы, второй вход которого соединен с выходом i -го элемента И группы, подключенного своим вторым входом к выходу переноса первого одноразрярного сумматора {i -2)-ой группы, первый вход ( п +2-1 )-го одноразрядног сумматора i -ой группы подключен к выхоцу i -юго сумматора по модулю два группы, подключенного своим вторым BXt дом к вых.оду 1 -го элемента ИЛИ груп4916пы, второй вход которого соединен с выходом (1 +1)-го элемента ИЛИ группы, выход (n-l)-ro элемента ИЛИ которой соединен с первым входом первого сумматора по модулю два каждой i -ой дополнительной группы, входом (n-l)-ro элемента НЕ группы и вторым входом (п -2)-го элемента ИЛИ группы, второй вход ( +2-1 )-го одноразрядного суммагора i -ой группы соединен с входом (2п -2 + 1)-го разряда блока извлe eння корня, (2П-2-1 +2)-ый разряд которой подключен к третьему вхооу одноразрядного сумматора к входу (п -1)-го элемента НЕ группы, первый и второй входы разрядов входа блока извлечения корня подключены к входам (n-l)-ro элемента ИЛИ группы, к первым входам соответственно первого и второго одноразрядного сумматоров (п -1)-ой группы, вторые входы которых соединены соответственно с выходом (п -1)-го элемента НЕ группы и генератора единиц, подключенного к первому вхоцу третьего одноразрядного сумматора, и (п -1)т-ой группы, выходы переносов первых одноразрядных сумматоров и выход (п -1)-го элемента ИЛИ группы являются выходами блока извлечения корня, а вход каждого элемента И и выход каждого п -го сумматора по модулю два групп выполнены в виде инверсных. При этом коммутирующие узлы первой группы содержат два элемента 2И-ИЛИ, причем первый вход узла соединен с первыми и вторыми входами первого и второго элементов , второй и третий входы узла подключены к третьему и чет вертому входам первого элемента 2И-ИЛИ, четвертый и пятый входы узла соединены с третьим и четвертым входами второго элемента 2И-41ЛИ, пятый и шестой входы узла подключены к пятым входам соответственно второго и первого элементов , выходы которых являются соответственно вторым и первым выходами коммутирующего узла. При этом в каждой группе (i 2, 3, ...1с) коммутирутощие узлы с первого по Р®™ содержат четырехвходовый элемент , коммутирующие узлы с четвертого по (k +1)-ый содержат пятивход{ вый элемент 2И-ИЛИ ,(1с +2)-ый коммутирующий узел содержит два элемента .21Т-ИЛИ, (4+3)-ый коммутирующий узел содержит элемент И, причем первый к второй входы четырехвходсеого элемента 2И-МЛИ соединены с первым входом входы j-го коммутирующего узла (j 1,2,3), 793 второй и третий входы которого соединены с третьим и четвертым входами четырехвхоцового элемента 2И-ИЛИ, выход которого является выходом коммутиру1сацего узла, первый вход пятивходового элемента 2И-ИЛИ является первым входо jfji-ro коммутирукшега узла, (j(,5,,,., к+1), второй и третий входы которого соединены соответственно с вторым и четвертым, пятым входами пятивходового элемента 2И-.ИЛИ, выход которого являстся выходом коммутирующего узла, первый вход ()-го коммутирующего узла соединен с первыми входашт первого и второго элементов 2И-ИЛИ и вторым входом второго элемента 2И-ИЛИ второй вход ()Го коммутирующего узла соединен с вторьш входом первого элемента 2И-ИЛИ и третьими входами первого и .второго элементов 2И-ИЛИ, третий вход (1 +2)-го коммутирующего узла соединен с четвертым и пятым входами первого элемента 2И-ИЛИ, четвертый и пятый входы (К +2)-го коммутирующего узла соединены соответственно с четвертым и пятым входами второго элемента 2И-ИЛИ, Выходы первого и второго элементов 2И-ИЛИ являются вьгходами (К +2)-го коммутирующего узла входу третьего одноразрядного сумматора (п -1)-ой группы, выходы переносов первых одноразрядных сумматоров и выход (п -1)-го элемента ИЛИ группы являются выходами устройства, а вход каждого элемента И и выход каждого f- го сумматора по модулю два; групп вьтолнены в виде инверсных. На фиг. 1 показана схема устройства для вычисления логарифмов чисел; на фиг. 2 - схема сравнения устройства; на фиг. 3 - схема параллельного множительно-делительного устройства для случая, когда информация представлена K n+m+l 4 двоичными разрядами; на фиг. 4-7 приведены коммутирующие узлы; на фиг.8 блок извлечения корня для случая, когда информация представлена К 5 двоичными разрядами. Устройство для вычисления логарифмов чисел (фиг. 1) содержит четыре регистра 1, два элемента ИЛИ 2, схему 3 сравнения, двигающий регистр 4, два сумматора 5 по модулю даа, множительно-делительное устройство 6, блок 7 извлечения корня, управляющий выход 8 устройства. Схема 3 сравнения (4иг. 2) выполнена, например, в виде (п +1) входового элемента ИЛИ 9, (п +2)-входового эпкмента И 1О и сумматора 11 по модулю 1g два, где- (n+m+1) - количество разрядов представления информации. Множительноцелительный блок (фиг. 3) содержит оцнсм разрядный сумматор 12 и коммутирующие узлы 13-17, входы 18 и 19, выходы 20 и 21. БЛОК извлечения корня (фиг. 8) соцержиг одноразрядные сумматоры 22, сумматоры 23 по модулю два, элементы ИЛИ 24, алименты НЕ 25, сумматоры 26 цо модулю два, элементы И 27, генератор 28 единиц, входы 29 и выходы 30, Работа ус тройства о,бьясняется на примере определения логарифма числа М с основанием с , т.е. Так как величины могут принимать различные значения больше или меньше единицы, то знак X мсисет быть определен в соответствии с таблидей . Представим выражение ( 1) в разрядной форме (2), V(JV N f, . Vfi}V N М, ПРИ х V fm-il У П+т ПРИ i n, N ,Х con3t «, is n, n-t,... , Р,- - Ti 1 где азрядные векгоры, представляющие собой разрядное изображение чисел а, N и X оответственно В соотвегсгвни с выраже99324нкем (3) вектор и может быть загагсан в виде v. Tl . n 5 (4) ...а d ...d -Vn5 Учитьшая TOT факт, что логарифмическая tasoKH с ocHOBaifflieM d симметрична относительно оси абсписс с лог яфмической ф5гнкдией с ocHOBaBHCM-f/cf, то в соответстеии с выражением (4) и оаннымя таблнчо ды значение каждого (i n, nt-f, ... 1,0-4,...-tTi) искомого вектора j{ для , N 1 или 01 I, М I мойсет быть определена по В Ь}ражению (2). В том CflSs ae, когда а 1, N l илиjs 01 i, 51 I алачение каждого -го раэ- . ряда исКомсяо вектора определяется . аналогично по выражению: y.wj. 1-п,.Поопз1И nj:«Mep а I, N I, а lO, N 20,5 XsCj 20,539 1,3125 1,0101 i 0,-l,-2,-3, 2Oj539,« ,0539 (Л - «5«VJj О : С/j i.- e-jV/ -tJ-/ N 27OS39 ),6495O N O,6495O02 1,1549927 1, l,l54 992710 -Ъ t 0,8661224 1. X 0 N 0,866 1224 -l( -4 i l,OOO1224 l, Ni 0,8660053-() -3 1,1548367 1, X 1,1548367-(i) -I l,OOOO472 i, . 1 Работу множительн1 -аелятельного блока поясним на примере О1феаеления частного X, делимого Z и делителя Ч & рАкиме не- ления и произведения 2 сомножителейХ,У в режиме умножения. Операция деления. Частное X рпредел5Н егся на основании выражения I-YX 0 , представленного в разрядной форме в виде I V VV V I ,(бГ разрядный вектор, представлякаций собой разрядное изображение делимого 2 ; азрядные векторы, представпяюшие собой азрядное изображение частного и нупя О; - разрядная матрица, представляющая собой изображение делителя щж п 4. Длй удобства изложения разрядные векторы Z., X , О и разрядная матртща Y представлены для случая, когда запятая фиксируется перед старшим разрядом. . Процесс определения f -го разряда X О 1,2,...п ) искомого вектора X реалиЕ5ется по вырахюнию (1), представленному при п 4 и развернутой форме, на оснсьа- НИИ зависимости вида 1 .0 ...а....п, значение переноса из старшего разряда вектора определяй емого по выражению Ц.-, €, (в) ветчина, принимающая значенияПРИ(9) 1-1- , , модули векторов и соответственно. Из вышеизлсисенного вид. 1 (1) r(i) Л , но, что при t l,.z. Для конкретных значений Ч 0,6875 2 0.4296875 и соответственно ,625 Ю или в разрядной форме т 1 33iE 3iEEH И )х|о|1|о|ф

на основании выражений (2-5) получаем . 7. -01В03 ffl4o|oh|QhlSa fflz| t|o|-t|o|y УЧ|о|о|о|о|о| IXie h|OJ-fiohl . IXie |ОН|ОИ| 25 i igf |oh|Q|i|f xie M loHlohl {o|oio|i1o| 14 Hjohloli 1Ь)ДсО . , . . . у. рИШft5 X 0)М Операция умножения. Частное Z сомножителей X ,У осуществляется ьсоответ- Р ствии с выражением У У V)(Z (40) S;L:.1:.ap-« Работа блока извлечения корня 2- Ici осуществляется бледукшйм образом. Стар- ший разряд Z искомоговектора Zonpeделяется на основании зависимости vet. (-f) Далее каждый последующий разряд z i 1,2,3... n искомого вектора 1 определяется по выражению 1 О , 932

/ ,. 91 где - значение переноса из старшего разряда вектора в определяемого на основании выражения V, (.(«) величина, принимающая значения i соответствии с выражением (9), Й e lLo а .-.- соответственно l гдетЛлГ, Kz05,s vil z.(i4) Для конкретного значенияа 1 0,4306640625 искомая величина z соответственно Z О,65625 или в разрядной форме Старши.й разряд искомого вектора Z в сиду выражения (11) равен (Va OY и далее на оснейании выражений (12), (13), (9) подучаем: « оеШЦ ffl nfflTRt -b №lo|oh|o -То |V(.)jg(3).j ъЧ(10о0 j|oloh|ohr « - LliLLLLJ р г ) -VOEHST ()Л-0 1 4-fhl-i{o|-i oHI 14)U(4) г 5)Л,,. Работа усгройсгва цля вычисления логарифмм чисел происходиг следукадим образом. В исходном состоянии в четвертый регистр 1 заносится основание с и хранится до тех пор, пока вычисляются логарифмы чисел N по данному основанию с Во второй и третий регистры 1 заносится число N , причем в третьем регистре 1 число N хранится в течение цикла работы устройства, т.е. в течение вычисления л{ гарифма. В первый регистр заносится основание а .если вычисляются логарифмы, у которых запятая фиксируется перед старшим разрядом, и d , если запятая фиксируется после (п +1) старших ра&ртдсв. В младший разряд сдвигакшего регистра 4 заносится единица. Далее в устройстве происходит переходной.процесс, после окончания которого на выходах первой и второй элементов ИЛИ 2 оп ределяется больше или меньше единицы основание ct и число N , а на выходе первого сумматора по модулю два обрадуется значение знака вычисляемого погарифма в соответствии с таблицей 1, которое хранится в течение цикла работы и определяет вычислительный процесс по выражению (4) или (5) соответственно, при этом с вькода второго элемента ИЛИ 2 на управляющий вход схвкгы сравнения 3 поступает значение i или О, соогветсгвующее , или N 1, которое шределяет режим работы по верхней или нижней формуле выражения (4) кпя (5). В частном случае, когдаct l на выходе первого сумматора по модулю два образуется сигнал О, соответствук щий положительному значению логарифма, а на выходе второго элемента ИЛИ 2 и соответственно управлякацем входе схемы 3 сравнения сигнал 1, опре деляющий режим работы по верхней формуле Выражения 4. При этом на управляющий выход множительпо-делительного блока 6 будет поступать единичный сигнал, соответствующий операций, на первы вход будет поступать, с выхода блока 7 1 /У, извлечения корня значение О уа , на второй вход из выхода второго регнстра 1 соответственно . В множительн« -делите1К)Ном блоке реали ется. операция деления, а на его выходе образуется значение ,(n+l) старших раарэ дов которого поступает на вход схемы 3сравнения, в которой по выражению (4) определяется значение старшего раз.ряда 7 логарифма. Так заканчивается первый такт работы устройства. Второй такт работы начинается при поступлении на управляющий выход 8 устройства импульса, благодаря котороцу по переднему фронту, в сдвиговом регистре 4осуществляется сдаиг информации, благодаря чему в младший разряд регистра 4 записывается значение л , вычисленного на предыдущем такте, а в первый и второй регистры 1 записываются с выходов соответственно блока извлечения кор- ня 7 и множительно-делительного блока 6 значения d и При этом благодаря тому, что в младшем разряде сдвигового регистра 4 записано значение х, посту|Пающее на второй вход сумматора по модулю два 5, на его выходе появл$йтся сигнал О или единица, который настраиват параллельный множительно-делительный блок 6 на режим умножения или деления соответственно. После этого в устройстве |происходит переходной процесс аналогично вышеописанному, в ре льтате чего на выходе схемы 3 сравнения образуется .значение последующего разряда-х логарифма числа, а устройство roTteo к следующему такту работы. В ре льтате выполнения (П+т+ 1) тактов (т.е. подачи n+trrt-l импульсов на управлякиций выход 8 устройства) в сдвиговом регистре будет записано значение логарифма X числа N по леяному основаниюа, -знак логарифма л при этом определяется значением сигнала на выходе первого сумматора 5 по модулю два в соответствии с таблицей.- Использование новых элементов - двух сумматорш по модулю два, регистра, блока извлечения корня и множительно-делительного устройства, а также наличие новых связей между ними, выгодно отличает предлагаемое устройство, так как в данном устройстве существенно расширяются функциональные возможности, определяющие вычисление логарифма произвапь ного числа по любому оснсеанию, а не только натурального логарифма, как в прототипе, кроме того, предлагаемое устройство существенно и естных ибо в нем не испольдуется блок памяти, а также существенно упрощается организ ия вычислительного процесса, так как для noj yчения (п +Ш + 1)разрядного значения логарифма в предлагаемом устройстве необходимо на управляющий выход 8 устройства подать всего (n+m + l) импульсов, в то 159324 время, как в прототипе для реализации вычислительного процесса организовано три режима работы. Кроме того, в прецлагаемом устройстве сущесгеенно увеличивается быстродействие благодаря тому, что каждыйз i -и разряд искомой величины опререляется за один такт ( а вся величина зап+ +ГГН-1 тактов), длительность которого равна времени переходного процесса в схеме, которое в свою очередь равно нескольким сотням наносекунд, если устройстЕо, например, построено на интегральных схемах серии 155, Формула изобретения 1. Устройство для вычисления логарифмов чисел, содержащее три регистра, два элемента ИЛИ, схему сравнения и сдвигатощий регистр, отличающееся тем, что, с целью повышения быстро 5ействия, в него введены два. сумматора помодулю два, регистр, блок извлечения корня и параллельный множительно-делительный блок, к первому входу которого подключен выход блока извлечения корня и вход первого регистра, подкл1оченного своим выходом к входу блока извлечения корня, к первому и второму входам первого сумматора по модулю два подключены соответственнб выходы первого и второго элементов ИЛИ, выход пер&ого сумматора по модулю два соединен с первым входом второго сумматора по модулю два, выход второго регистра соединен с вторым входом параллельного множительноделительного блока, управляющий вход которого соединен с выходом второго сумма тора по модулю два, разряднью выходы с входом второго регистра, а выходы старших разрядсб - с первым входом схемы сравнения; подключенной своим выходом к входу сдвига сдвигающего регистра выход младшего разряда которого подключен к второму вхоцу второго сумматора по модулю два, выходы (л +1) старщих разрядов третьего и п-разрядов четвертого регистров подключены соответственно к входам второго и первого элементов ИЛИ, выход второго элемента ИЛИ соединен с вторым входом схемы сравнения, выходом которой является выход сумматора по модулю два. 2. Устройство по п. I, о т л и ч а ю щ е е с я тем, что множите льно-делительный блок содержит 1 групп одноразрядных сумматоров по ( 1с + 1) в каждой (где 1с - разрядность выходного кода), 10 9116 первую группу из (X + I) коммутирующих уёлов и (1с-I) групп из () коммутирующих узлов в каждой ( i +1)--ой группе (i ,...,k), причем выход каждого В-го орноразрядного сумматора (2 1,2, ..., 1.-И) i -ой группы соединен с первым входом (K-l)-ro одноразрядного сумматора (i +1)-ой группы, второй вход которого подключен к выходу (Р +2)-го коммутирующего узла (i +1)-ой группы, подключенного своим, вход ом к выходу первого коммутирутощего узла этой же группы, третьи входы (Р +2)-ых коммутирующих узлов ( i +1}-рй группы обьединены и подключены к пятому и шестому входам соответственно ( +1)-го и В -го коммутирующего узла первой Г{ушы и к входу -Го разряда первого входа мнсисительно-целительного блока, первые входы каждого коммутирующего узла ой .группы объединены и подключены к управляющему вхору устройства и третьему ВХОДУ (It :1)-го одноразрядного сумматора первой г руппы, выход переноса ,po одноразрядного сумматора i -ой соединен с вторыми входами первого и второго коммутирующих узлов соответственно ( i +1)-ой и i -ой групп, третьи входы второго и первого коммутирующях узлов ( i +1)-ой грушы подкя1Оче„ соответственно к выходу первого одноразрядного сумматора -ой группы и к входу (i +2)-го разряда второго входа мнржите льно-делительного блока, входы и второго разрядов которого соециненад соответственно с вторым и четверрым входами коммутирующих узлов группы, тремй вход каждого 4-го коммутирукщего узла которой подключен к входу i -го разряда второго входа множитёльно-делительного блока, вход каждого { +1)-го разряда которого соединен с вторым входом {k +3)-Го коммутирутощего узла ( t +1)-оЙ группы, подключенных своими выходами к третьему входу одноразрйдного сумматора (i -МЬой Ьрупцы, первый и второй входы каждого i-го одноразрядного сумматора цервой rpynwu подключены соответственно к первому и второму вькоду -i -го коммутирующего первой группы, второй вход (К+1)-го одноразрйдного сумматора (i +1)-ой группы соединен с вторым вькодом (k+2)-го коммутирующего узла (i +1)-ой группы, подключенного своим пятым входом к вхог ду младшего разряда первогр входа множительно-делительного блока, а четвертый вход ( 1с+ 2)-го коммутирующего узла второй и (-k +2) .ч)й групп соединен соотвегст1793венно с входом второго разряда второго входа множительно-делигельного блока и с выходом первого коммутирующего узла (i +1)-ой группы, Выход переноса первого одноразрядного сумматора первой Г|уппы, выход первого коммутирующего узла каждой ( i +1)-ой группы и выход каждого одноразрядного сумматора it-ой группы соединены с выходами множительно-делительно го блока, третий вход третьего коммут грующего узла {i группы соединен с выходом переноса первого одноразрядного сумматора (i +2)-ой группы, выход переноса первого одноразрядного сумматора второй группы соединен с четвертым входом первого коммутирующего узла вервой группы, пятый вход которого подключен к управляющему входа параллельного множительно-делительного блока, а одноразрясщые сумматоры каждой f-ой группы обьедчаены цепями переноса. 3. Устройство по п. I. отличающ е 8 с я тем, что блок извлечения корня содержит (-1) (k-разрядность выходкого кода) группу последовательно соединеннйх одноразрядных сумматоров, группу сумматорсв по модулю два, группу элементов ИЛИ, группу элементов НЕ, (п -2) допсишительных групп из (п -i -I) (где 1 омер группы) сумматорой по модулю два в каждой группе, генератор единиц и группу из (п-2) элементов И, каждая 1-я группа О 1,2,...,п-1) одноразрядных сумматоров содержит (п +2 -i) oftнораэрядных сумматоров, а группы эл&ментов ИЛИ, элементов НЕ и сумматоров по модулю два ссдатветсгвенно содернсат (п-1) и (п -2) элэментов, причем выход каждого j -го оаноразрядно| о сумматора , (i -Ц)-ой группы соединен с первым входом (j -1)-го одноразрядного сумматора 1-ой группы, второй вход первого одно разрядного сумматора i -ой группы соеди1нен с выходом переноса первого однорааГрядного сумматора (i +1)-ой группы, пёрвыл входами i -ых элементов И, ИЛИ, сумматоров по модулю два групп и сумматоров по модулю два i -ой цопслнительной группы, выходы которых соесшнены с вторыми входами j -ых( ,...,п-i) ойноразрядньсс сумматоров i-ой группы, вгорые входы j-ой ( J 2,... ) сумматоров по модулю два i-ой дополнительной группы соединены с выходами переноса первых одноразрядных сумматоров (п-j + + 1)-ых групп, выход-f-го элемента НЕ группы подключены к первому входу (п+ + 1 - i )-го одноразрядного сумматфа i -ой группы, второй вход которого соеди- 9118 нея с выходом i -го элемента И группы, подключенного своим вторым входом к выходу tiejaeaoca первого одноразрядного сумматора (i-2 )-ой группы, первый вход ( +2 i )-одноразрядного сумматора i-ой группы подключен к вькоау i -го сумматора по модулю два группы, подключенного своим вторым входом к выходу i-ro элемента ИЛИ группы, второй вход которого соецинен с выходом (i.+ l)-ro элеменга ИЛИ группы, выход (п -1)-го элемента ИЛИ которой соединен с первым входом первого сумматора-по модулю два каждои |-ой дополшггельной группы, входом . (h-I)-ro элемента НЕ группы и вторым входом (п -2)-го элемента ИЛИ группы, второй вход (п +2-1 )-го одноразрядного сумматора i -ой группы соецинен с входом (2п -2+1)-го блока изв/вчения корня, ( 2п-21+2)-ый разряд которой поцключен к третьему входу одноразрядного сумматора, входу (п -1)-го адамента НЕ группы, первый и второй входы разрядов, входа блока извшчения корня подключены к входам (n-l)-ro элемента ИЛИ груп ы, к nepвы r входам соответственно первого и второго одноразрядного суммато- („ 1)ой группы, вторые входы котор д соединены соответственно с выходом (п -1)-го элемента НЕ группы и генерагора единиц, подключенного к первому входу третьего одноразрядного сумматора ,и (п-1)-ой группы, выходы переносов первых одноразрядных сумматоров и выход (п -1)-го э;юмента ИЛИ группы являются выходами блока извлечения корня, а вход каждого элемента И и выход каждогоп-го сумматора по модулю два групп выпоа1ены в виде инверсных. 4. Устройство по п. I, о т л и ч а ю щ е е с я тем, что коммутирующие уалы первой группы содержат два элемента 2И-ИЛИ, причем первый вход узла соедицен с первыми и вторыми входами первопо и второго элементов 2И-ИЛИ, второй „ третий входы узла подключены к третье и четвертому входам первого элемен- , четвертый и пятый входы уэла соединены с треизим и четвертым входами второго элэмента 2И-ИЛИ, пятый и ; шестой входы узла подключены к пятым входам соответственно второго и первого элементов 2И-ИЛИ, выходы которых являются соответственно вторым и первым выходами коммутирующего узла. 5 Устройство по п. 1, о т л и ч а ющ е е с я тем, что в каждой группе (i 2,3,..., V )коммутирующие узлы с первого по третий содержат четырехвхоцовый элемент 2И-ИЛИ, коммутирующие узлы с четвертого по ()-ый содержат .пятявходовый элемент 2И-ЙЛИ, (Ц+2)-ый коммутирукщий узел содержит два элэмента 2И-41ЛИ (п +3)-ый коммутиругсядий узел содержит элемент И, причем первый и второй входы четырехвходоього элемента 2И-ИЛИ соединены с первым входом J-го коммутирующего узла (j 1,2,3), второй и третий входы которого соединень с третьим и четвертым входами, .четырехвходового элемента 2H-4dJfli, которого является выходом/ -го коммутирутог щего узла первый вход пятивходового элеме та 2И-ИЛИ :№ляется первым входом коммутирукядего узла (ji 4,5,...К -ь), второй и третий входы которого соединены соответственно с вторым и четвертым, пяГы входами пятивходового элемента 2И-ИЛЙ, выход которого является выходом jn коммутирутсяцего узла, первый вход (1i +2)-го коммутирующего узла соединен с nepBiAviH ьходами первого и второго

93 91 элементой 2И-41ЛИ и вторым входом второго элемента , второй вход (-k н-2)-го коммутирующего узла соединен с вторым входом первого элэ мента 2ИИЛИ и третьими входами первого и второго элементов 2И- ИЛИ, третий вход ( + +2)-го KOMivQrTHpyKMuero узла соединен с четвертым и пятым входами первого элемента , четвертый и пятый вхо№1 ( +2)-го коммутирующего узла соединены соответственно с че№ертым и пятым входами второго элемента 2И-44/М, выхощы первого и второго элементовг 2ИИЛИ выходами (1с +2)-го коммутирующего узла. Источники информации, принятые во внимание при экспертизе 1,Авторское свидетельство СССР N9 64145О, кл. Q Об F 7/38, l979. 2,Авторское свидетепьс№о СССР № 59О733, кл. G Об F 7/38, 1978 :(прогогйоЬ

фаг.З

LZjiJ

gju3

фие.5

Авторы

Даты

1982-05-30—Публикация

1980-06-30—Подача