(54) ДИФФЕРЕНЦИРУЮЩЕЕ УСТРОЙСТВО

| название | год | авторы | номер документа |

|---|---|---|---|

| Датчик тока | 1982 |

|

SU1057788A1 |

| Фазовый компаратор | 1986 |

|

SU1429288A1 |

| Измеритель активной и реактивной составляющих полного сопротивления | 1975 |

|

SU564608A1 |

| Синхронный детектор | 1978 |

|

SU711674A1 |

| Дифференцирующее устройство | 1982 |

|

SU1051547A1 |

| Измеритель параметров комплексных сопротивлений | 1989 |

|

SU1751690A1 |

| ПИКОВЫЙ ДЕТЕКТОР | 2009 |

|

RU2409818C1 |

| Преобразователь угла поворота вала в длительность импульсов | 1987 |

|

SU1534755A1 |

| Усилитель мощности | 1983 |

|

SU1133649A1 |

| Дифференцирующее устройство | 1988 |

|

SU1508246A1 |

I

Изобретение относится к аналоговой вычислительной технике и может быть использовано в системах автоматического регулирования.

Известны дифференцирующие устройства, основанные на сравнении запомнен- ных мгновенных значений сигнала в тактовые моменты времени. Одно из них содержит два входных кпюча, запоминающие конденсаторы и дифференциальный усилитель 1 1 J.

Однако выходной сигнал устройства является знакопеременным, что затрудняет епо использование в ряде систем.

Наиболее близким к предлагаемому ПО технической сущности является дифференцирующее устройство, содержащее два запоминающих конденсатора, соединенных с входом через первый и второй управляемые ключи, первый и второй дифференциальные усилители, триггер, третий и четвертый управляемые ключи и два переходных конденсатора, при этом первые обкладки запоминающих конденсаторов подключены к соответствующим входам первого дифференциального усилителя, выход которого через третий и чет вертый управляемые ключи связан с соответствующими входами второго дифференциального усилителя, выходы триггера соединены с управляющими входами первого и второго управляемых ключей через соответствующие переходные конденсаторь, а с управляющими входами третьего и четвертого управляемых - непосредственно. Известное устройство позволяет получить выходной сигнал в виде напряжения постоянного тока 2 J.

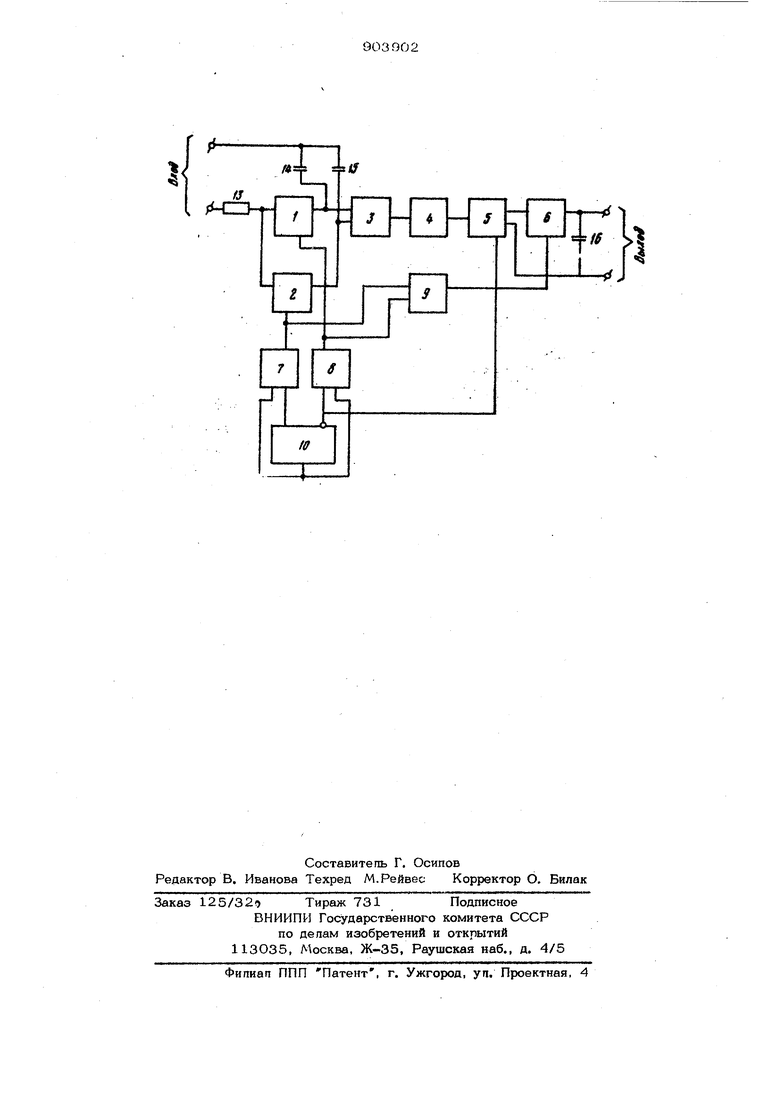

Однако в выходном сигнале устройства присутствуют выбросы напряжения противоположной полярности, возникающие при перезаряде запоминающих конденсаторов. Кроме того, управление входными ключами с помощью экспоненциапь ных импульсов, получающихся при перезаряде переходных конденсаторов через входное сопротивление ключей, не позво390ляет попучить стабапьного времени замы кания входных кпючой и стабильной фазы размыкания кпючей. Это приводит к нарушению симметрии переменного напря жения с выхода первого йиффсренциапьногр усилите ля и к пуггьсациям выходд о- го напряжения устройства с частотой Нэстабильность и разброс пара метров цепей заряап запоминающих конденсаторов затрудняет использование из- вестного устройство п качестве пиффе- ренциатора огибакидой а мп ли ту дно-моду- ли :юванного входного сигнапа, а слабое подавпение синфазного снгнапа -в дифференциальном уси.чнтопо и его дрейф могут привести к амяпитудной модупяции выходного сигнала. UeniD изобретения - повышение точнос ти и помехоустойчивости. Цеггь достигается тем, что дифференцирующее устройство, содержащее первый и второй запоминающие конденсаторы, первые обкпадки которых соединены с первой входной шиной, вторые обкпадки запоминающих конденсаторов соединены с Соответствующими вхопами. цпфферен- циапьного усипитегтя и с выходами первого и второго кпючей, и триггер, допо ните пьно содержит два эпемента И, эпемент ИЛИ-НЕ, фипьтр высоких 9acтoт, фазовый детектор, третий кпюч, третий запоминающий конденсатор, фазоврашате ть, формирователь импупьсов и зарядный резистор, через который вторая входная шина связана с входами первого и второго ключей, выход дифференциального усилителя связан через фипьтр высокой частоты с первым чзходом фазового детектора, второй вход которого подключен к выходу триггера, первый выход фазового детектора через третий кпюч, а второй выход непосредственно соединены с обкладками третьего запоминающего конденсатора и с соответству ющими выходными шинами устройства, вход фазовращателя подключен к шине задания тактовой частоты, а выход фазо вращателя через формирователь импупь- сов к счетному входу триггера и к первым входам элементов И, вторые входы которых соединены соответственно с пря мым и инверсным выходами триггера, в ходы эпементов И соединены с упрайпя- юшими входами первого It второго ключей, а также с соответствующими входа ми эпемента ИЛИ-НЕ, выход которого соединен с управляющим входом третьег ключа. 2 На чертеже представлена схема предлагаемого устройства. Устройство содержит кпючи 1 и 2, дифференциальный усилитель 3, фильтр 4 высоких частот, фазовый детектор 5, ключ 6, элементы И 7 и 8, элемент ИЛИ-НЕ9, триггер 1О, формироватепь 11 импульсов, фазовращатель 12, входной резистор 13, запоминающие конден. саторы 14-16. Позицией 17 обозначена щииа задания тактовой частоты. Устройство работает следующим образом. Входной сигнал через резистор1.3 и кпючи 1 и 2, замыкающиеся поочередно частотой тс1кт / 1 поступает на коненсаторы 14 или 15, образующие с резистором 13 интегрирующую цепочку. Ее постоянная времени соизмерима с длительностью .импульсов записи, открывающих ключи 1 и 2. Это способствует подавлению входных импульсных помех. С конденсаторов 14 и 15 попеременно изменяющиеся ступенчатые наприте- НИН поступают на в.ход дифференциального усилителя 3, на выходе которого образуется переменное -напряжение прямоугольной формы с фронтами, определяемыми постоянной времени цепи заряда запоминающих конденсаторов 14 и 15. После фильтрации напряжения-дрейфа и .синфазной помехи дифференциально1го усигштеля 3 переменное напряжение поступает на вход фазового детектора 5, на другой вход которого подается опорное напряжение прямоугольной формы с выхода триггера 10. На выходе фазового детектора 5 образуется постоянное напряжение, пропорциональное скорости изменения входного сигнала, имеющее выбросы напряжения противоположной полярности. На время действия этих выбросов напряжения ключ 6 размыкается и на конденсаторе 16, подключенном к выходу устройства, хранится предьщушее значеР1ие напряжения. Импульсы записи вырабатываются формирователем 11 и распределяются триргером 1О через элементы И 7 и 8 попеременно на ключи 1 и 2. Импульс, управляющий размыканием ключа 6, обра- на выходе эпемента ИЛИ-НЕ 9. В случае дифференцирования огибающей амп1штудно-модулированного входного сигнапа на шине 17 подается несущая частота . входного сигнала либо, при необходимости {цее нес /3, и т.д.

Фазоврашатепь 12 при этом служит дпя совмещения во времени выходного импупьса формироватепя 11с необходимым участком входного сигнапа, например с максимумом синусоиды входного сигнапа.

Смена полярности выходного напряжения производится подключением входа опорного сигнапа фазового детектора 5 к другому выходу триггера 1О.

Технико-экономический эффект от непользования изобретения обусловлен повышением точности и помехозащищенности при дифференцировании сигналов постоянного и переменного тока. .

Формула изобретения

Дифференцирующее устройство, содержащее первый и второй запоминакшие конденсаторы, первые обкладки которых соединены с первой входной шиной, вторые обкладки запоминающих конденсаторов соединены с соответствующими входами дифференциального усилителя и с выходами первого и второго ключей и триггер, отличающееся тем, что, с целью повышения точности и помехоустойчивости, устройство дополнительно содержит два элемента И, эпемент ИЛИ-НЕ, фильтр высоких частот, фазовый детектор, третий ключ, третий запоминающий конденсатор, фазовращатель, формирователь импульсов и зарядный резистор, через который вторая входная шина связана с входами первого и второго ключей, выход дифференциального усилителя связан через фильтр высокой частоты с первым входом фазового детектора, второй вход которого подключен к ш 1ходу триггера, первый выход фазового детектора через ключ, а второй выход непосредственно соединены с обкладками третьего запоминающего кон денсатора и с соответствующими выходными шинами устройства, вход фазовращателя подключен к щи не задания твисто- вой частоты, а выход фазовращателя через формирователь импульсов - к счетному входу триггера и к первым входам элементов И, вторые входы которых соединены соответственно с прямым и инверсным выходами триггера, выходы элементов И соединены с управляющими входами цервого и второго ключей,а также с соответствукшими входами элемента ИЛИ-НЕ, выход которого соединен с управляющим входом третьего ключа.

Источники информации, принятые во внимание при экспертизе

Авторы

Даты

1982-02-07—Публикация

1980-05-13—Подача