10

It

Изобретение относится к импульсной технике и может быть использовано в устройствах автоподстройки частоты, синтезаторах частот и ряде других устройств, где необходимо применение фазовых компараторов.

Целью изобретения является повышение быстродействия фазового компаратора при одновременном обеспечении возможности изменения передаточной характеристики фазового компаратора в широких пределах.

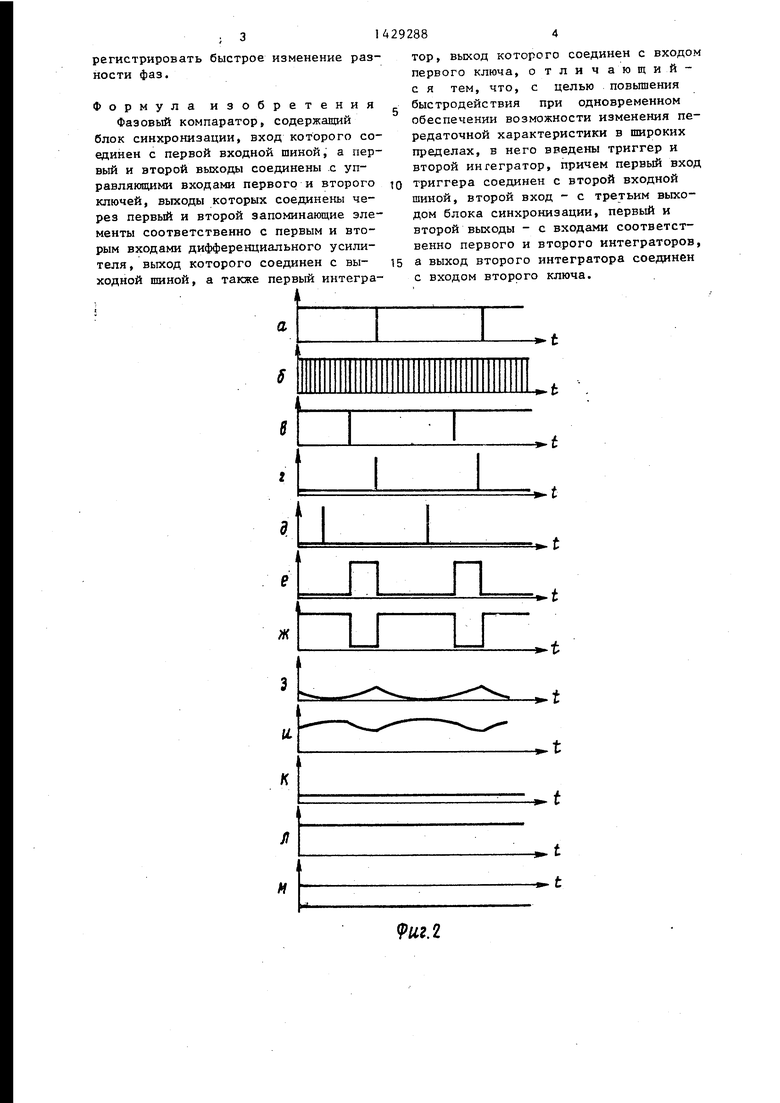

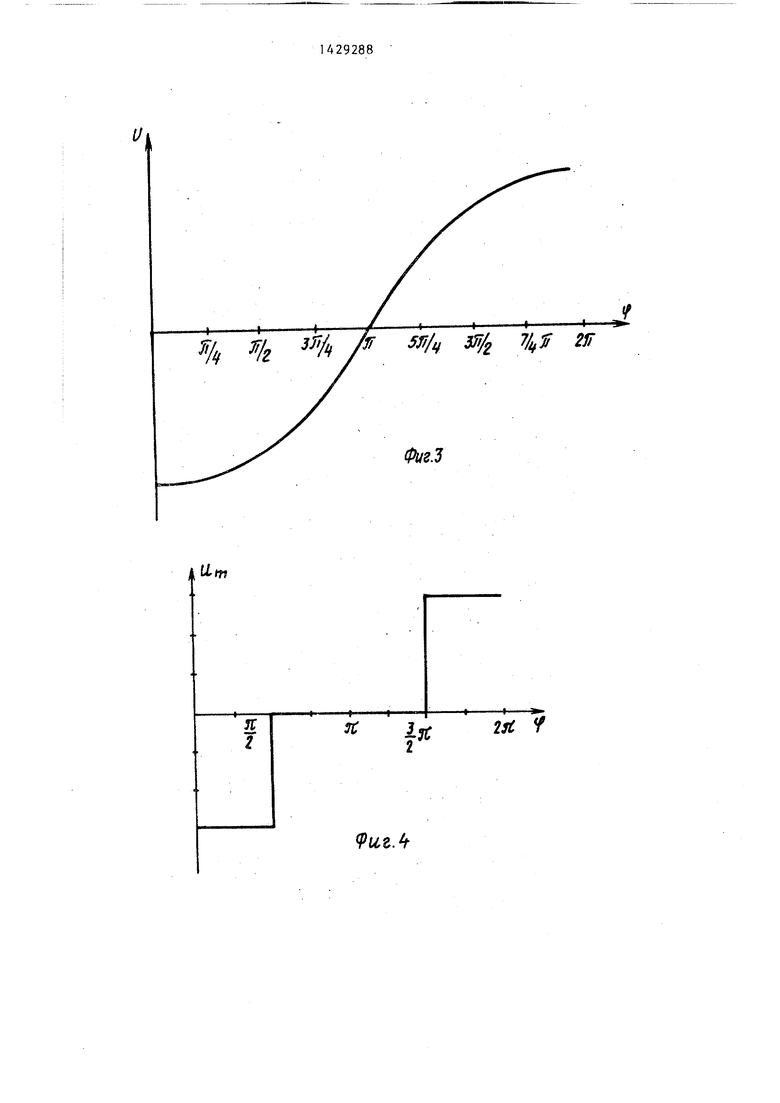

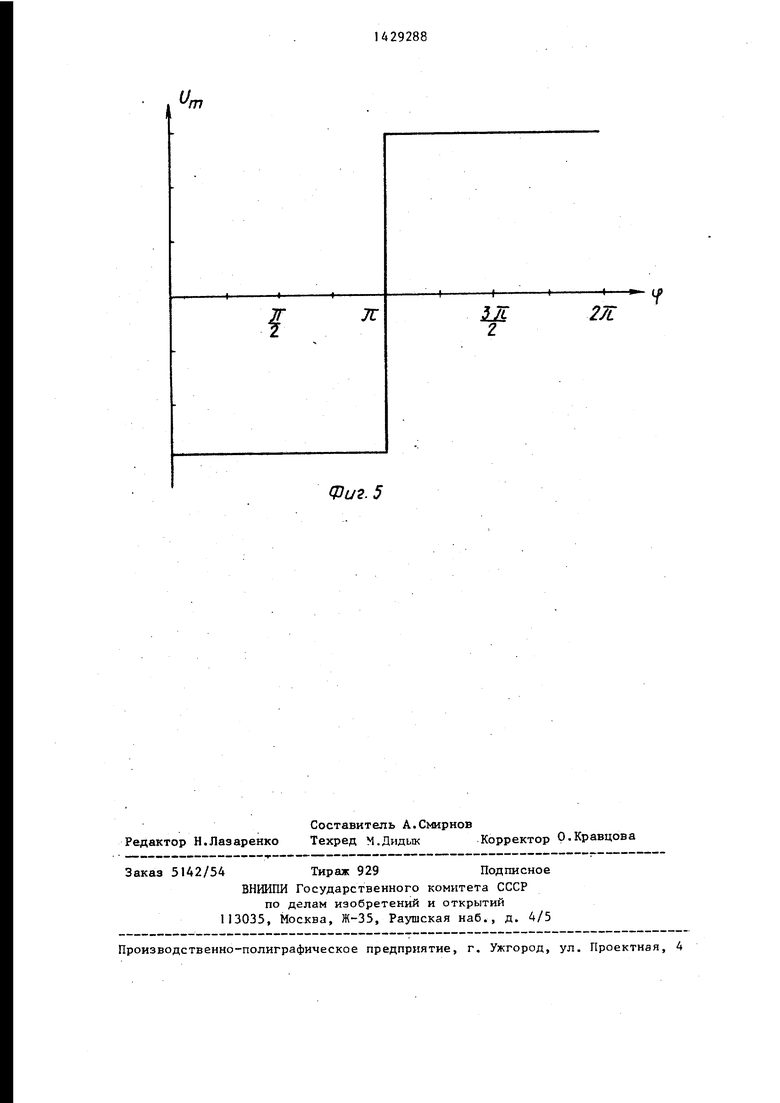

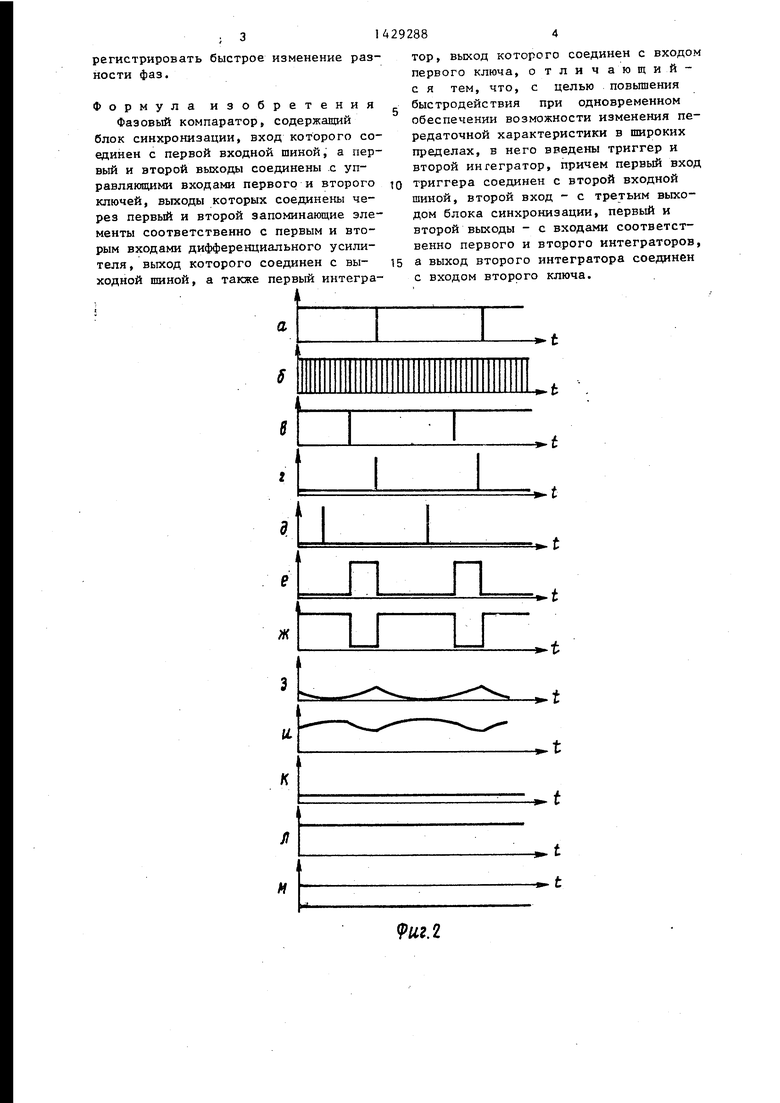

На фиг.1 приведена структурная схема устройства; на фиг.2 - временные диаграммы работы устройства; на фиг,3-5 - передаточные характеристики для различных комбинаций параметров устройства.

Фазовый компаратор содержит блок 1 синхронизации, триггер 2, первый 3 и второй 4 интеграторы, первый 5 и второй 6 ключи, первый 7 и второй 8 за- поминаклцие элементы, дифференциальный усилитель 9, первую 10 и вторую 11 входные шины, выходную шину 12 и шину 13 напряжения смещения.

Вход блока i соединен с первой входной шиной 10, первый и второй выходы - с управляющими входами первого 5 и второго 6 ключей. Вторая входная шина 11 соединена с первым входом триггера 2, второй вход которого соединен с третьим выходом блока 1, а первый и второй выходы через последовательно соединенные первые интегратор, ключ и запоминающий элемент и вторые интегратор, ключ и запоминающий элемент соединены соответственно с первым и BTOpbiM входами дифференциального усилителя, выход которого соединен с выходной шиной 12.

Блок 1 может быть выполнен в ы-ще счетчика на N, последовательно соединенного с дешифратором на N выходов. В этом случае опорная частота, подаваемая на первую входную шину 10, должна быть в N раз больше частоты сигнала на второй входной шине 11. На третьем выходе блока 1 вырабатывается короткий импульс в начале периода опорной частоты, поделенной на N, а на первом и втором выходах - импульсы с заданным фазовым сдвигом относительно начала периода. Триггер 2 является, например, RS-триггером.

Запоминающие элементы 7 и,8 могут быть выполнены в виде конденсаторов, первые обкладки которых являются вхо

0

5

0

5

0

5

0

0

дом и выходом запоминающего элемента, а вторые обкладки соединены с шиной 13, на которую подано постоянное напряжение, величина которого несущественна.

Устройство работает следующим образом,

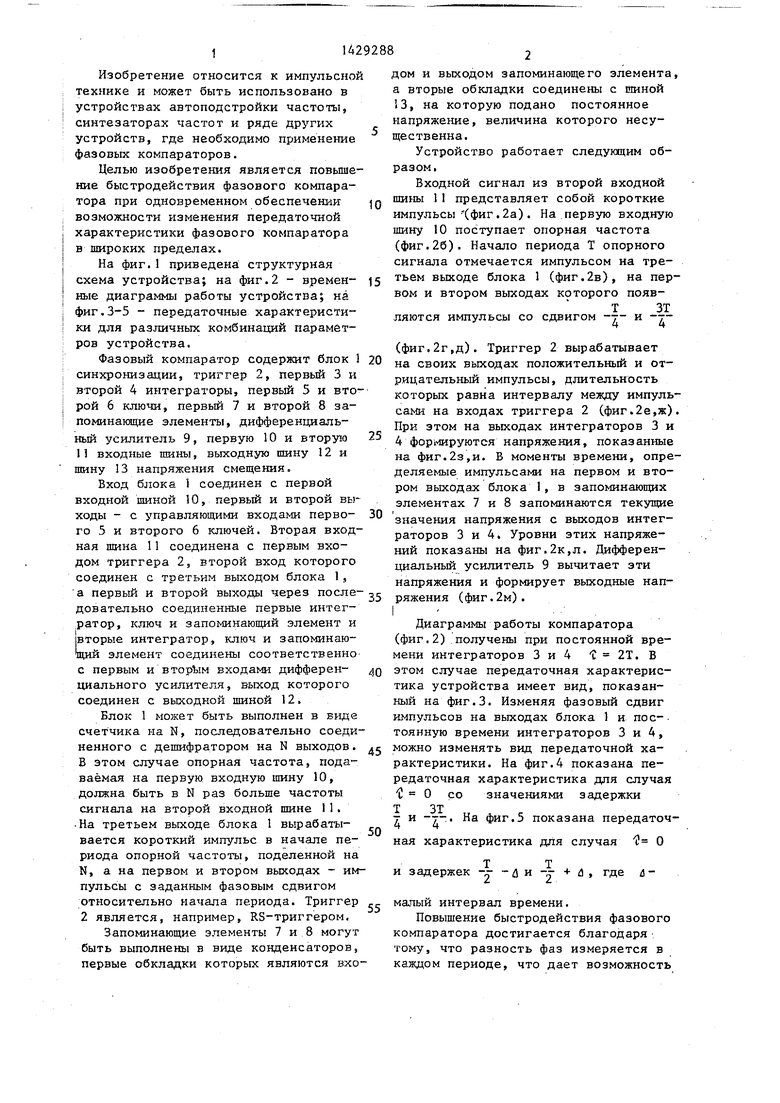

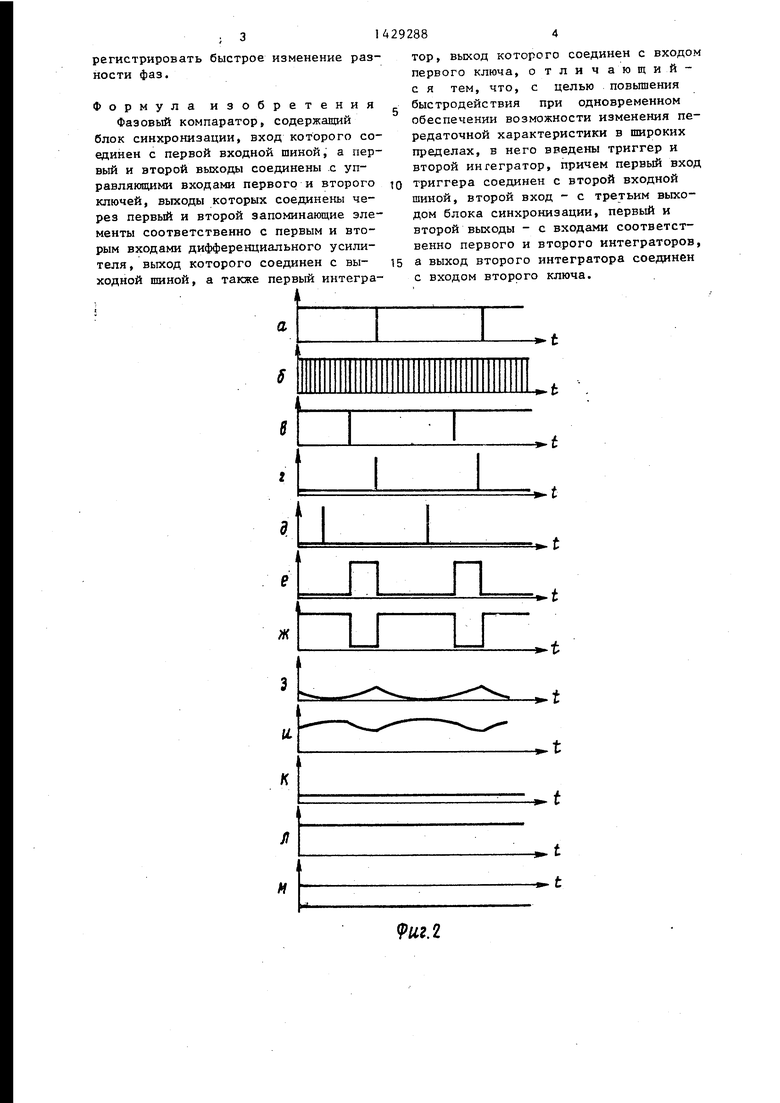

Входной сигнал из второй входной шины 11 представляет собой короткие импульсы (фиг.2а). На первую входную шину 10 поступает опорная частота (фиг.26). Начало периода Т опорного сигнала отмечается импульсом на третьем выходе блока 1 (фиг.2в), на первом и втором выходах которого появТ ЗТ ляются импульсы со сдвигом -т- и -т(фиг.2г,д). Триггер 2 вырабатывает на своих выходах положительный и отрицательный импульсы, длительность которых равна интервалу между импульсами на входах триггера 2 (фиг.2е,ж). При этом на выходах интеграторов 3 и 4 фор отруются напряжения, показанные на фиг.2з,и. В моменты времени, определяемые импульсами на первом и втором выходах блока I, в запоминающих элементах 7 и 8 запоминаются текущие значения напряжения с выходов интеграторов 3 и 4. Уровни этих напряжений показаны на фиг.2к,л. Дифференциальный усилитель 9 вычитает эти напряжения и формирует выходные напряжения (фиг.2м). I -. .

Диаграммы работы компаратора (фиг.2) получены при постоянной времени интеграторов 3 и 4 t 2Т. В этом случае передаточная характеристика устройства имеет вид, показанный на фиг.3. Изменяя фазовый сдвиг импульсов на выходах блока 1 и пос-- тоянную времени интеграторов 3 и 4, можно изменять вид передаточной характеристики. На фиг.4 показана передаточная характеристика для случая со значениями задержки

Т ЗТ

7 и -д- На фиг.5 показана передаточная характеристика для случая 1) О

Т Т и задержек & и - + и

где й

малый интервал времени.

Повышение быстродействия фазового компаратора достигается благодаря тому, что разность фаз измеряется в каждом периоде, что дает возможность

регистрировать быстрое изменение разности фаз.

Формула изобретения

Фазовый компаратор, содержащий блок синхронизации, вход которого соединен с первой входной шиной, а первый и второй выходы соединены .с управляющими входами первого и второго ключей, выходы которых соединены через первьй и второй запоминающие элементы соответственно с первым и вторым входами дифференциального усилителя, выход которого соединен с выходной шиной, а также первый интегра

тор, выход которого соединен с входом первого ключа, отличающий- с я тем, что, с целью повышения быстродействия при одновременном обеспечении возможности изменения передаточной характеристики в широких пределах, в него введены триггер и второй интегратор, причем первый вход триггера соединен с второй входной шиной, второй вход - с третьим вько- дом блока синхронизации, первый и второй выходы - с входами соответственно первого и второго интеграторов, а выход второго интегратора соединен с входом второго ключа.

| название | год | авторы | номер документа |

|---|---|---|---|

| Импульсно-фазовый детектор | 1987 |

|

SU1552369A1 |

| Устройство для контроля динамических параметров аналого-цифровых преобразователей | 1987 |

|

SU1474839A1 |

| УСТРОЙСТВО АНАЛОГО-ЦИФРОВОГО ПРЕОБРАЗОВАНИЯ | 1992 |

|

RU2042269C1 |

| Измеритель параметров комплексных сопротивлений | 1989 |

|

SU1751690A1 |

| Цифровой интегрирующий вольтметр | 1985 |

|

SU1267272A1 |

| Устройство для измерения ускорений | 2020 |

|

RU2740875C1 |

| Цифровой синтезатор частоты с частотной модуляцией | 1989 |

|

SU1771068A1 |

| Устройство для контроля средств числового программного управления | 1988 |

|

SU1675852A1 |

| Цифровой интегрирующий вольтметр | 1983 |

|

SU1093984A2 |

| Двухотсчетный преобразователь угла поворота вала в код | 1985 |

|

SU1269265A1 |

Изобретение относится к импульсной технике и может быть использовано в устройствах автоподстройки частоты, синтезаторах частот и в ряде других устройств, где необходимо применение фазовых компараторов. Целью изобретения является повышение быстродействия фазового компаратора itpia одновременном обеспечении возможности изменения передаточной характеристики фазового компаратора в широких пределах. Для достижения этой цели в устройство дополнительно введены триггер 2 и второй интегра- .тор 4. Кроме того, устройство содержит блок 1 синхронизации, первый интегратор 3, ключи 5 Н в, запоминаю щие элементы 7 и 8, дифференциальный усилитель 9, входнь1е шины 10 и 11, выходную шину 12 и шину 13 напряжения смещения. Повышение быстродействия предложенного фазового компарато- ра по сравнению с прототипом достиг а- SS ется благодаря тому, что разность фаз измеряется в каждом периоде, что дает возможность регистрировать быстрое изменение разности фаз. 5 ил. (Л

ж 3 и. к

fi н

t

9иг.2

Н--I.

Д

% % Л / f /2 V

t I

II

Ijt

2

. J

t I

II

Ijt

9uz.

Фи.5

Ж

UL

27L

| Синхронный детектор | 1976 |

|

SU657581A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1988-10-07—Публикация

1986-05-27—Подача