I

Изобретение относится к устройствам логарифмического преобразования аналоговых сигналов и может быть использовано в аналоговых вычислительных машинах.

Известен логарифмический преобразователь амплитуды импульсов, содержащий компаратор, ключи, счетчик .

Однако устройство характеризуется низкой точностью работы.

Наиболее близким к предлагаемому является логарифмический преобразователь амплитуды импульсов, содержащий блок усиления, компараторы, накопительный конденсатор, делители напряжения, блок управления .

Недостатком устройства является малая точность преобразования, обусловленная низкой помехоустойчивостью и большой погрешностью при преобразовании импульсных сигналов с пологим спадом.

Цель изобретения - повышение точности преобразования.

Поставленная цель достигается тем, что известный логарифмический преобразователь амплитуды импульсов, содержащий блок усиления, выход которого соединен со входом повторителя напряжения и с первым выводом токозадающего резистора, первый вход блока усиления является входом логарифмического преобразователя амплитуды импульсов и подключен к первому входу первого компаратора, второй вход которого соединен с выходом источника опорного напряжения, выход блока усиления через накопительный конденсатор соединен с шиной нулевого потенциала, выход повторителя напряжения подключен к первому входу второго, компаратора и через первый делитель напряжения - ко второму входу блока усиления, первый вход второго компаратора через второй делитель напряжения соединен с первым входом третьего компаратора, выходы первого, втоDoro и третьего компараторов соедийены соответственно с первым, вторым и третьим входами блока управления, введены усилитель постоянного тока, первый и второй дополнительные источники опорных напряжений, дополнительный накопительный конденсатор, блокирующий конденсатор, первый, в торой,третий и четвертый ключи, управляемый генератор тока, причем первый вход усилителя постоянного тока соединен с первым входом второго компаратора, выход усилителя постоянного тока через первый ключ подключен к первой обкладке дополнительного накопительного конденсатора и к управляющему входу управляемого генератора тока, выход которого соединен с выходом повторителя напряжения, первая обкладка блокирующего конденсатора подключена к первому входу третьего компаратора, вторые обкладки дополнительного накопительного и блокирующего конденсаторов и второй вход усилителя постоянного тока соединены с шиной нулевого потенциала, выход первого дополнительного источника опорного напряжения через второй .ключ подключен ко второму выводу токозадающего резистора, первый вход первого компаратора через третий соединен со вторыми входами второго и третьего компараторов, к которым через четвертый ключ подключен выход второго дополнительного источника опорного напряжения, четвертый вход блока управления является входом установки в исходное состояние логарифмического преобразователя амплитуды импульсов, первый выход блока управления соединен с управляющим входом блока усиления, второй, третий, четвертый и пятый выходы блока управления подключены к управляющим входам соответственно четвертого третьего, первого и второго ключей, второй, выход блока управления является выходом логарифмического преобразователя амплитуды импульсов, а блок управления содержит первый и второй триггеры, первый и второй элементы И, первый и второй элементы ИЛИ и одновибратор причем выход первого триггера.соединен с первыми входами первого элемента И и второго элемента ИЛИ, выход первого элемента И подключен к первым входам первого триггера и первого элемента ИЛИ, вход второго

триггера через одновибратор соединен со вторым входом элемента ИЛИ, выход которого подключен ко второму входу второго триггера, выход которого соединен с первым входом второго элемента И, второй вход которого подключен ко второму входу первого элемента И, инверсный выход второго тpиfгepa соединен со вторым

входом второго элемента ИЛИ, входы установки в исходное состояние первого и второго триггеров соединены, первый вход второго триггера является первым входом блока управления,

5 второй вход первого элемента И является вторым входом блока управления, второй вход первого триггера является третьим входом блока управления , четвертым входом которого явQ ляется вход,установки в исходное состояние первого триггера, выходы вто . рого элемента И и первого триггера являются соответственно первым и вторым выходами блока управления, инверсный выход первого триггера является третьим выходом блока управления, инверсный выход второго триггера является четвертым выходом блока управления, пятым выходом которого

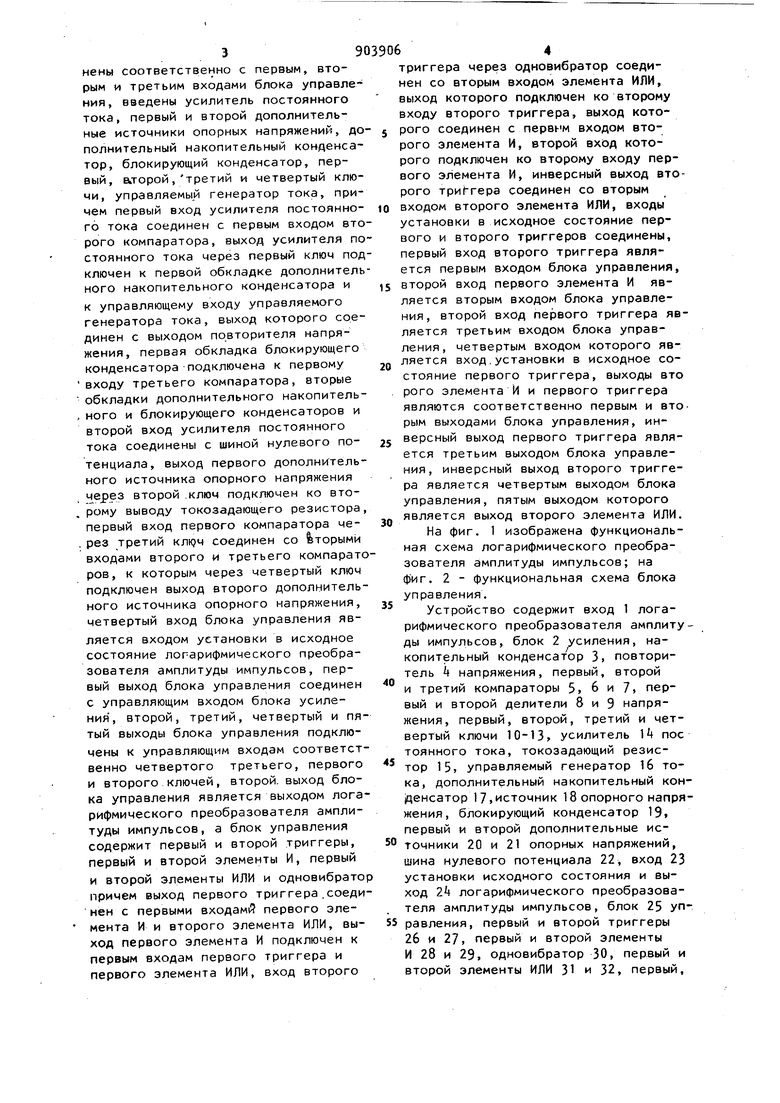

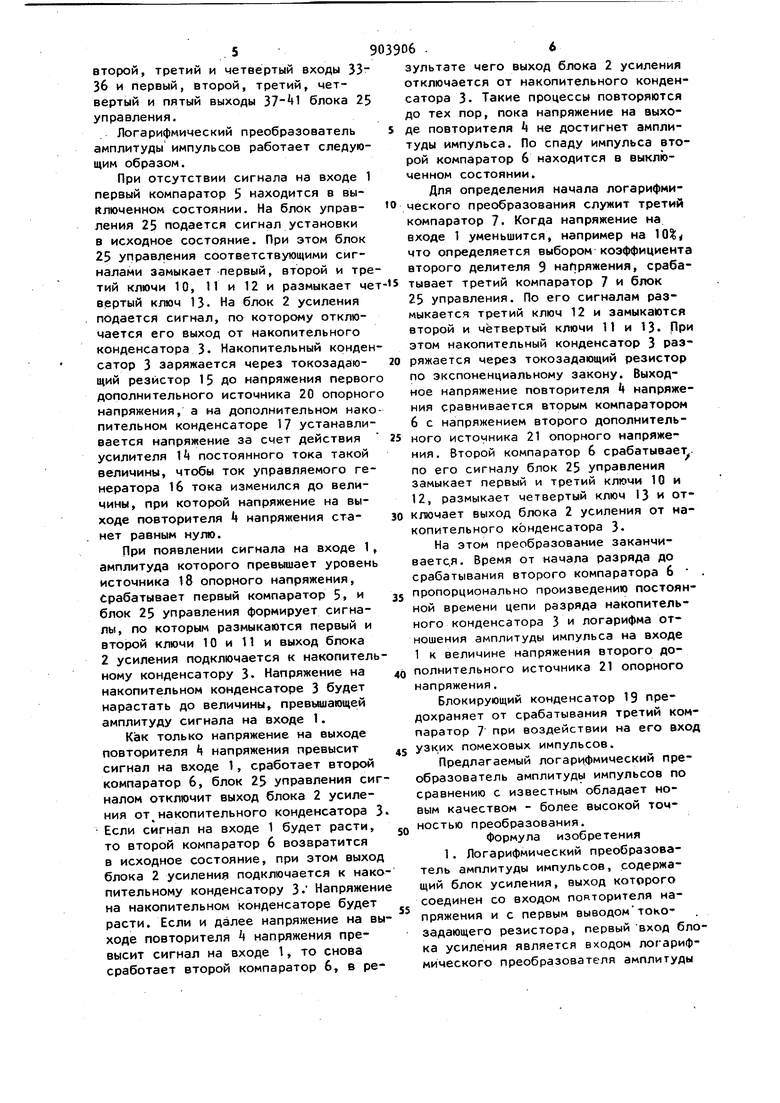

является выход второго элемента ИЛИ. На фиг. 1 изображена функциональная схема логарифмического преобразователя амплитуды импульсов; на фиг. 2 - функциональная схема блока управления.

Устройство содержит вход 1 логарифмического преобразователя амплитуды импульсов, блок 2 усиления, накопительный конденсатор 3, повторитель напряжения, первый, второй и третий компараторы 5, 6 и 7, первый и второй делители 8 и 9 напряжения, первый, второй, третий и четвертый ключи 10-13, усилитель 1t пос тоянного тока, токозадающий резистор 15, управляемый генератор 16 тока, дополнительный накопительный кон(Ценсатор 17,источник 18 опорного напряжения, блокирующий конденсатор 19. первый и второй дополнительные ис точники 20 и 21 опорных напряжений, шина нулевого потенциала 22, вход 23 установки исходного состояния и выход 2k логарифмического преобразователя амплитуды импульсов, блок 25 управления, первый и второй триггеры 26 и 27, первый и второй элементы И 28 и 29, одновибратор 30, первый и второй элементы ИЛИ 31 и 32, первый. второй, третий и четвертый входы 33 36 и первый, второй, третий, четвертый и пятый выходы блока 25 управления. Логарифмический преобразователь амплитуды импульсов работает следующим образом. При отсутствии сигнала на входе 1 первый компаратор 5 находится в выключенном состоянии. На блок управления 25 подается сигнал установки в исходное состояние. При этом блок 25 управления соответствующими си|- налами замыкает первый, второй и тре тий ключи 10, 11 и 12 и размыкает че вертый ключ 13. На блок 2 усиления подается сигнал, по которому отктючается его выход от накопительного конденсатора 3. Накопительный конден сатор 3 заряжается через токозадающий резистор 15 до напряжения первог дополнительного источника 20 опорног напряжения, а на дополнительном нако пительном конденсаторе 17 устанавливается напряжение за счет действия усилителя 1k постоянного тока такой величины, чтобы ток управляемого генератора 16 тока изменился до величины, при которой напряжение на выходе повторителя k напряжения станет равным нулю. При появлении сигнала на входе 1, амплитуда которого превышает уровень источника 18 опорного напряжения. Срабатывает первый компаратор 5 и блок 25 управления формирует сигналы, по которым размыкаются первый и второй ключи 10 и И и выход блока 2 усиления подключается к накопитель ному конденсатору 3. Напряжение на накопительном конденсаторе 3 будет нарастать до величины, превышающей амплитуду сигнала на входе 1. Как только напряжение на выходе повторителя k напряжения превысит сигнал на входе 1, сработает второй компаратор 6, блок 25 управления сиг налом отключит выход блока 2 усиления от накопительного конденсатора 3 Если сигнал на входе 1 будет расти, то второй компаратор 6 возвратится в исходное состояние, при этом выход блока 2 усиления подключается к нако пительному конденсатору 3. Напряжени на накопительном конденсаторе будет расти. Если и далее напряжение на вы ходе повторителя напряжения превысит сигнал на входе 1, то снова сработает второй компаратор 6, в результате чего выход блока 2 усиления отключается от накопительного конденсатора 3. Такие процессы повторяются до тех пор, пока напряжение на выходе повторителя « не достигнет амплитуды импульса. По спаду импульса второй компаратор 6 находится в выключенном состоянии. Для определения начале логарифмического преобразования служит третий компаратор 7. Когда напряжение на входе 1 уменьшится, например на 10 что определяется выбором коэффициента второго делителя 9 напряжения, срабатывает третий компаратор 7 и блок 25 управления. По его сигналам размыкается третий ключ 12 и замыкаются второй и четвертый ключи 11 и 13. При этом накопительный конденсатор 3 разряжается через токозадающий резистор по экспоненциальному закону. Выходное напряжение повторителя k напряжения сравнивается вторым компаратором 6 с напряжением второго дополнительного источника 21 опорного напряжения. Второй компаратор 6 срабатывает по его сигналу блок 25 управления замыкает первый и третий ключи 10 и 12, размыкает четвертый ключ 13 и отключает выход блока 2 усиления от накопительного конденсатора 3. На этом преобразование заканчиваетс.я. Время от начала разряда до срабатывания второго компаратора 6 . пропорционально произведению постоянной времени цепи разряда накопительного конденсатора 3 и логарифма отношения амплитуды импульса на входе 1 к величине напряжения второго дополнительного источника 21 опорного напряжения. Блокирующий конденсатор 19 предохраняет от срабатывания третий компаратор 7 при воздействии на его вход узких помеховых импульсов. Предлагаемый логарифмический преобразователь амплитуды импульсов по сравнению с известным обладает новым качеством - более высокой точностью преобразования. Формула изобретения 1. Логарифмический преобразователь амплитуды импульсов, содержащий блок усиления, выход которого соединен со входом повторителя напряжения и с первым выводомтокозадающего резистора, первый вход блока усиления является входом логарифмического преобразователя амплитуды импульсов и подключен к первому вход первого компаратора, второй вход которого соединен с выходом источника опорного напряжения, выход блока усиления мерез накопительный конденсатор соединен с ши.иой нулевого потенциала, выход повторителя напряжения /юдключен к первому входу второго компаратора и через первый делитель напряжения - ко второму входу блока усиления, первый вход второго компаратора мерез второй делитель на пряжения соединен с первым входом третьего компаратора, выходы первого, второго и третьего компараторов соединены соответственно с первым, вторым и третьим входами блока управления, отличающийся тем, что, с целью повышения точности преобразования, в него введены усилитель постоянного тока, первый и второй дополнительные источники опор ных напряжений, дополнительный накопительный конденсатор, блокирующий конденсатор, первый, второй, третий и четвертый ключи, управляемый генератор тока, причем первый вход усилителя постоянного тока соединен с первым входом второго компаратора, вь1ход усилителя постоянного тока через первый ключ подключен к 1|ервой обкладке дополнительного накопитель ного конденсатора и к управляющему входу управляемого генератора тока выход которого соединен с выходом повторителя напряжения, первая обкладка блокирующего конденсатора под ключена к первому входу третьего ком паратора, вторые обкладки дополнительного накопительного и блокирующего конденсаторов и второй вход уси лителя постоянного тока соединены с шиной нулевого потенциала, выход пер вого дополнительного источника опорного напряжения через второй ключ подключен ко второму выводу токозадающего резистора, первый вход первого компаратора через третий ключ соединен со вторыми входами второго и третьего компараторов, к которым через четвертый ключ подключен выход второго дополнительного источника опорного напряжения, четвертый вход блока управления является входом установки в исход1тЬе состояние логарифмического преобразователя амплитуды импульсов, первый выход блока управления соединен с управляющим .входом блока усиления, второй, трети четвертый и пятый выходы блока управления подключены к управляющим входам соответственно четвертого, третьего, первого и второго ключей, второй выход блока управления является выходом логарифмического преобразователя амплитуды импульсов. 2. Преобразователь по п. 1, о т личающийся тем, что блок, управления содержит первый и второй триггеры, первый и второй элементы И, первый и второй элементы ИЛИ и одновибратор, причем выход первого триггера соединен с первыми входами первого элемента И и второго элемента ИЛИ, выход первого элемента И подключен к первым входам первого три1- гера и первого элемента ИЛИ, вход второго триггера через одновибратор соединен со вторым входом первого элемента ИЛИ, выход которого подключен ко второму входу второго триггера, выход которого соединен с первым входом второго элемента И, второй вход которого подключен ко второму входу первого элемента И, инверсный выход второго триггера соединен со вторым входом второго элемента ИЛИ, входы установки в исходное состояние первого и второготриггеров соединены, первый вход второго триггера является первым входом блока управления, второй вход первого элемента И является вторым входом блока управления, второй вход первого три|- гера является третьим входом блока управления, четвертым входом которого является вход установки в исходное состояние первого триггера, выходы второго элемента И и первого триггера являются соответственно первым и вторым выходами блока управлевым и вторым выходами блока управления, инверсный выход первого триггера является третьим выходом блока управления, инверсный выход второго триггера является четвертым выходом блока управления, пятым выходом которого является выход второго элемента ИЛИ, Источники информации, принятые во внимание при экспертизе 1,Авторское свидетельство СССР If 373782, кл. G Об G 7/2, 1971. 2.Авторское свидетельство СССР № 387517, кл. Н 03 К 13/02, 1971 протитип).

о

Фи.г

| название | год | авторы | номер документа |

|---|---|---|---|

| ИЗМЕРИТЕЛЬ СКОРОСТИ ЗВУКА | 1998 |

|

RU2152597C1 |

| Устройство для считывания информации из доменной памяти | 1988 |

|

SU1558226A1 |

| Устройство для идентификации частиц | 1986 |

|

SU1382210A1 |

| Цифровой синтезатор частот | 1986 |

|

SU1401552A1 |

| Аналоговое запоминающее устройство | 1979 |

|

SU841057A1 |

| Логарифмический аналого-цифровой преобразователь | 1990 |

|

SU1725397A1 |

| Функциональный генератор | 1983 |

|

SU1120364A1 |

| Устройство для моделирования @ -фазного вентильного электродвигателя | 1990 |

|

SU1797133A1 |

| Аналого-цифровой преобразователь | 1986 |

|

SU1388987A1 |

| Преобразователь напряжение-цифровой код | 1978 |

|

SU1075402A1 |

Авторы

Даты

1982-02-07—Публикация

1980-05-07—Подача