Изобретение относится к специализированным средствам вычислительной техники и может быть использовано для оперативного статистического анализа случайных процессов в различных областях техники.

Известно устройство для анализа распределения экстремальных значений, которое на бумаге регистратора строит координаты максимумов и минимумов исследуемого процесса и содержит кольцевой магнитный регистратор, две магнитных головки, усилители-нориализаторы ключ, дифферен0иальные усилители, источник опорных напряжений, формирователь служебных сигналов, регистратор, коммутатор, два преобразователя числа импульсов в год, два элемента НЕ, элемент И, триггер р.

К недостаткам данного устройства можно отнести его сложность, вывод информации на бумагу регистратора, что требует последующей ручной обработки, отсутствие возможности ввода полученных результатов в ЭВМ. Кроме того, это устройство не строит распределения экстремальных пар максимум-минимум по коэффициентам ассиметрии (соотношение максимума и последовавшего за ним минимума), что требуется, например, в ряде случаев при расчетах металлоконструк ций на прочность.

10

Наиболее близким по технической сущности к предлагаемому является устройство для получения полусумм и полуразностей экстремальных значений случайного процесса 2}.

15

Устройство содержит параллельно подключенные к источнику исследуемого сигнала пороговые устройства, каждое из которых связано с двумя дифференцирующими усили.елями, два

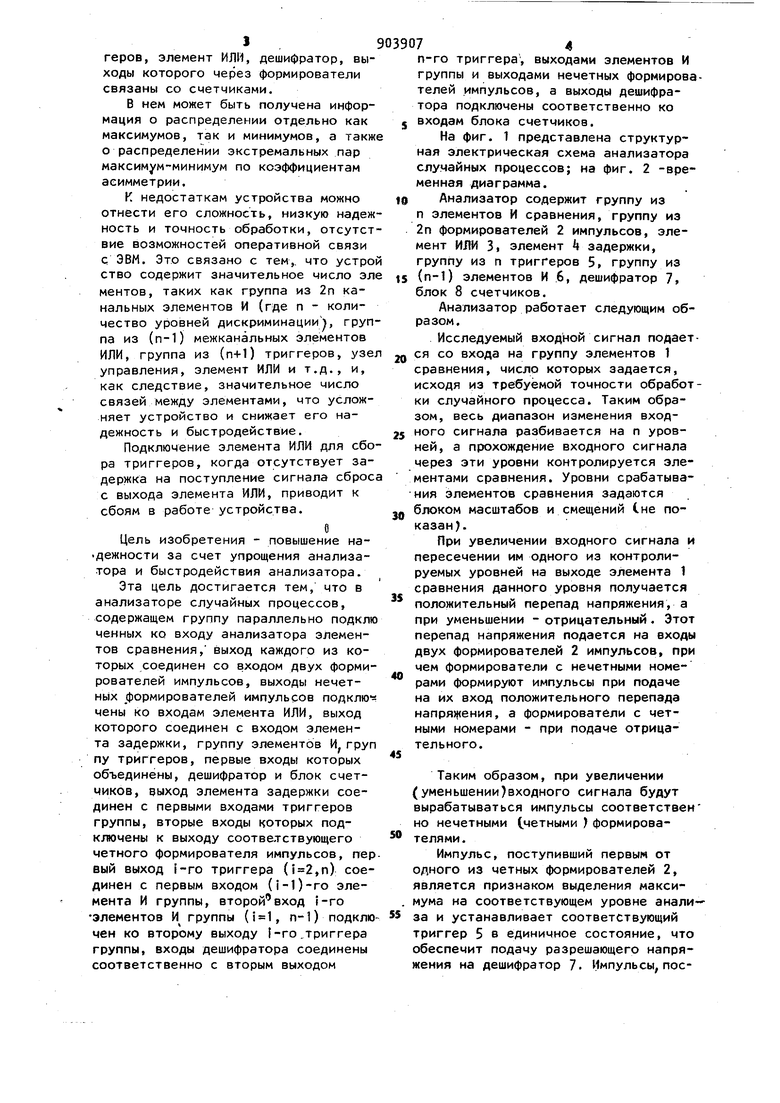

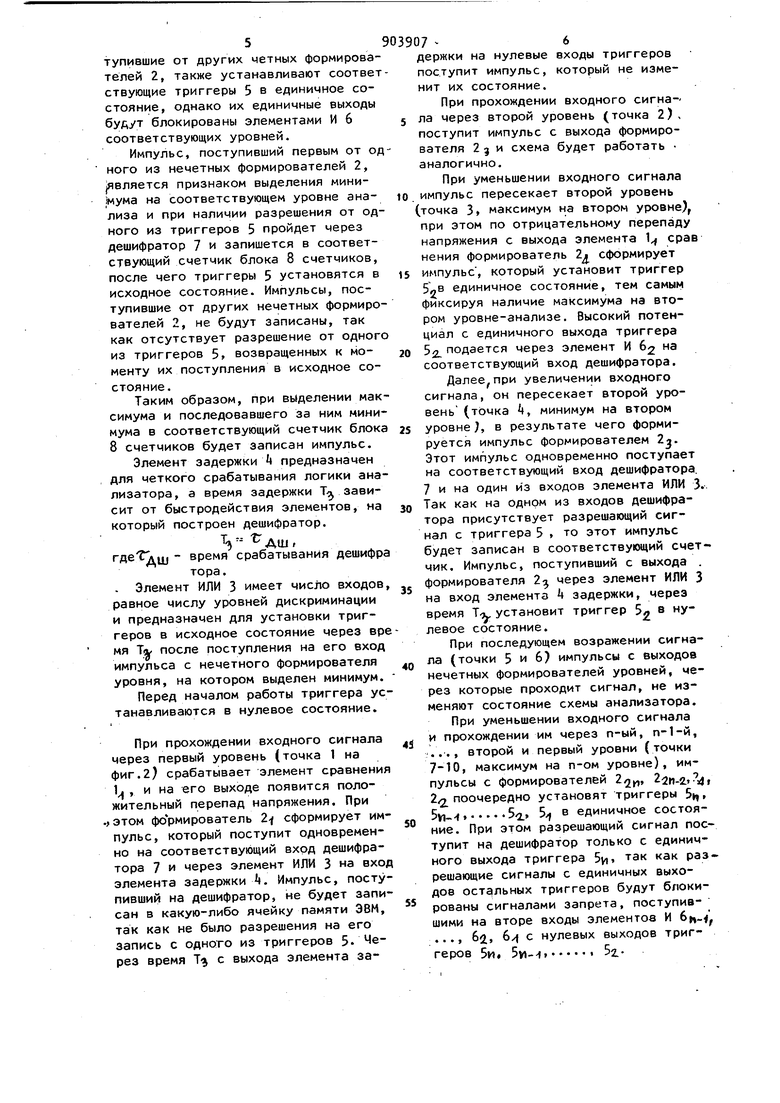

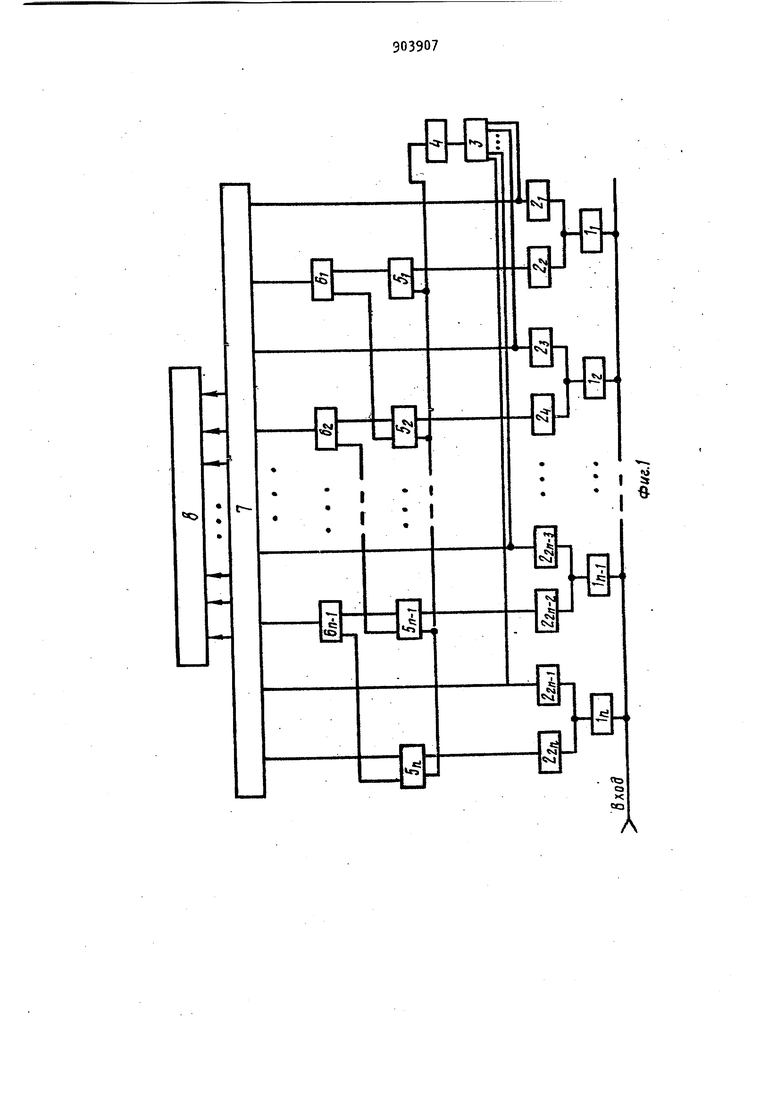

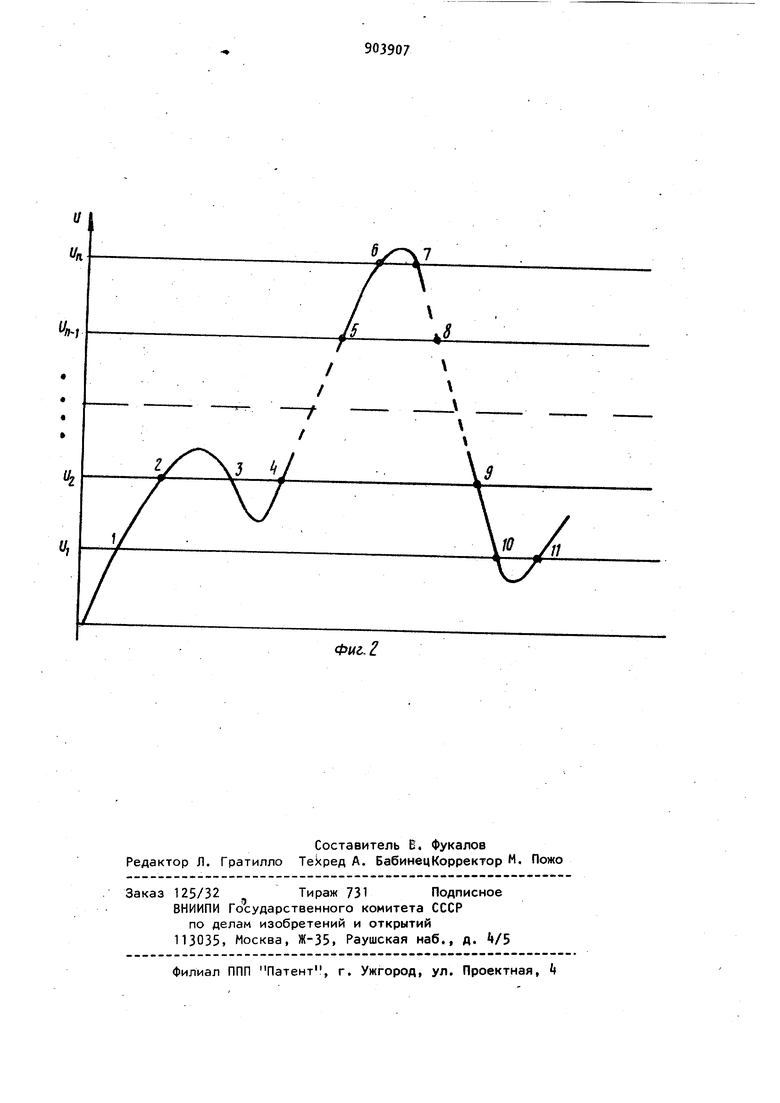

20 элемента ИЛИ, две линии задержки, управляющий триггер, две группы канальных элементов И, группу межканальных элементов ИЛИ, группу три| геров, элемент ИЛИ, дешифратор, выходы которого через формирователи связаны со счетчиками, В нем может быть получена информация о распределении отдельно как максимумов, так и минимумов, а такж о распределении экстремальных пар максимум-минимум по коэффициентам асимметрии. К недостаткам устройства можно отнести его сложность, низкую надеж ность и точность обработки, отсутст вие возможностей оперативной связи С ЭВМ. Это связано с тем,, что устро ство содержит значительное число эл ментов, таких как группа из 2п канальных элементов И (где п - количество уровней дискриминации , груп па из (п-1) межканальных элементов ИЛИ, группа из (п+1) триггеров, узе управления, элемент ИЛИ и т.д., и, как следствие, значительное число связей между элементами, что усложняет устройство и снижает его надежность и быстродействие. Подключение элемента ИЛИ для сбо ра триггеров, когда отсутствует задержка на поступление сигнала сброс с выхода элемента ИЛИ, приводит к сбоям в работе устройства. Цель изобретения - повышение надежности за счет упрощения анализатора и быстродействия анализатора. Эта цель достигается тем, что в анализаторе случайных процессов, содержащем группу параллельно подкл ченных ко входу анализатора элементов сравнения, выход каждого из которых соединен со входом двух форми рователей импульсов, выходы нечетных формирователей импульсов подклю цены ко входам элемента ИЛИ, выход которого соединен с входом элемента задержки, группу элементов И, гру пу триггеров, первые входы которых объединены, дешифратор и блок счетчиков, выход элемента задержки соединен с первыми входами триггеров группы, вторые входы которых подключены к выходу соотве-тствующего четного формирователя импульсов, пе вый выход i-ro триггера (,n) соединен с первым входом (i-l)-ro элемента И группы, второйвход i-ro элементов И группы (i 1, п-1) подклю чен ко второму выходу 1-го .триггера группы, входы дешифратора соединены соответственно с вторым выходом 74 п-го триггера, выходами элементов И группы и выходами нечетных формирователей импульсов, а выходы дешифратора подключены соответственно ко входам блока счетчиков. На фиг. 1 представлена структурная электрическая схема анализатора случайных процессов; на фиг. 2 -временная диаграмма. Анализатор содержит группу из п элементов И сравнения, группу из 2п формирователей 2 импульсов, элемент ИЛИ 3, элемент k задержки, группу из п триггеров 5, группу из (п-1) элементов И 6, дешифратор 7, блок 8 счетчиков. Анализатор работает следующим образом. Исследуемый входной сигнал подается со входа на группу элементов 1 сравнения, число которых задается, исходя из требуемой точности обработки случайного процесса. Таким образом, весь диапазон изменения входного сигнала разбивается на п уровней, а прохождение входного сигнала через эти уровни контролируется элементами сравнения. Уровни срабатывания элементов сравнения задаются блоком масштабов и смещений Сне показан). При увеличении входного сигнала и пересечении им одного из контролируемых уровней на выходе элемента 1 сравнения данного уровня получается положительный перепад напряжения, а при уменьшении - отрицательный. Этот перепад напряжения подается на входы двух формирователей 2 импульсов, при чем формирователи с нечетными номерами формируют импульсы при подаче на их вход положительного перепада напря)(ения, а формирователи с четными номерами - при подаче отрицательного. Таким образом, п.ри увеличении (уменьшении)входного сигнала будут вырабатываться импульсы соответствен но нечетными (четными ) формирователями. Импульс, поступивший первым от одного из четных формирователей 2, является признаком выделения максимума на соответствующем уровне анализа и устанавливает соответствующий триггер 5 в единичное состояние, что обеспечит подачу разрешающего напряжения на дешифратор 7. Импульсы, поступившие от других четных формирователей 2, также устанавливают соответствующие триггеры 5 в единичное состояние, однако их единичные выходы будут блокированы элементами И 6 соответствующих уровней.

Импульс, поступивший первым от одного из нечетных формирователей 2, (Является признаком выделения мини1мума на соответствующем уровне анализа и при наличии разрешения от одного из триггеров 5 пройдет через дешифратор 7 и запишется в соответствующий счетчик блока 8 счетчиков, после чего триггеры 5 установятся в исходное состояние. Импульсы, поступившие от других нечетных формирователей 2, не будут записаны, так как отсутствует разрешение от одного из триггеров 5, возвращенных к моменту их поступления в исходное состояние.

Таким образом, при выделении максимума и последовавшего за ним минимума в соответствующий счетчик блока 8 счетчиков будет записан импульс.

Элемент задержки предназначен для четкого срабатывания логики анализатора, а время задержки Т зависит от быстродействия элементов, на который построен дешифратор.

Т -ЕГАШ, гдеТдщ - время срабатывания дешифра

тора.

. Элемент ИЛИ 3 имеет число входов, равное числу уровней дискриминации и предназначен для установки триггеров в исходное состояние через время То. после поступления на его вход импульса с нечетного формирователя уровня, на котором выделен минимум.

Перед началом работы триггера устанавливаются в нулевое состояние.

При прохождении входного сигнала через первый уровень (точка 1 на фиг.2) срабатывает элемент сравнения 1., и на его выходе появится положительный перепад напряжения. При этом формирователь 2- сформирует импульс, который поступит одновременно на соответствующий вход дешифратора 7 и через элемент ИЛИ 3 на вход элемента задержки k. Импульс, поступивший на дешифратор, не будет записан в какую-либо ячейку памяти ЭВМ, так как не было разрешения на его запись с одного из триггеров 5-Через время Т с выхода элемента задержки на нулевые входы триггеров поступит импульс, который не изменит их состояние.

При прохождении входного сигна-5 ла через второй уровень (точка 2), поступит импульс с выхода формирователя 2 5 и схема будет работать аналогично.

При уменьшении входного сигнала

0 импульс пересекает второй уровень (точка 3 максимум на втором уровне), при этом по отрицательному перепаду напряжения с выхода элемента 1 срав нения формирователь 2д сформирует

5 импульс , который установит триггер ЗяВ единичное состояние, тем самым фиксируя наличие максимума на втором уровне-анализе. Высокий потенциал с единичного выхода триггера

0 52. подается через элемент И 62 на соответствующий вход дешифратора. Далее,при увеличении входного сигнала, он пересекает второй уровень (точка , минимум на втором

5 уровне), в результате чего формируется импульс формирователем 2j. Этот импульс одновременно поступает на соответствующие вход дешифратора. 7 и на один из входов элемента ИЛИ 3.

0 Так как на одном из входов дешифратора присутствует разрешающий си1- нал с триггера 5 то этот импульс будет записан в соответствующий счетчик. Импульс, поступивший с выхода . формирователя 2 через элемент ИЛИ 3 на вход элемента U задержки, через время TX, установит триггер 5л в нулевое состояние.

При последующем возражении сигна- ла (точки 5 и 6) импульсы с выходов нечетных формирователей уровней, через которые проходит сигнал, не изменяют состояние схемы анализатора. При уменьшении входного сигнала и прохождении им через п-ый, п-1-й, ..., второй и первый уровни (точки 7-10, максимум на п-ом уровне), импульсы с формирователей 22 22n-2. 2 поочередно установят триггеры 5ц, , 5/J в единичное состояние. При этом разрешающий сигнал поступит на дешифратор только с единичного выхода триггера 5щ к как разрешающие сигналы с единичных выходов остальных триггеров будут блокированы сигналами запрета, поступившими на вторе входы элементов И ( ..., 6ii, 6х| с нулевых выходов триггеров 5и, SiПри дальнейшем увеличении сигнала и прохождении им через первый ур вень анализа (точка 11, минимум-на первом уровне) с формирователя 2 поступит импульс через дешифратор 7 в соответствующий счетчик. Далее анализатор работает аналогично. В счетчиков каждому уровню дискриминации выделена определенная группа счетчиков, номер группы и чис ло Счетчиков в ней равны номеру уро ня, В ячейках i-ой группы хранится информация о количестве выделенных экстремальных пар максимум-минимум с максимумами на i-ом уровне и минимумами на 1,2,..., i-OM уровнях ( в первой ячейке i-ой группы записано количество экстремальных пар с максимумом на i-ом уровне, а минимумом на первом, во второй ячейке - с максимумом на i-OM, уровне, а минимумом на втором и т.д. . Коэффициенты асимметрии этих пар равны отношению уровней, на которых выделен максимум и минимум. В результате работы анализатора может быть получена информация о количестве максимумов на i-ом уровне (содержимое всех ячеек |--ой группы) о количестве минимумов на i-ом уровне (содержимое i-ых ячеек всей групп о количестве экстремальных пар с определенными коэффициентами асимметрии (содержимое ячейки внутри группы) , что позволяет отдельно построить распределение максимумов, мини-мумов и экстремальных пар с одинаковыми коэффициентами асимметрии. Таким образом, в анализаторе реализован принцип выделения, регистрации и анализа экстремумов, при котором импульсы, поступившие от четных и нечетных формирователей каждого уровня анализа, анализируются так что первый импульс, поступивший от одного из четных формирователей, считается признаком максимума на соответствующем уровне и запоминается одним из триггеров, что обеспечивает подачу разрешения на соответствующий вход дешифратора, а первый импульс, поступивший от одного из нечетных формирователей, считается признаком минимума) на соответвующем уровне и подается непосредственно на соответствующий вход дешифратора, в результате чего в соответствующий счетчик будет записан импульс, свидетельствующий о выделении экстремальной пары максимум-минимум. Кроме того, импульс, поступивший первый от одного из нечетных формирователей, считается также признаком конца выделения очередной экстремальной пары и признаком начала выделения следующей экстремальной пары, для чего триггеры этим импульсом возвращаются в исход-. ное состояние. Зтот принцип позволяет упростить анализатор и повысить его надежность за счет сокращения числа логических связей и повысить быстродействие анализатора, сократив время обработки и время прохождения сигнала в анализаторе за счет меньшего числа элементов и связей между ними, а также исключить сбои при сбросе триггера и записи импульсов в блок счетчиков. Формула изобретения Анализатор случайных процессов содержащий группу подключенных ко входу анализатора элементов сравнения, выход каждого из которых соединен со входом двух формирователей импульсов, выходы нечетных формирователей импульсов подключены ко входам элемента ИЛИ, выход которого соединен с входом элемента задержки, группу элементов И, группу триггеров, первые входы которых объединены, дешифратор и блок счетчиков, отличающийся тем, что, с целью повышения надежности за счет упрощения и быстродействия анализатора, выход элемента задержки соединен с первыми входами триггеров группы, вторые входы которых подключены к выхо-. ду соответствующего четного формирователя импульсов, первый выход i-ro триггера (,n) соединен с первым входом (i-l)-ro элемента И группы, второй вход 1-го элемента И группы (1-1, п-1) подключен ко второму выходу i-ro триггера группы, входы дешифратора соединены соответственно с вторым выходом п-го триггера, выходами элементов И группы и выходами нечетных формирователей импульсов, а выходы дешифратора подключены соответственно ко входам блока счетчиков. Источники информации, принятые во внимание при экспертизе 1, Авторское свидетельство СССР № , кл. G Об G 7/52, 1975. 2. Авторское свидетельствоСССР № 332472,кл.С06 G 7/52,1972 прототип .

| название | год | авторы | номер документа |

|---|---|---|---|

| Статистический анализатор | 1980 |

|

SU896642A1 |

| Статистический анализатор | 1980 |

|

SU898457A1 |

| УСТРОЙСТВО для ПОЛУЧЕНИЯ ПОЛУСУММи | 1972 |

|

SU332472A1 |

| Устройство для определения локальных экстремумов | 1982 |

|

SU1032452A1 |

| Устройство для регистрациидиНАМичЕСКиХ дЕфОРМАций | 1977 |

|

SU805060A1 |

| УСТРОЙСТВО для ПОЛУЧЕНИЯ ЗАКОНА РАСПРЕДЕЛЕНИЯ | 1972 |

|

SU328467A1 |

| Устройство для исследования путей в графе | 1982 |

|

SU1076909A1 |

| Устройство для определения взаимной корреляционной функции | 1983 |

|

SU1108463A1 |

| Вычислительное устройство | 1985 |

|

SU1269124A1 |

| Анализатор функций распределения экстремумов | 1982 |

|

SU1091176A1 |

« I в

hS

Авторы

Даты

1982-02-07—Публикация

1980-05-07—Подача