54) АНАЛОГО-ЦИФРОВОЙ ИНТЕГРАТОР

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналого-цифровой интегратор | 1977 |

|

SU732905A1 |

| Цифровой измеритель активных сопротивлений | 1985 |

|

SU1308936A1 |

| Аналого-цифровой интегратор | 1979 |

|

SU813456A2 |

| Аналого-цифровой интегратор | 1980 |

|

SU866563A1 |

| Интегратор | 1978 |

|

SU748438A1 |

| Аналого-цифровой интегратор | 1977 |

|

SU682908A2 |

| Устройство для интегрирования электрического сигнала | 1982 |

|

SU1115066A1 |

| Способ аналого-цифрового преобразования с весовым интегрированием и устройство для его реализации | 1981 |

|

SU953722A1 |

| Устройство для интегрирования постоянного тока | 1983 |

|

SU1166144A1 |

| Аналого-цифровой преобразователь сопротивления | 1983 |

|

SU1108369A1 |

1

изобретение относится к автоматике и вычислительной технике и предназначено для формирования напряжения, пропорционального интегралу от входного сигнала. Оно может использоваться в системах автоматического управления различных технологических процессов и объектов, когда требуются большие постоянные интегрирования Известны устройства для интегрирования, содержащие последовательно включенные преобразователь напряжение - частота, реверсивный счетчик импульсов и цифроаналоговый преобразователь. Эти устройства, работающие по принципу квантования интеграла входного сигнала и последующего запоминания числа квантов в реверсивном счетчике импульсов, позволяют получать большие постоянные интегрирования при малых емкостях интегрирующего конденсатора ГИ

Однако они имеют низкую помехоустойчивость, так как сбои счетчика под действием различного рода помех вызывают разрушение информации, накопленной интегратором, что во многих случаях недопустимо.

Наиболее близким по технической -сущности к предлагаемому является

аналого-цифровой интегратор, в котором устраняются указанные недостатки путем введения канала восстановления информации, выполненного на осг нове блока аналоговой -памяти и блока сравнения. Устройство содержит последовательно включенные входной резистор, аналоговый интегратор с цепью сброса, компаратор, реверсивный счетчик импульсов, цифроаналоговый преобразователь, блок аналоговой. памяти и блок сравнения, другой вход которого подключен к выходу цифроаналогового преобразователя, а выход соединен с дополнительным входом аналогового интегратора 2 .

Однако в данном устройстве при длительном воздействии входного сигнала одного знака происходит переполнение реверсивного счетчика импульсов в результате чего нарушается нормальная работа интегратора.

для исключения переполнения счетгчика аналого-цифровой интегратор должен содержать контур ограничения. Применение для этих целей простых схем ограничения на диодах, стабилитронах или транзисторах связано с сокращением диапазона выходного сигнала интегратора и снижением его точности.

Применение для двухстороннего ограничения двух операционных усилителей с соответствующими цепями частотной коррекции, задания входных токов и коэффициентов усиления ведет к усложнению интегратора, а наличие квантования по уровню в аналогоцифровых интеграторах приводит к возникновению автоколебаний при охвате такого интегратора глубокой отрицательной Обратной связью через схемы ограничения.. Необходимость уменьшения амплитуды автоколебаний требует специальных мер, усложняющих устройство в целом.

Наконец, во многих случаях, например, при использовании аналого-цифровых интеграторов в программно-временных устройствах возникает необходимость автоматического перехода на новый уровень ограничения с постоянной скоростью, не зависящей от входного сигнала. Известные аналого-цифровые интеграторы не обеспечивсцот такой режим работы, что ограничивает их нкциональные возможности.

Цель изобретения - повышение точности интегрирования и упрощение интегратора.

Для достижения поставленной цели в аналого-цифровой интегратор, содер,жащий последовательно соединенные интегрирующий усилитель, компаратор управляемый делитель частоты, реверсивный счетчик импульсов, цифроаналоговый преобразователь, блок памят| и блок сравнения, другой вход которого подключен к выходу цифроаналогового преобразователя, а выход - к управляющему входу блока памяти и к суммирующему входу интегрирующего усилителя, и блок ограничения, вход которого соединен с выходом цифроаналогового преобразователя, введены нелинейный элемент, токозадающий блок, инвертор, элемент ИЛИ и переключатель, сигнальные входы которого соединены соответственно с первым выходом и через токозадающий блок - со вторым выходом блока ограничения соединенным со входом нелинейного элемента, выход, которого подключен к первому управляющему входу управляемого делителя частоты, к первому входу и через инвертор - ко второму входу элемента ИЛИ и второму управляющему входу управляемого делителя частоты, третий управляющий вход которого соединен с выходом блока сравнения, выход элемента ИЛИ подключен к управляющему входу переключателя, выходом соединенного с суммирующим входом интегрирующего усилителя, управляющие входы блока ограничения подключены к знаковым выходам реверсивного счетчика импульсов , а установочный вход блока ограничения соединен свыходом интегрирую1чего усилителя; при этом блок ограничения выполнен на операционном усилителе, выход которого через две цепи из последовательно соединенных первого резистора и первого диода подключен к первому выходу блока ограничения, в каждой цепи общий вывод первого резистора и первого диода через второй резистор подключен к

соответствующему источнику разнополярных напряжений и через второй диод - к соответствующему источнику тока уставки и выходу второго и третьего переключателей соответственно, входы каждого из которых соединены соответственно с шиной нулевого потенциала и суммирующим входом блока ограничения, а управляющие вход являются управляющими входгиии блока ограничения.

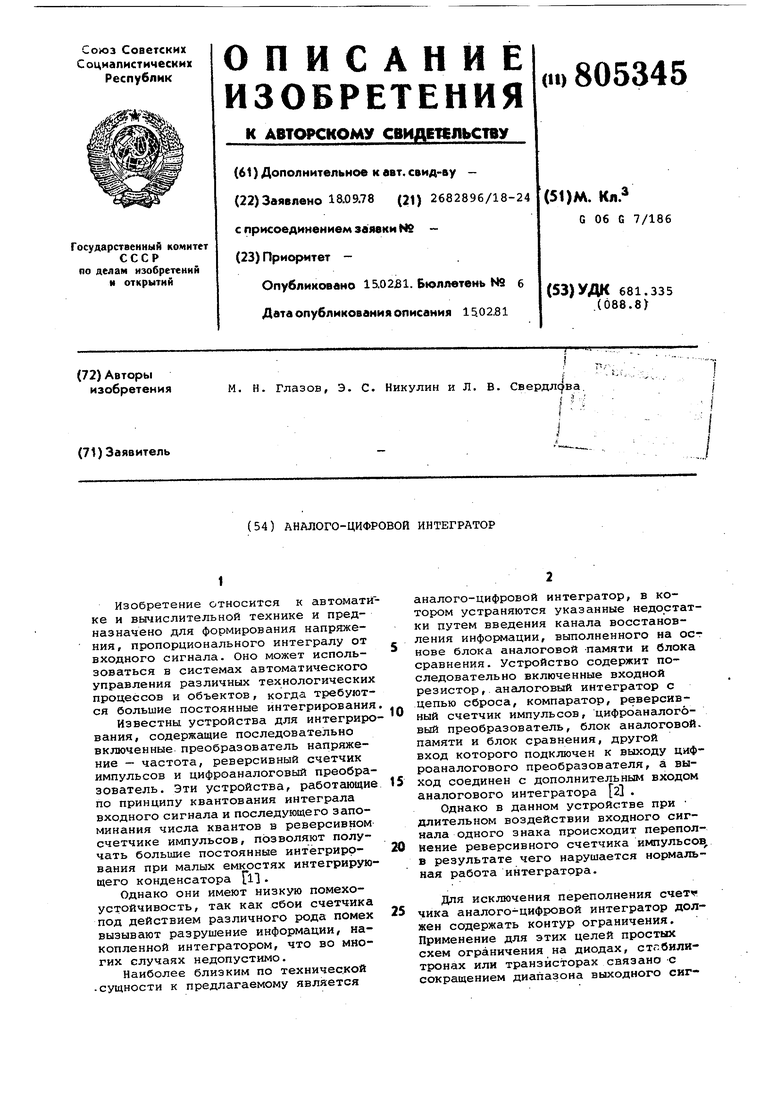

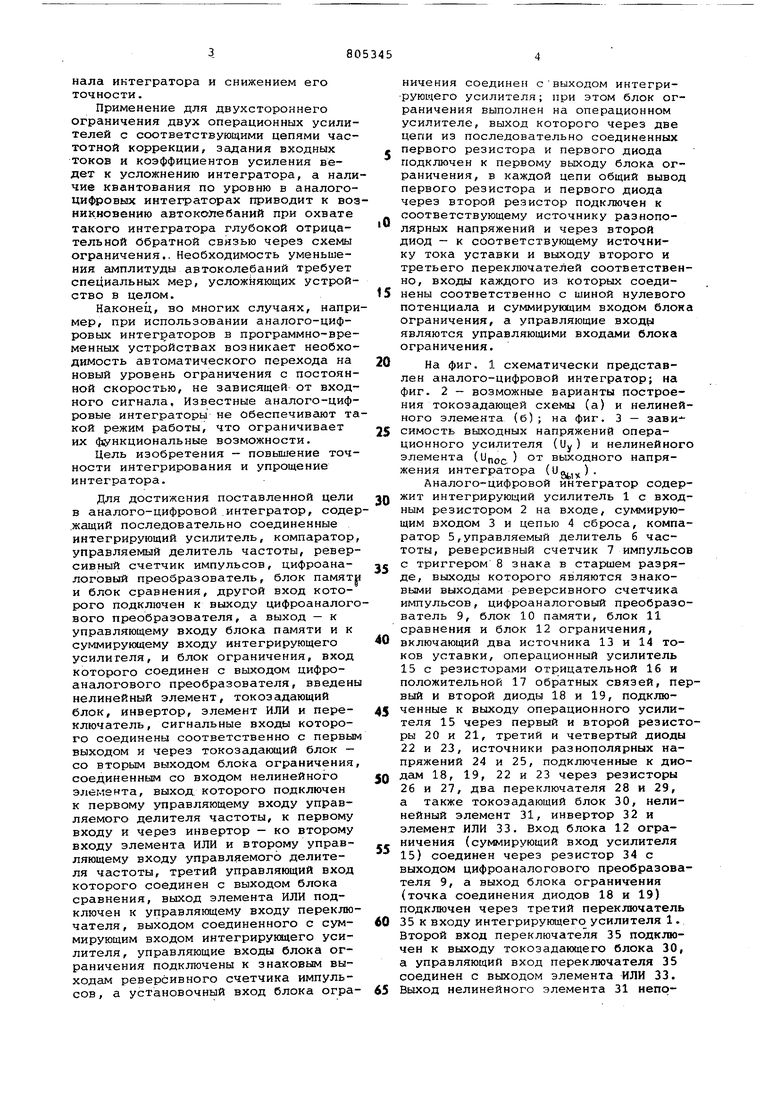

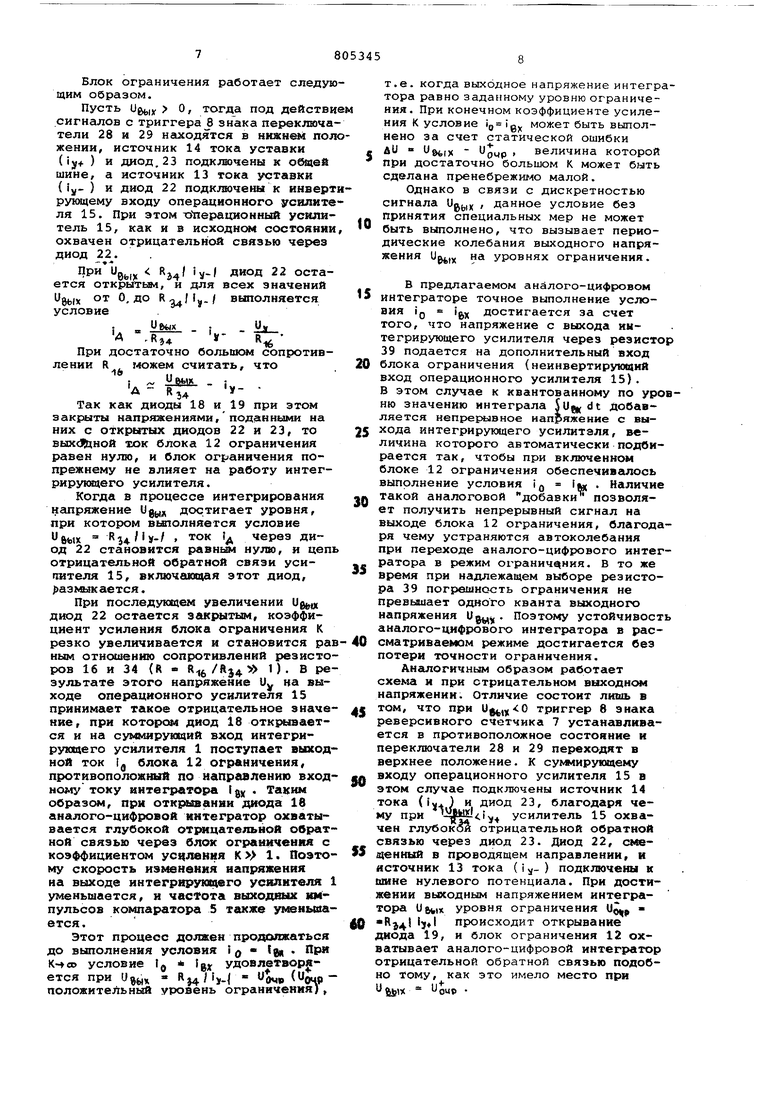

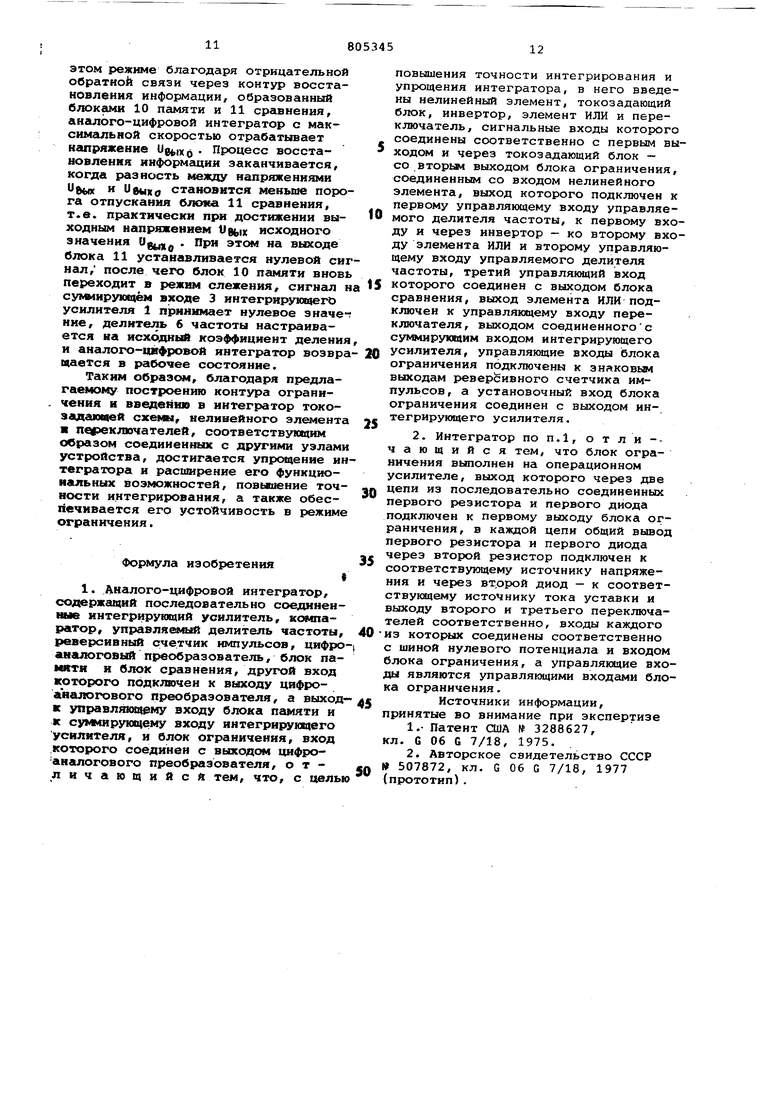

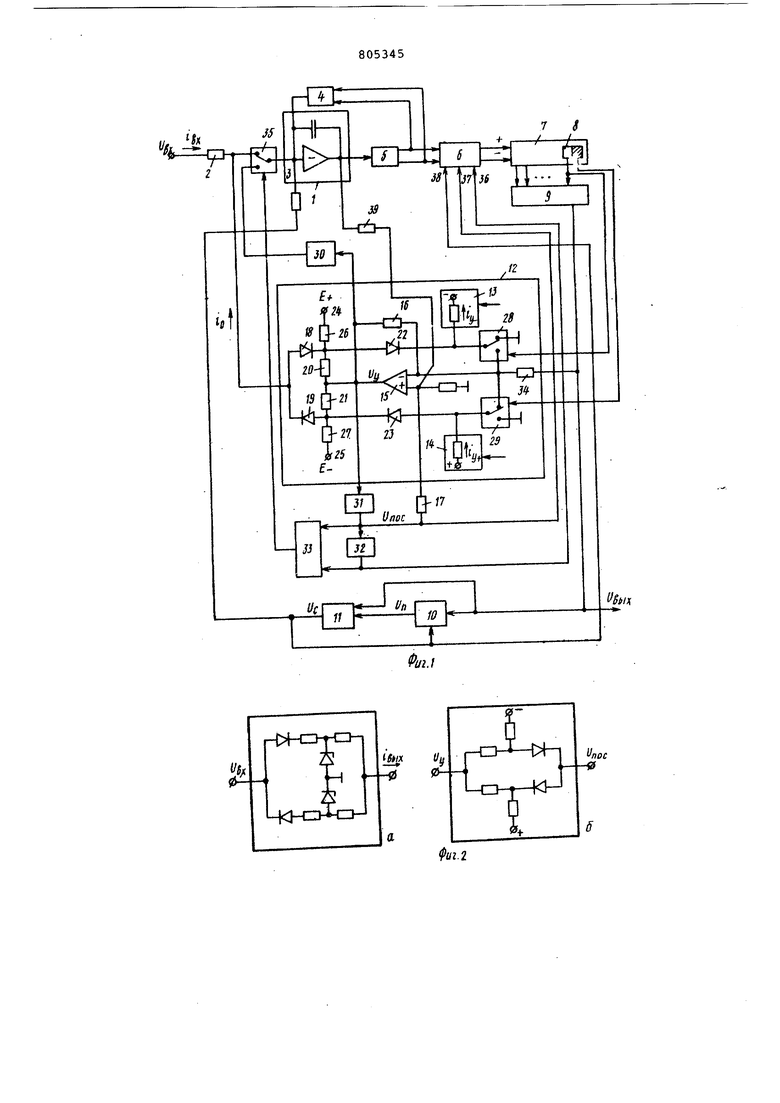

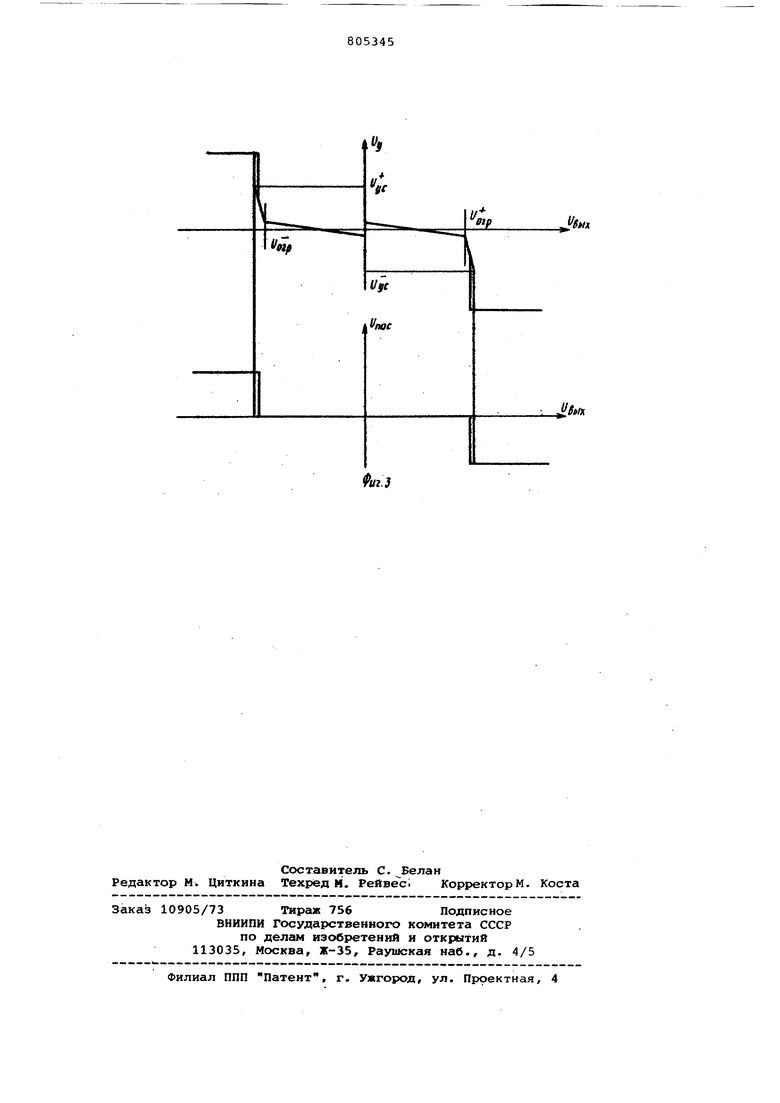

0 На фиг. 1 схематически представлен аналого-цифровой интегратор; на фиг. 2 - возможные варианты построения токозадающей схемы (а) и нелинейного элемента (б) ; на фиг. 3 - зави- 5 симость выходных напряжений операционного усилителя (Uy) и нелинейного элемента (Uf,(jc.) ° выходного напряжения интегратора (ио,,,).

Аналого-цифровой интегратор содерQ жит интегрирующий усилитель 1 с входным резистором 2 на входе, суммирующим входом 3 и цепью 4 сброса, компаратор 5,управляемый делитель 6 частоты, реверсивный счетчик 7 импульсов

C с триггером 8 знака в старшем разряде, выходы которого являются знаковыми выходами реверсивного счетчика импульсов, цифроаналоговый преобразователь 9, блок 10 памяти, блок 11 сравнения и блок 12 ограничения,

0 включающий два источника 13 и 14 токов уставки, операционный усилитель 15 с резисторами отрицательной 16 и положительной 17 обратных связей, первый и второй диоды 18 и 19, подключенные к выходу операционного усилителя 15 через первый и второй резисторы 20 и 21, третий и четвертый диоды 22 и 23, источники разнополярных напряжений 24 и 25, подключенные к диоQ дам 18, 19, 22 и 23 через резисторы 26 и 27, два переключателя 28 и 29, а также токозадающий блок 30, нелинейный элемент 31, инвертор 32 и элемент ИЛИ 33. Вход блока 12 ограничения (суммирующий вход усилителя 15) соединен через резистор 34 с выходом цифроаналогового преобразователя 9, а выход блока ограничения (точка соединения диодов 18 и 19) подключен через третий переключатель

0 35 к входу интегрирующего усилителя 1. Второй вход переключателя 35 подключен к выходу токозадающего блока 30, а управляющий вход переключателя 35 соединен с выходом элемента ИЛИ 33.

5 Выход нелинейного элемента 31 непрсредственно и через инвертор 32 подключен к управляющим входам 36 и 37 делителя 6 частоты. Третий управляющий вход 38 делителя б частоты соединен с выходом блока 11 сравнения. Управляющие входы переключателей 28 и 29 соединены со знаковыми выходами реверсивного счетчика 7 импульсов. При этом первые входы переключателей 28 и 29 соединены с шиной нулевого потенциала, а вторые входы этих переключателей подключены к суммирующему входу, операционного усилителя 15. Блок ограничения имеет также установочный вход (неинвертирунвдий вход операционного усилителя 15), к которому через резистор 39 подключен выход интегрирующего усилителя 1.

Токозадающий блок {фиг. 2) построей на стабилитронах, задающих напряжения на резисторах, подключаемых переключателем 35 к сукпиирующему входу интегрирующего усилителя 1.

Нелинейный элемент выполнен на основе диодных ключей, диоды которых смещены в непроводящем направлении с помощью источников напряжения прртивположной полярности.

Работа аналого-цифрового интегратора происходит следующим образом.

В исходном, состоянии при отсутствии входного сигнала и нулевых начальных условиях реверсивнь(й счетчик

7импульсов находится в состоянии, при котором выходное напряжение И цифроаналогового преобразователя 9 равно нулю. Блок 10 памяти работает в режиме слежения за выходным, сигналом . Поэтому выходные напряжения блока 10 памяти (Uf) и блока

11 сравнения (11) равны нулю. Нулевое выходное напряжение 1) удерживает блок 10 памяти в режиме слежения и не оказывает влияния на интегрирующий усилитель 1 и управляемый делитель б частоты. Триггер 8 знака реверсивного счетчика 7 устанавливает переключатели 28 и 29 в нижнее положение, так что диод 22 и источник 13 тока уставки подключаются к суммирующему входу операционного усилителя 15. При этом усилитель 15 охватывается глубокой отрицательной об ратной связью через диод 22.

Диод 23 смещен в проводящем.направлении напряжением Е источника 25

Поскольку диоды la и 1У закрыты . напряжениями Цд к Цд, приложенньоми к ним с открытых диодов 22 и 23, блок ограничения отключен от интегрирующего усилителя 1. Благодаря тому, что диоды 18 и 19 находятся под весьма малыми и противоположными по знак обратными напряжениями, результирующий ток утечки этих диодов оказывает пренебрежимо малое влияние на смещение нуля интегрирующего усилителя 1.

8исходном состоянии напряжение Uy

на выходе операционного усилители 15 лежит в зоне нечувствительности нелинейного элемента 31 (фиг. 3),, а потому цепь положительной обратной связи усилителя 15 разомкнута и на , вход&х элемента ИЛИ 33 и на управляющих входах 36 и 37 дглителя 6 частоты действуют нулевые си1налы, благодаря чему переключатель 35 находится в верхнем положении, а делитель 6 частоты настроен на максимальный коэффициен т деления (постоянная интегрирования аналого-цифрового интегратора максимальная).

Для рассматриваемого интегратора характерны следующие режимы работы: интегрирование сограничением выходного сигнала на минимальном и максимальном уровнях; управляемое ограничение выходного сигнсша; восстановление информации после сбоев счетчика.

В режиме интегрирования ycTjjoftcTво работает при т 0. При этЬм на выходе компаратора 5 возникают импульсы с частотой, пропорциональной t, которые в зависимости от знака .поступают на суммируютдай или вычитающий вход реверсивного счетчика 7 импульсов. За каждый период работы ко паратора 5 в счетчике 7 фиксируетсявеличина и знак приргицения интеграла входного напряжения Ugj , т.е. осуществляется квантование интеграла входного сигнала по уровню. Такюи образом, в счетчике 7 формируется цифровой код М, характеризующий квантованное значение интеграла SUex которое с помощью цифроаналогового преобразователя 9 Лреобразуется в -эквивалентное электрическое напряжение и

6bt)t

При нормальной работе аналогоцифрового интегратора (без сбоев счетчика) блок 10 памяти остается в рюжимё слежения за выходным сигналом Ug(,, , поскольку скорость слежения блока 10 ВБйирается выше максимальной скорости изменения Uj . Поэтому разность напряжений.на входа блока 11 сравнения не превыаает одного кванта сигнала Ugj и находится в зоне нечувствительности блока 11, в результате чего его выходное напряжение имеет нулевое значение, по которому блок 10 памяти работает в режиме слежения за напряжением Uy,, , а делитель 6 частоты настроен на максимальный коэффициент деления. До тех пор пока напряжение , лежит в зоне

i у I

V

и- о

г-

где 1у, ij, - токи уставки, Rj сопротивление резистора 34, блой 12 ограничения находится в состоянии, при котором диоды 18 и 19 и ток с выхода операционного усилителя 15 не поступает на. суммирующий вход интегрирующего усилителя 1. Блок ограничения работает следую щим образом. Пусть О, тогда под действи сигналов с триггера J знака переключа тели 28 и 29 находятся в нижнем по; жении, источник 14 тока уставки (У4 ) и диод, 23 подключены к общей шине, а источник 13 тока уставки ( iy- ) и диод 22 пoдкJгoчeны к инверт рующему входу операционного усилите ля 15. При этом тзперашюнный усилитель 15, как и в исходном состоянии охвачен отрицательной связью через диод 2Д. ПриЦц, Rj4/ диод 22 остается открытьам, и для всех значений Ugt,,x от О, до выполняется условие А ftj4. При достаточно большом сопротивлении R можем считать, что 1в .. i сг - i,. . «34 Так как диоды 18 и 19 при этом закрыты напряжениями, поданными на них с открытых диодов 22 и 23, то выхсЗ ной хок блока 12 ограничения равен нулю, и блок ограничения попрежнему не влияет на работу интегрирукйцего усилителя. Когда в процессе интегрирования нгшряжение Ugy достигает уровня, при котором вьтолняется условие Uj,, А диод 22 становится равным нулю, и цеп отрицательной обратной связи усигштеля 15, включающая этот диод, размьжается. При последующем увеличении Ug{ диод 22 остается закрытым, коэффициент усиления блока ограничения К резко увеличивается и становится ра ным отнсшенню сопротивлений резисто ров 16 и 34 (R - Й16/Й34 1). В ре зультате этого напряжение U на выходе операционного усилителя 15 принимает такое отрицательное значе ние, при котором диод 18 открывается и на с «мирую«ий вход интегрирующего усилителя 1 поступает выход ной ток Ig блока 12 ограничения, противоположный по направлению вход ному току интегратора I gy . Тахю образом, при открывании диода 18 аналого-цифровой интегратор охватывается глубокой от1мцательной обрат ной связью через блох ограиичення с коэффициентом усцлекия К 1. Поэто му скорость изменения напряжения на выходе интегрнруюв го усилителя уменьшается, и частота выходйых кмпульсоБ компаратора 5 также умвныел ется. Этот процесс должен продолжаться до выполнения условия Q ten При K-tcD условие Ig Ig; удовлетворяется при и - Rj4/j-r положительный уровень ограничения), т.е. когда выходное напряжение интегратора равно заданному уровню ограничения. При конечном коэффициенте усиления К условие ( может быть выполнено за счет статической ошибки all и,)( - , величина которой при достаточно большом К может быть сделана пренебрежш-ю малой. Однако в связи с дискретностью сигнала , данное условие без принятия специальных мер не может быть вьтолнено, что вызывает периодические колебания выходного напряжения и, на уровнях ограничения. В предлагаемом аналого-цифровом интеграторе точное выполнение услодостигается за счет того, что напряжение с выхода интегрирующего усилителя через резистор 39 подается на дополнительный вход блока ограничения (неинвертируюций вход операционного усилителя 15). В этом случае к квантованному по уровню значению интеграла 5Ug,(dt добавляется непрюЕшвное напряжение с выхода интегрирующего усилиталя, величина которого автоматически подвирается так, чтобы при включенном блоке 12 ограничения обеспечивешось выполнение условия i - IM . Наличие такой аналоговой добавки позволяет получить непрерывный сигнал на выходе блока 12 ограничения, благодаря чему устраняются автоколебания при переходе аналого-цифрового интегратора в режим ограничения. В то же время при надлежащем выборе резистора 39 погрешность ограничения не превьшает одного кванта выходного напряжения Ug. Поэтому устойчивость аналого-цифрового интегратора в рассматриваемом режиме достигается без потери точности ограничения. Аналогичным образом работает схема и при отрицательном выходном напряжении. Отличие состоит лишь в том, что при U$fc« 0 триггер 8 знака реверсивного счетчика 7 устанавливается в противоположное состояние и переключатели 28 и 29 переходят в верхнее положение. К суммирующему входу операционного усилителя 15 в этом случае подключены источник 14 тока ( и диод 23, благодаря чему при V4 усилитель 15 охвачен глубокой отрицательной обратной связью через диод 23. Диод 22, смещенный в проводящем направлении, и ИСТОЧНИК 13 тока (-) подключены к шине нулевого потенциала. При достижении выходным напряжением интегратора Ubfcix уровня ограничения U происходит открывание днода 19, и блок ограничения 12 охватывает аналого-цифровой интегратор отрицательной обратной связью подобно Тому, как это имело место при Uftfel Отметим, что как в процессе интегрирования входного напряжения Ug так и при переходе аналого-цифрового интегратора в режим ограничения, напряжение Uj на выходе операциоиного усилителя 15 находится в зоне нечувствительности нелинейного элемента 31. Напряжение Uj достигает максимального значения включенном контуре ограничения, когда U кмaкc Таким образом, при соответствующем выборе порогов аереключенвя U и нелинейный элемент 31 остается в вьослюченном положениц, а потому переключатель 35 и делитель 6 частоты находятся в исходных состояниях. В режиме управляемого огранкчвняя устройство работает сгтяуущюл оОраэсж Этот режим имеет место в том случае, когда по внешнему ynpaBAHKK iiy сигналу происходит перек вочение уставки ограничения так, что вшсодноа напряжение интегратора оказывается выше уставки. При этом под действием большого рассогласования на инверсном входе на выходе операционного усилителя 15 возникает напряжение , превышающее порог пере ключения нелинейного элемента 31, в результате чего операциоинггЗй усилитель 15 охватывается положительной обратной связью через резистор 17 и переходит 6 релейный режшл. Под цействием выходного сигнала нелинейного элемента 31 переклпчатель 35густанавливается в нижнее положение, обеспечивая подключение .блок.а 12 ограничения через токозгщакаций блок 30 к суммиру1СШ1е14у входу интегрирующе го усилштеля 1. Одновременно на соответствующем управляив ем входе (36 или 37) делителя б частоты возникает единичнЁЗв логический сигнал, по которому устанавливается требуемый коэффициент деления делителя 6. Для сопряжения с логическими схемами управляющими перек гвочателем 35 и делителем б частоты, в интеграторе предусмотрен инвертор 32 знака, обес печивакщий иа выходе сигнал логической единицы при отрицательном напряжения на его входе. Под действием выходного сигнала токозада ющего блока 30 напряжение на выходе аналогоцифрового интегратора изменяется в направлении уменьшения рассогласования на входе бжжа ограничения. Благодаря наличию токоэадаяяцего блока 30, формирукйдего постоянный ток на входе интегрирукааего усилителя 1, скорость изменения выходного напр)яже ния аналого-цифрового интегратора в режиме управляемого ограннчения постоянна и не зависит от входного напряжения и , что необходимо при использовании интегратора во многих программно-управляющих устройствах. В то же время за счет уменьшения коэффициента деления делителя 6 переход на заданный уровень ограничения осуществляется с достаточно большой скоростью, благодаря iteMy обеспечивается экстренное снижение выходного напряже ния интегратора в случаях, когда по условиям его применения требуется, например, осуществить аварийное снижение регулнруе юго параметра, определяемого напряжением U (уъп( Процесс изменения выходного напряжения и g продолжается: до тех пор, пока разность тжду напряжени® и заданной уставкой ограничения не уменьшается до величины порога отпускания блока ограничения. При 8тта нелинейный элемент 31 переходит в выключенное положение, в рез} льтате чего переключатель 35 и делитель 6 частоты устанавливаютця в нсходное состояние, обеспечивая работу интегратора с заданной постояяной интегрирования. , Таким образом, в режиме управляемого ограничения схема работает как релейная следящая система с интегрирукяцим исполнительным устройством, В которой трехпозиционный релейный элемент на операционном усилителе 15 выполняет функции усилителя рассогласования, обеспечивая в конечнсм счете равенство напряжения ищ,, заданной уставке. В режиме управляемого ограничения, как и в режиме интегрирования входного сигнала, блок 10 памяти отслеживает выходной напряжение интегратора Ugfciy. Это достнгается за счет того, что скорость слежения этого блока выбирается достаточно большой по сравнению со скоростью изменения напряжения U,. Поэтсму выходной сигнал блока 11 сравнения сохраняется :равнь 4 нулю, что удерживает блок памяти в режиме слежеиия. При сбоях счетчика 7 импульсов аналого-цифровой интегратор .работает следующим образом. В .этом случае достаточно большие (превышающие один квант) изменения сигнала на выходе цифроаналогового преобразователя 9 происходят практически мгновенно, и блок 10 памяти не успевает отрабатывать напряжение . Поэтснлу на выходе блока 11 сравнения возникает единичный сигнал, по которому блок 10 памяти переходит в режим хранения напряжения Uoyjj , предшествовавшего сбок. Одновременно делитель б частоты по сигналу на входе 38 перестраивается на единичный коэффициент деленияг на суммирукмдий вход 3 интегрируквдего усилителя 1 поступает выходное напряжение блока 11 сравнения, и аналого-цифровой интегратор переходит в режим восстановления информации. Р ЭТОМ режиме благодаря отрицательной обратной связи через контур восстановления информации, образованный блоками 10 памяти и 11 сравнения, ангшого-цифровой интегратор с максимальной скоростью отрабатывает напряжение ( Процесс восстановления информгщии заканчивается, когда разность между напряжениями UftMt и U0bix0 становится меньше поро га отпускания блока 11 сравнения. т.е. практически при достижении выходным напряжением исходного значения . При этом на выходе блока 11 устангшливается нулевой си нал, после чего блок 10 памяти внов переходит в режим слежения, сигнал сукмирующём входе 3 интегрирувхцего усилителя 1 п1рнннмает нулевое значе ние, делитель 6 частоты настраивается на исходный коэффициент делени и аналого-цифровой интегратор возвр цается в рабочее состояние. Таким обраэ м«, благодаря предлагаемому построению контура ограничения н введению в интегратор токозадаюцей схемы, нелинейного элемент переключателей, соответствующим оСразом соедииенных с другими узлам устройства, достигается упрощение и тегратора и расширение его функциональных возможностей, повышение точ нести интегрирования, а также обеспечивается его устойчивость в режиме ограничения. Формула изобретения 1. Аналого-цифровой интегратор, содержеш ий последовательно соединенные интегрирукнций усилитель, ктшаратор, управля«« делитель частоты реверсивный счетчик импульсов, цифро аналоговый преобразователь, блок памяти и блох сравнения, другой вход которого подключен к выходу цифроаналогового преобразователя, а выход к управлякяв0му входу блока памяти и к суммирующему входу интегрирующего усилителя, и блок ограничения, вход ,которого соединен с выходом цифроаиалогового преобразователя, о т личаюцийсй тем, что, с цель повьо11ения точности интегрирования и упрощения интегратора, в него введены нелинейный элемент, токозадающий блок, инвертор, элемент ИЛИ и переключатель, сигнальные входы которого соединены соответственно с первым выходом и через токозадающий блок - со вторым выходом блока ограничения, соединенным со входом нелинейного элемента, выход которого подключен к первому управляющему входу управляемого делителя частоты, к первому входу и через инвертор - ко второму входу элемента ИЛИ и второму управляющему входу управляемого делителя частоты, третий управляющий вход которого соединен с выходом блока сравнения, выход элемента ИЛИ подключен к управляющему входу переключателя, выходом соединенногос суьФшрующим входом интегрирующего усилителя, управляющие входы блока ограничения подключены к знаковым выходам 1)еверсивного счетчика импульсов, а установочный вход блока ограничения соединен с выходом интегрирующего усилителя. 2. Интегратор по п.1, о т ли -чающийся тем, что блок ограничения выполнен на операционном усилителе, выход которого через две цепи из последовательно соединенных первого резистора и первого диода подключен к первому выходу блока ограничения, в каждой цепи общий вывод первого резистора и первого диода через второй резистор подключен к соответствующему источнику напряжения и через втррой диод - к соответствукадему источнику тока уставки и выходу второго и третьего переключателей соответственно, входы каждого из которых соединены соответственно с шиной нулевого потенциала и входом блока ограничения, а управлякидие входы являются управлякяцими входами блока ограничения, Источники информации, принятые во внимание при экспертизе 1.- Патент США № 3288627, кл. G 06 G 7/18, 1975. 2. Авторское свидетельство СССР 507872, кл. G 06 G 7/18, 1977 (прототип).

iS

к

fi

НЖэ-t-a-i S

H -KhCO-MZH7 f

Л« (/,

лог

Авторы

Даты

1981-02-15—Публикация

1978-09-18—Подача