Изобретение относится к радиотехнике и может использоваться при построении кодирующих устройств, npftiменяющих дифференциальное кодирование построчно развертываемых изображений для их передачи по цифровому каналу.

Известно устройство формирования сигнала отсчета для дифференциального кодера изображений, содержащее последовательно соединенные семь блоков задержки, первый и второй сумматоры 1.

Однако известное устройство имеет низкую точность формирования сигнала отсчета при наличии в изображении криволинейных контуров.

Цель изобретения - повышение точности формирования сигнала отсчета при наличии в изображении криволинейных контурюв.

Цель достигается тем, что в устройство формирования сигнсша отсчета для дифференциального кодера изображений, содержащее последовательно соединенные семь блоков задержки, первый и второй сумматоры, введены восьмой блок задержки, двенадцать блоков вычисления модуля разности сигналов, третий и четвёртый сумма торы, блок сравнения и четыре ключевых элемента, причем вход восьмого блока задержки подключен к выходу седьмого блока задержки, а к первому и второму входам первого, второго, третьего, четвертого, пятого, шестого, седьмого, восьмого, девятого, десятого, одиннадцатого, двенадцатого блоков вычи сления, модуля разнос10ти сигналов подключены соответственно выходу второго и третьего, третьего и четвертого, четвертого и пятого, первого и третьего, третьего и шестого, четвертого и седьмого, пер15вого и четвертого, второго и шестого, четвертого и восьмого, первого и пятого, второго и седьмого, третьего и восьмого блоков задержки, при этом к первому, второму и третьему вхо20дам первого, второго, третьего и четвертого сумматоров подключены соответственно выходы первого, второго и третьегоI четвертого, пятого и шестого; седьмого, восьмого и девя25того; десятого, одиннсщцатогр и двенадцатого блоков вычисления модуля разности сигналов, выходы первого, второго, третьего и четвертого сумматоров подключены к соответствую30щим входам блока сравнения, первый.

второй, третий и четвертый выходы блока сравнения подключены к первым входам первого, второго, третьего и четвертого ключевых элементов соответственно а ко вторым входам первого, второго, третьего и четвертого ключевых элементов подключены соответственно выходы первого, второго, третьего и четвертого блоков задержки, причем вь-ходы четырех ключевых элементов соединены между собой.

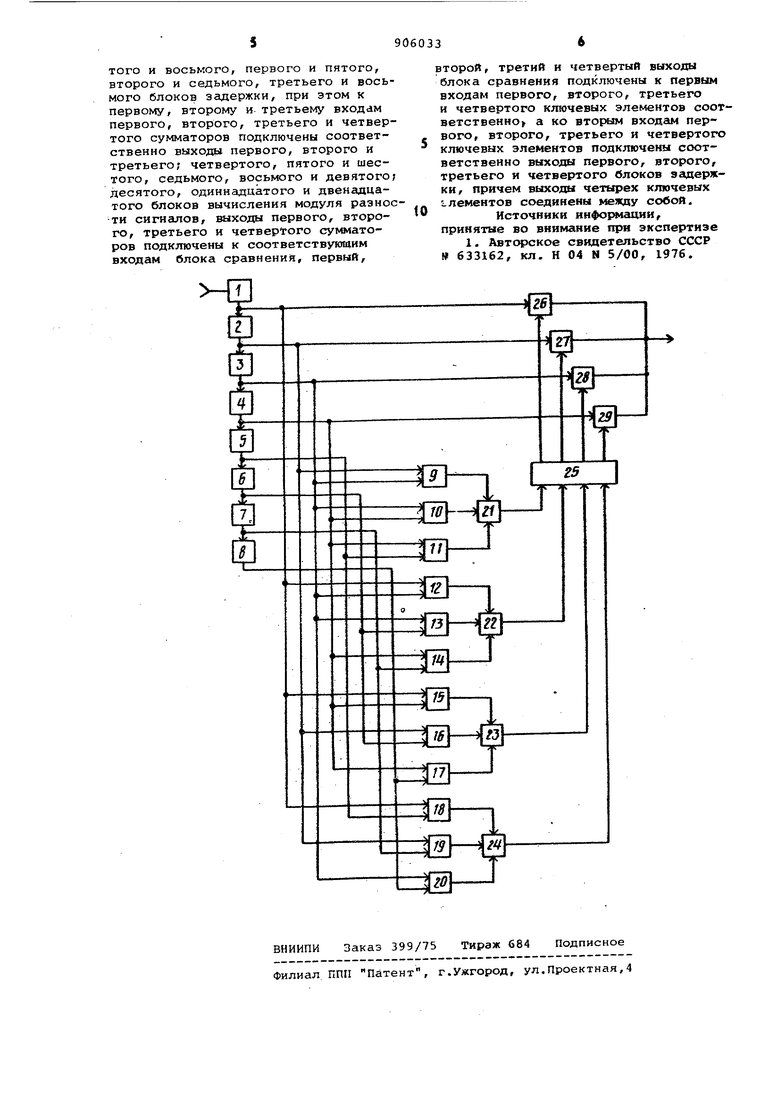

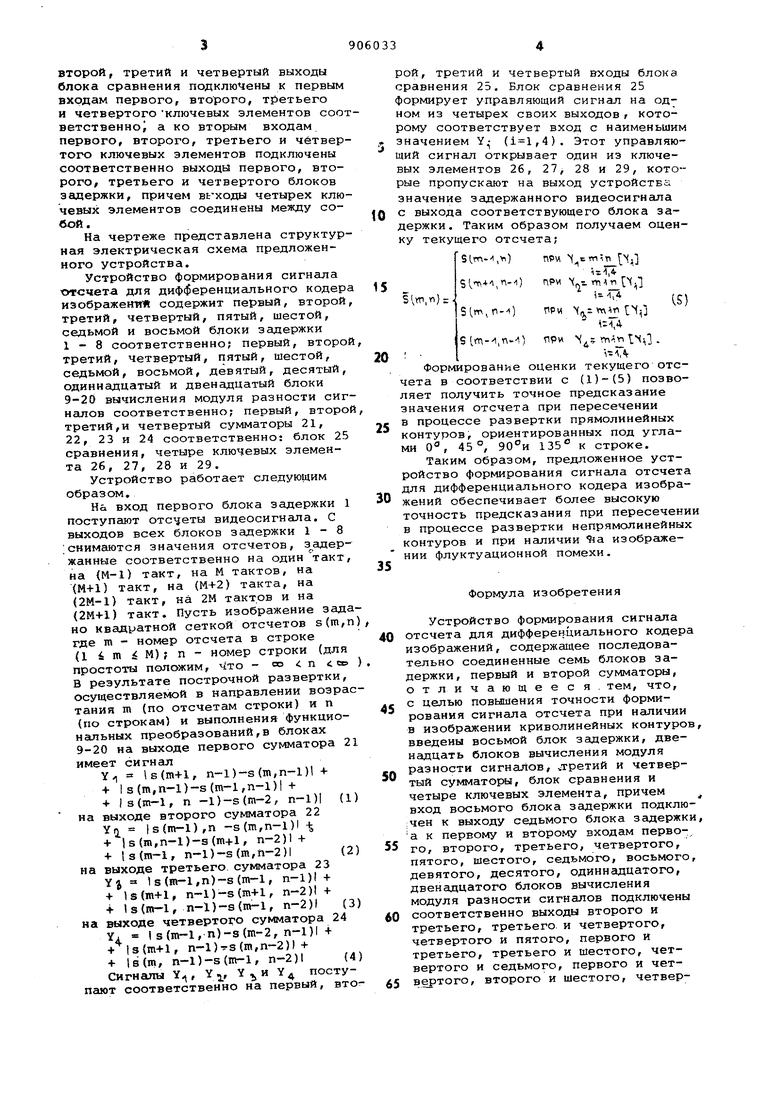

На чертеже представлена структурная электрическая схема предложенного устройства.

Устройство формирования сигнала ХУгсчета для дифференциального кодера изображенттЖ содержит первый, второй, третий, четвертый, пятый, шестой, седьмой и восьмой блоки задержки 1-8 соответственно; первый, второй третий. Четвертый, пятый, шестой, седьмой, восьмой, девятый, десятый, одиннадцатый и двенадцатый блоки 9-20 вычисления модуля разности сигналов соответственно; первый, второй третий,и четвертый сумматоры 21, 22, 23 и 24 соответственно: блок 25 сравнения, четыре ключевых элемента 26, 27, 28 и 29.

Устройство работает следующим образом.

На вход первого блока задержки 1 поступают отсчеты видеосигнала. С выходов всех блоков задержки 1-8 ;снимсиотся значения отсчетов, задержанные соответственно на один такт, на {М-1) такт, на М тактов, на М+1) такт, на (М+2) такта, на (2М-1) такт, на 2М тактов и на {2М4-1) такт. Пусть изображение задано квадратной сеткой отсчетов s(m,n) где тп - номер отсчета в строке (1 6т i М); п - номер строки (для простоты положим, что - «5 п 6 ее ) в результате построчной развертки, осуществляемой в направлении возрастания m (по отсчетам строки) и п (по строкам) и выполнения функциональных преобразований,в блоках 9-20 на выходе первого сумматора 21 имеет сигнал

Y., ls(m+l, n-l)-s (m,n-l)l + + 1 s(m,n-l)-s(m-l,n-l)l + + |s(m-l, n -l)-s(m-2, n-1) (1) на выходе второго сумматора 22 Yfj ls{m-l),n -s(m,n-l)l -I- ls(in,n-l)-s(in+l, n-2)l + + ls(m-l, n-l)-s(m,ii-2)l (2) на выходе третьего, сумматора 23 Yj 1s(m-l,n)-s(m-l, n-l)l + + is{m+l, n-l)-s(m+l, n-2)l + f ls(ro-l, n-l)-s(m-l, n-2)l (3) на выходе четвертого сумматора 24 Yi I s{m-l, n)-s(m-2, n-l)l + + ls(m+l, n-l)TS(m,n-2)l + 4- |s(m, n-l)-s(m-l, n-2)l (4) Сигналы Y, Y, Y , и Y поступают соответственно на первый, вто

рой, третий и четвертый входы блока сравнения 25. Блок сравнения 25 формирует управляющий сигнал на одном из четырех своих выходов , которому соответствует вход с наименьшим 2 значением Y,- (1 1,4). Этот управляющий сигнал открывает один из ключевых элементов 26, 27, 28 и 29, которые пропускают на выход устройства значение задержанного видеосигнала с выхода соответствующего блока задержки. Таким образом получаем оценку текущего отсчета;

,i)ПРМ mir

1гТл

5 ,-i) ПРИ

SIvW.nJEli -li (с

) ПРИ i1,4

Sim-l,n--l) nPVA Хд W.n tX;| .

A-A7t

Формирование оценки текущего отсчета в соответствии с (1)-(5) позволяет получить точное предсказание значения отсчета при пересечении в процессе развертки прямолинейных контуров, ориентированных под углами О , 45°, 90°и 135° к строке.

Таким образом, предложенное устройство формирования сигнала отсчета для дифференциального кодера изображений обеспечивает более высокую точность предсказания при пересечении в процессе развертки непрямолинейных контуров и при наличии а изображении флуктуационной помехи.

Формула изобретения

Устройство формирования сигнаша

отсчета для дифференциального кодера изображений, содержащее последовательно соединенные семь блоков задержки, первый и второй сумматоры, отличающееся, тем, что,

с целью повышения точности формирования сигнала отсчета при наличии в изображении криволинейных контуров, введены восьмой блок задержки, двенадцать блоков вычисления модуля разности сигналов, третий и четвертый сумматоры, блок сравнения и четыре ключевых элемента, причем вход восьмого блока задержки подклю;Чен к выходу седьмого блока задержки, а к первому и второму входам перво-,

го, второго, третьего, четвертого, пятого, шестого, седьмого, восьмого, девятого, десятого, одиннадцатого, двенадцатого блоков вычисления модуля разности сигналов подключены

соответственно выходы второго и третьего, третьего и четвертого, четвертого и пятого, первого и третьего, третьего и шестого, четвертого и седьмого, первого и четвертого, второго и шестого, четвер

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство формирования сигнала отсчета для дифференциального кодера изображений | 1989 |

|

SU1653178A1 |

| СПОСОБ ПРЕОБРАЗОВАНИЯ ЦИФРОВОГО СИГНАЛА ИЗОБРАЖЕНИЯ И УСТРОЙСТВО ДЛЯ ЕГО РЕАЛИЗАЦИИ | 2004 |

|

RU2287909C2 |

| Устройство для вычисления быстрого преобразования Фурье с основанием 3 | 1985 |

|

SU1302292A1 |

| АРИФМЕТИЧЕСКОЕ УСТРОЙСТВО ДЛЯ ВЫПОЛНЕНИЯ ДИСКРЕТНОГО ПРЕОБРАЗОВАНИЯ ФУРЬЕ | 1991 |

|

RU2015550C1 |

| Устройство формирования сигнала отсчета для дифференциального кодера изображений | 1976 |

|

SU633162A1 |

| Арифметическое устройство для процессора быстрого преобразования Фурье | 1981 |

|

SU1042028A1 |

| СПЛАЙН-ИНТЕРПОЛЯТОР | 1997 |

|

RU2116668C1 |

| Устройство для быстрого преобразования Уолша-Адамара | 1987 |

|

SU1443002A1 |

| Адаптивный эхокомпенсатор | 1989 |

|

SU1665520A1 |

| ДУПЛЕКСНЫЙ МОДЕМ | 1998 |

|

RU2147791C1 |

Авторы

Даты

1982-02-15—Публикация

1979-10-02—Подача